|

|

PDF BL24C512G Data sheet ( Hoja de datos )

| Número de pieza | BL24C512G | |

| Descripción | Two-wire Serial EEPROM | |

| Fabricantes | BELLING | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de BL24C512G (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

Shanghai Belling Corp., Ltd

Features

Two-Wire Serial Interface, I2CTM Compatible

– Bi-directional data transfer protocol

Wide-voltage Operation

– VCC = 1.7V to 5.5V

Speed: 400 KHz (1.7V) and 1 MHz (2.5V~5.5V)

Standby current (max.): 1 A, 1.7V

Operating current (max.): 2 mA, 1.7V

Hardware Data Protection

– Write Protect Pin

Sequential & Random Read Features

Memory organization: 65,536 x 8 bits

Description

The BL24C512G are EEPROM devices that use the

industrial standard 2-wire interface for communications. The

BL24C512G contains a memory array of 512K-bits

(65,536x8), which is organized in 128-byte per page.

The EEPROM can operate in a wide voltage range from

1.7V to 5.5V which fits most application. This product can

provide a low-power 2-wire EEPROM solution. The device

is offered in Lead-free, RoHS, halogen free or Green. The

available package types are 8-pin SOIC/SOP, TSSOP, DFN

and CSP.

The BL24C512G is compatible with the industrial standard

2-wire bus protocol. If in case the bus is not responded, a

new sent Op-code command will reset the bus and the

device will respond correctly. The simple bus consists of the

Serial Clock wire (SCL) and the Serial Data wire (SDA).

Utilizing such bus protocol, a Master device, such as a

microcontroller, can usually control one or more Slave

devices, alike this BL24C512G. The bit stream over the

SDA line includes a series of bytes, which identifies a

particular Slave device, an instruction, an address within

BL24C512G

Page Size: 128 bytes

Page write mode

– Up to 128 bytes per page write

Self timed write cycle with auto clear: 5ms (max.)

Filtered inputs for noise suppression

High-reliability

– Endurance: 1 million cycles

– Data retention: 100 years

Industrial temperature grades

Packages: SOIC/SOP, TSSOP, DFN and CSP

Lead-free, RoHS, Halogen free, Green

that Slave device, and a series of data, if appropriate. The

BL24C512G also has a Write Protect pin (WP) to allow

blocking any write operations over specified memory area.

Under no circumstance, the device will be hung up. In order

to refrain the state machine entering into a wrong state

during power-up sequence or a power toggle off-on

condition, a power on reset circuit is embedded. During

power-up, the device does not respond to any instructions

until the supply voltage (VCC) has reached an acceptable

stable level above the reset threshold voltage. Once VCC

passes the power on reset threshold, the device is reset

and enters into the Standby mode. This would also avoid

any inadvertent Write operations during power-up stage.

During power-down process, the device will enter into

standby mode, once VCC drops below the power on reset

threshold voltage. In addition, the device will be in standby

mode after receiving the Stop command, provided that no

internal write operation is in progress. Nevertheless, it is

illegal to send a command unless the VCC is within its

operating level.

1

1 page

Shanghai Belling Corp., Ltd

memory location. The BL24C512G acknowledges once

more and the Master generates the Stop condition, at which

time the device begins its internal programming cycle. While

this internal cycle is in progress, the device will not respond

to any request from the Master device.

Page Write

The BL24C512G is capable of 128-byte Page-Write

operation. A Page-Write is initiated in the same manner as a

Byte Write, but instead of terminating the internal Write

cycle after the first data word is transferred, the Master

device can transmit up to 127 more bytes. After the receipt

of each data word, the EEPROM responds immediately with

an ACK on SDA line, and the seven lower order data word

address bits are internally incremented by one, while the

higher order bits of the data word address remain constant.

If a byte address is incremented from the last byte of a page,

it returns to the first byte of that page. If the Master device

should transmit more than 128 bytes prior to issuing the

Stop condition, the address counter will “roll over,” and the

previously written data will be overwritten. Once all 128

bytes are received and the Stop condition has been sent by

the Master, the internal programming cycle begins. At this

point, all received data is written to the BL24C512G in a

single Write cycle. All inputs are disabled until completion of

the internal Write cycle.

Acknowledge (ACK) Polling

The disabling of the inputs can be used to take advantage

of the typical Write cycle time. Once the Stop condition is

issued to indicate the end of the host's Write operation, the

BL24C512G initiates the internal Write cycle. ACK polling

can be initiated immediately. This involves issuing the Start

condition followed by the Slave address for a Write

operation. If the EEPROM is still busy with the Write

operation, no ACK will be returned. If the BL24C512G has

completed the Write operation, an ACK will be returned and

the host can then proceed with the next Read or Write

operation.

Read Operation

Read operations are initiated in the same manner as Write

operations, except that the (R/W) bit of the Slave address is

set to “1”. There are three Read operation options: current

address read, random address read and sequential read.

BL24C512G

Current Address Read

The BL24C512G contains an internal address counter

which maintains the address of the last byte accessed,

incremented by one. For example, if the previous operation

is either a Read or Write operation addressed to the

address location n, the internal address counter would

increment to address location n+1. When the EEPROM

receives the Slave Addressing Byte with a Read operation

(R/W bit set to “1”), it will respond an ACK and transmit the

8-bit data byte stored at address location n+1. The Master

should not acknowledge the transfer but should generate a

Stop condition so the BL24C512G discontinues

transmission. If 'n' is the last byte of the memory, the data

from location '0' will be transmitted. (Refer to Figure 1-8.

Current Address Read Diagram.)

Random Address Read

Selective Read operations allow the Master device to select

at random any memory location for a Read operation. The

Master device first performs a 'dummy' Write operation by

sending the Start condition, Slave address and byte

address of the location it wishes to read. After the

BL24C512G acknowledges the byte address, the Master

device resends the Start condition and the Slave address,

this time with the R/W bit set to one. The EEPROM then

responds with its ACK and sends the data requested. The

Master device does not send an ACK but will generate a

Stop condition. (Refer to Figure 1-9. Random Address Read

Diagram.)

Sequential Read

Sequential Reads can be initiated as either a Current

Address Read or Random Address Read. After the

BL24C512G sends the initial byte sequence, the Master

device now responds with an ACK indicating it requires

additional data from the BL24C512G. The EEPROM

continues to output data for each ACK received. The Master

device terminates the sequential Read operation by pulling

SDA High (no ACK) indicating the last data word to be read,

followed by a Stop condition. The data output is sequential,

with the data from address n followed by the data from

address n+1,n+2 ... etc. The address counter increments by

one automatically, allowing the entire memory contents to

be serially read during sequential Read operation. When

the memory address boundary of the array is reached, the

5

5 Page

Shanghai Belling Corp., Ltd

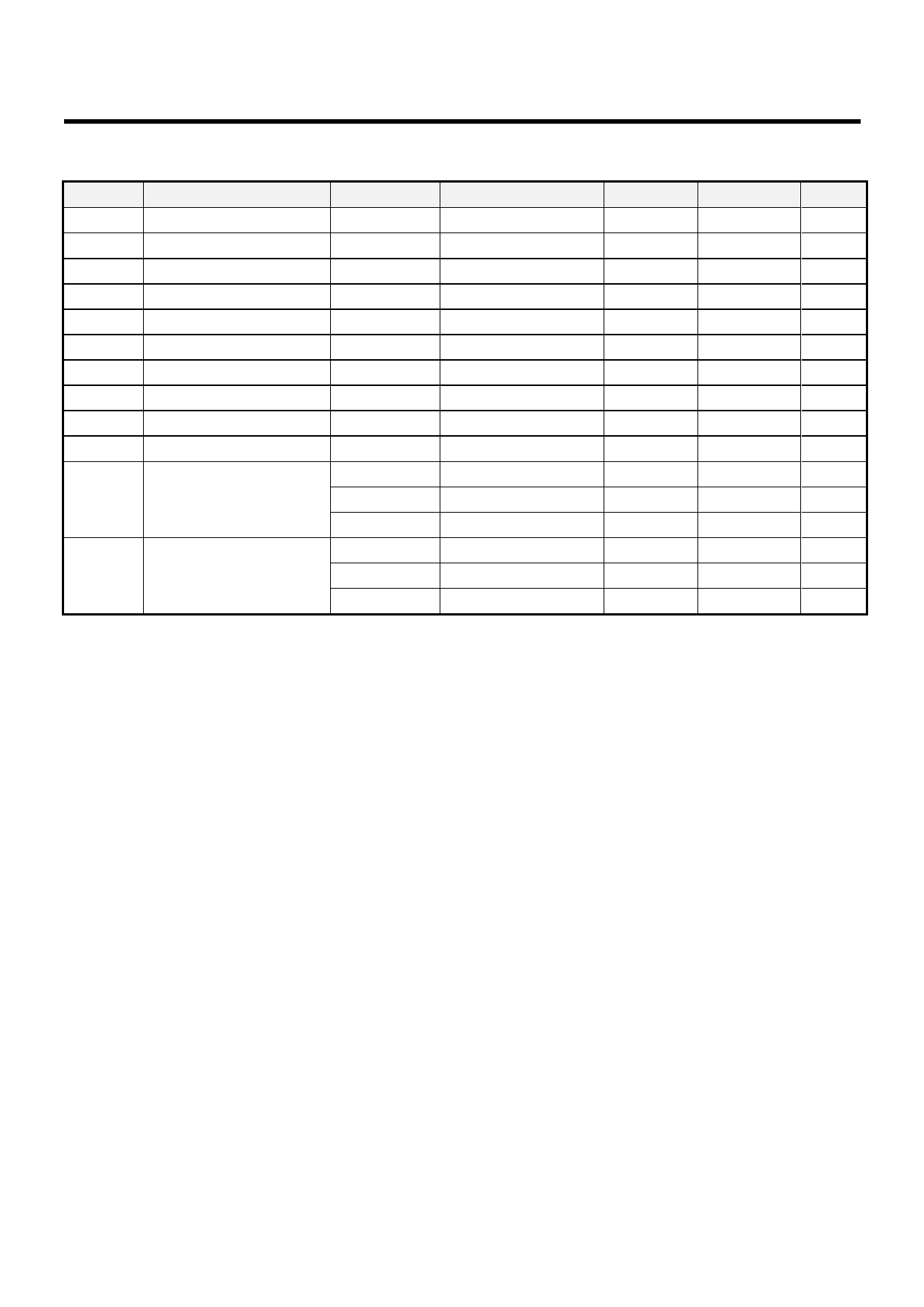

DC Electrical Characteristic

Industrial: TA = –40°C to +85°C, VCC = 1.7V ~ 5.5V

Symbol

Parameter[1]

VCC Test Conditions

VCC Supply Voltage

VIH Input High Voltage

VIL Input Low Voltage

ILI Input Leakage Current 5 V VIN = VCC max

ILO Output Leakage Current

5V

VOL1

Output Low Voltage

1.7V

IOL = 0.15 mA

VOL2

Output Low Voltage

3V IOL = 2.1 mA

ISB1 Standby Current

1.7V

VIN = VCC or GND

ISB2 Standby Current

2.5V

VIN = VCC or GND

ISB3 Standby Current

5V VIN = VCC or GND

1.7V

Read at 400 KHz

ICC1 Read Current

2.5V

5.5V

Read at 1 MHz

Read at 1 MHz

1.7V

Write at 400 KHz

ICC2 Write Current

2.5V

5.5V

Write at 1 MHz

Write at 1 MHz

Note: The parameters are characterized but not 100% tested.

Min.

1.7

0.7*VCC

-1

--

--

—

—

—

—

—

—

—

BL24C512G

Max.

5.5

VCC+1

0.3* VCC

2

2

0.2

0.4

1

2

3

0.5

1

1

2

3

3

Unit

V

V

V

μA

μA

V

V

μA

μA

μA

mA

mA

mA

mA

mA

mA

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet BL24C512G.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| BL24C512 | Two-wire Serial EEPROM | BELLING |

| BL24C512G | Two-wire Serial EEPROM | BELLING |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |