|

|

PDF W956K6HB Data sheet ( Hoja de datos )

| Número de pieza | W956K6HB | |

| Descripción | A/D MUX | |

| Fabricantes | Winbond | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W956K6HB (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

W956K6HB

32Mb Async./Burst/Sync./A/D MUX

TABLE OF CONTENTS

1. GENERAL DESCRIPTION .......................................................................................................... 3

2. FEATURES.................................................................................................................................. 3

3. ORDERING INFORMATION ....................................................................................................... 3

4. PIN CONFIGURATION................................................................................................................ 4

4.1 Ball Assignment .................................................................................................................................. 4

5. PIN DESCRIPTION ..................................................................................................................... 5

5.1 Signal Description............................................................................................................................... 5

6. BLOCK DIAGRAM ...................................................................................................................... 6

7. INSTRUCTION SET .................................................................................................................... 7

7.1 Bus Operation..................................................................................................................................... 7

8. FUNCTIONAL DESCRIPTION .................................................................................................... 8

8.1 Power Up Initialization ........................................................................................................................ 8

8.1.1 Power-Up Initialization Timing ................................................................................................................... 8

8.2 Bus Operating Modes ......................................................................................................................... 8

8.2.1 Asynchronous Modes ................................................................................................................................ 8

8.2.1.1 READ Operation (ADV# LOW)......................................................................................................................... 9

8.2.1.2 WRITE Operation (ADV# LOW) ....................................................................................................................... 9

8.2.2 Burst Mode Operation.............................................................................................................................. 10

8.2.2.1 Burst Mode READ (4-word burst)................................................................................................................... 10

8.2.2.2 Burst Mode WRITE (4-word burst) ................................................................................................................. 11

8.2.2.3 Refresh Collision During Variable-Latency READ Operation ......................................................................... 12

8.2.3 Mixed-Mode Operation ............................................................................................................................ 13

8.2.4 WAIT Operation ....................................................................................................................................... 13

8.2.4.1 Wired-OR WAIT Configuration ....................................................................................................................... 13

8.2.5 LB#/ UB# Operation................................................................................................................................. 14

8.3 Low Power Operation ....................................................................................................................... 14

8.3.1 Standby Mode Operation......................................................................................................................... 14

8.3.2 Temperature Compensated Refresh ....................................................................................................... 14

8.3.3 Partial-Array Refresh ............................................................................................................................... 14

8.3.4 Deep Power-Down Operation.................................................................................................................. 14

8.4 Registers........................................................................................................................................... 15

8.4.1 Access Using CRE .................................................................................................................................. 15

8.4.1.1 Configuration Register WRITE Asynchronous Mode Followed by READ Operation ...................................... 16

8.4.1.2 Configuration Register WRITE Synchronous Mode Followed by READ Operation........................................ 17

8.4.1.3 Register READ Asynchronous Mode Followed by READ ARRAY Operation ................................................. 18

8.4.1.4 Register READ Synchronous Mode Followed by READ ARRAY Operation................................................... 19

8.4.2 Software Access ...................................................................................................................................... 20

8.4.2.1 Load Configuration Register........................................................................................................................... 20

8.4.2.2 Read Configuration Register .......................................................................................................................... 21

8.4.3 Bus Configuration Register...................................................................................................................... 21

8.4.3.1 Bus Configuration Register Definition............................................................................................................. 22

8.4.3.2 Burst Length (BCR[2:0]) Default = Continuous Burst ..................................................................................... 23

8.4.3.3 Burst Wrap (BCR[3]) Default = No Wrap ........................................................................................................ 23

8.4.3.4 Sequence and Burst Length........................................................................................................................... 24

8.4.3.5 Drive Strength (BCR[5:4]) Default = Outputs Use Half-Drive Strength........................................................... 25

8.4.3.6 Table of Drive Strength................................................................................................................................... 25

8.4.3.7 WAIT Configuration. (BCR[8]) ........................................................................................................................ 25

8.4.3.8 WAIT Polarity (BCR[10])................................................................................................................................. 25

8.4.3.9 WAIT Configuration During Burst Operation................................................................................................... 26

8.4.3.10 Latency Counter (BCR[13:11]) Default = Three Clock Latency .................................................................... 26

8.4.3.11 Initial Access Latency (BRC[14]) Default = Variable ..................................................................................... 26

8.4.3.12 Allowed Latency Counter Settings in Variable Latency Mode....................................................................... 26

Publication Release Date: Nov. 07, 2014

Revision: A01-001

-1-

1 page

W956K6HB

5. PIN DESCRIPTION

5.1 Signal Description

Symbol

Type

Description

Address inputs: Inputs for addresses during READ and WRITE operations. Addresses are

A[max:16]

Input

internally latched during READ and WRITE cycles. The address lines are also used to define

the value to be loaded into the BCR or the RCR. A[max:16]=A[20:16] (32Mb)

Clock: Synchronizes the memory to the system operating frequency during synchronous

CLK

(Note 1)

Input

operations. When configured for synchronous operation, the address is latched on the first

rising CLK edge when ADV# is active. CLK must be static (HIGH or LOW) during

asynchronous access READ and WRITE operations when burst mode is enabled.

ADV#

(Note 1)

Input

Address valid: Indicates that a valid address is present on the address inputs. Addresses are

latched on the rising edge of ADV# during asynchronous READ and WRITE operations.

CRE

Input

Control register enable: When CRE is HIGH, WRITE operations load the RCR or BCR, and

READ operations access the RCR, BCR, or DIDR.

Chip enable: Activates the device when LOW. When CE# is HIGH, the device is disabled and

CE# Input

goes into standby mode.

OE#

Input

Output enable: Enables the output buffers when LOW. When OE# is HIGH, the output buffers

are disabled.

WE#

Input

Write enable: Determines if a given cycle is a WRITE cycle. If WE# is LOW, the cycle is a

WRITE to either a configuration register or to the memory array.

LB#

Input

Lower byte enable. DQ[7:0]

UB#

Input

Upper byte enable. DQ[15:8]

Address/data I/Os: These pins are a multiplexed address/data bus. As inputs for addresses,

A/DQ[15:0]

these pins behave as A[15:0]. A[0] is the LSB of the 16-bit word address within the

Input/Output

CellularRAM device. Address, RCR, and BCR values are loaded with ADV# LOW. Data is

input or output when ADV# is HIGH.

WAIT: Provides data-valid feedback during burst READ and WRITE operations. WAIT is used

WAIT

(Note 1)

Output

to arbitrate collisions between refresh and READ/WRITE operations. WAIT is also asserted at

the end of a row unless wrapping within the burst length. WAIT should be ignored during

asynchronous operations. WAIT is High-Z when CE# is HIGH.

NC — Reserved for future use.

VCC

VCCQ

Supply

Supply

Device power supply: (1.70V–1.95V) Power supply for device core operation.

I/O power supply: (1.70V–1.95V) Power supply for input/output buffers.

VSS

Supply

VSS must be connected to ground.

VSSQ

Supply

VSSQ must be connected to ground.

Note:

1. When using asynchronous mode exclusively, CLK can be tied to VSSQ or VCCQ. WAIT should be ignored during

asynchronous mode operations.

Publication Release Date: Nov. 07, 2014

Revision: A01-001

-5-

5 Page

W956K6HB

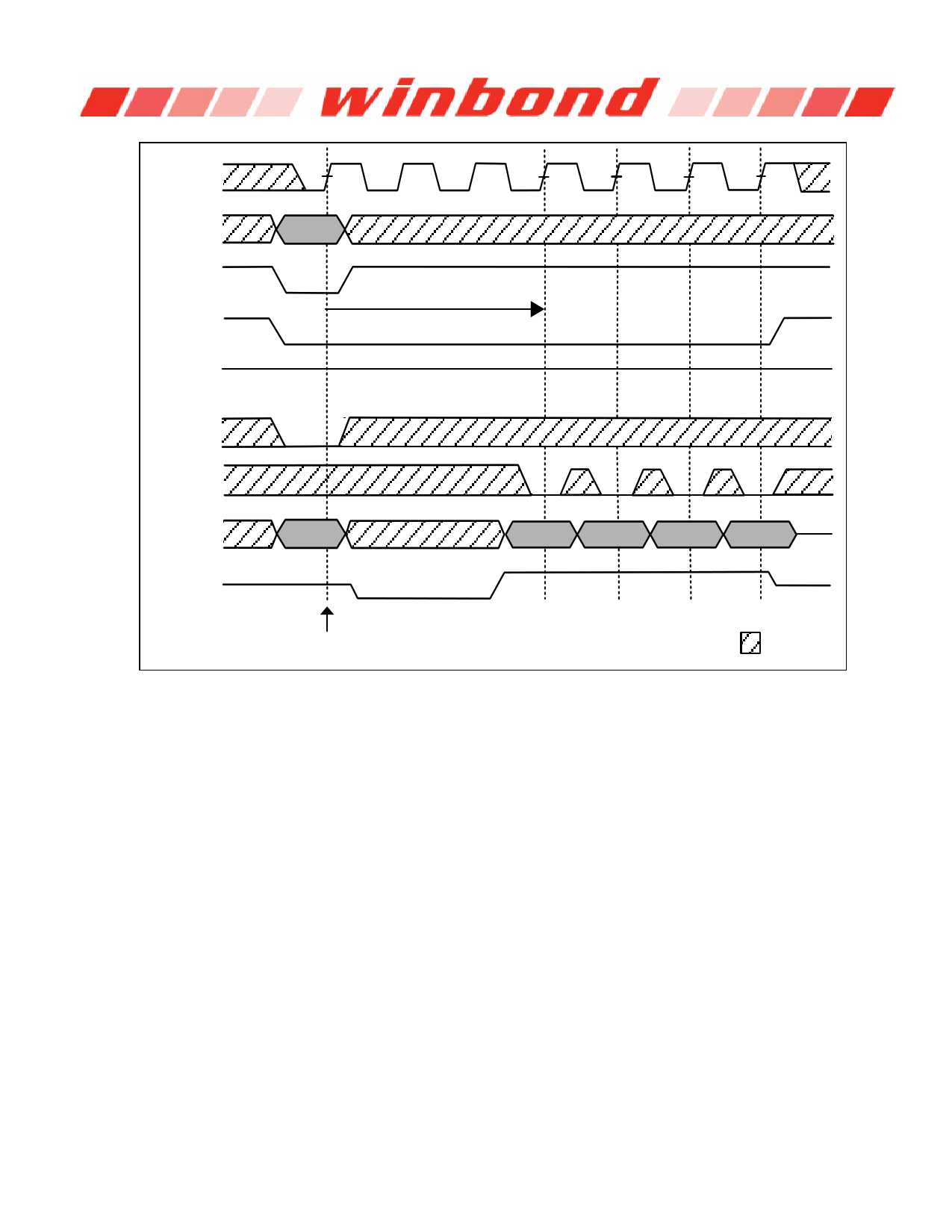

8.2.2.2 Burst Mode WRITE (4-word burst)

CLK

A[max:16]

ADV#

CE#

Valid

address

Latency Code 2(3 clocks)

OE#

WE#

LB#/UB#

A/DQ[15:0]

WAIT

Valid

address

D0 D1 D2 D3

WRITE burst identified

(WE#=LOW)

Don’t Care

Note:

Non-default BCR settings for burst mode WRITE (4-word burst) : fixed or variable latency , latency code 2(3 clocks) ,

WAIT active LOW , WAIT asserted during delay.

- 11 -

Publication Release Date: Nov. 07, 2014

Revision: A01-001

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet W956K6HB.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W956K6HB | A/D MUX | Winbond |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |