|

|

PDF R5F51137ADFP Data sheet ( Hoja de datos )

| Número de pieza | R5F51137ADFP | |

| Descripción | 32-Bit MCU | |

| Fabricantes | Renesas | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de R5F51137ADFP (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Cover

RX113 Group

32

User’s Manual: Hardware

RENESAS 32-Bit MCU

RX Family / RX100 Series

All information contained in these materials, including products and product specifications,

represents information on the product at the time of publication and is subject to change by

Renesas Electronics Corp. without notice. Please review the latest information published by

Renesas Electronics Corp. through various means, including the Renesas Electronics Corp.

website (http://www.renesas.com).

www.renesas.com

Rev.1.02 Dec 2014

1 page

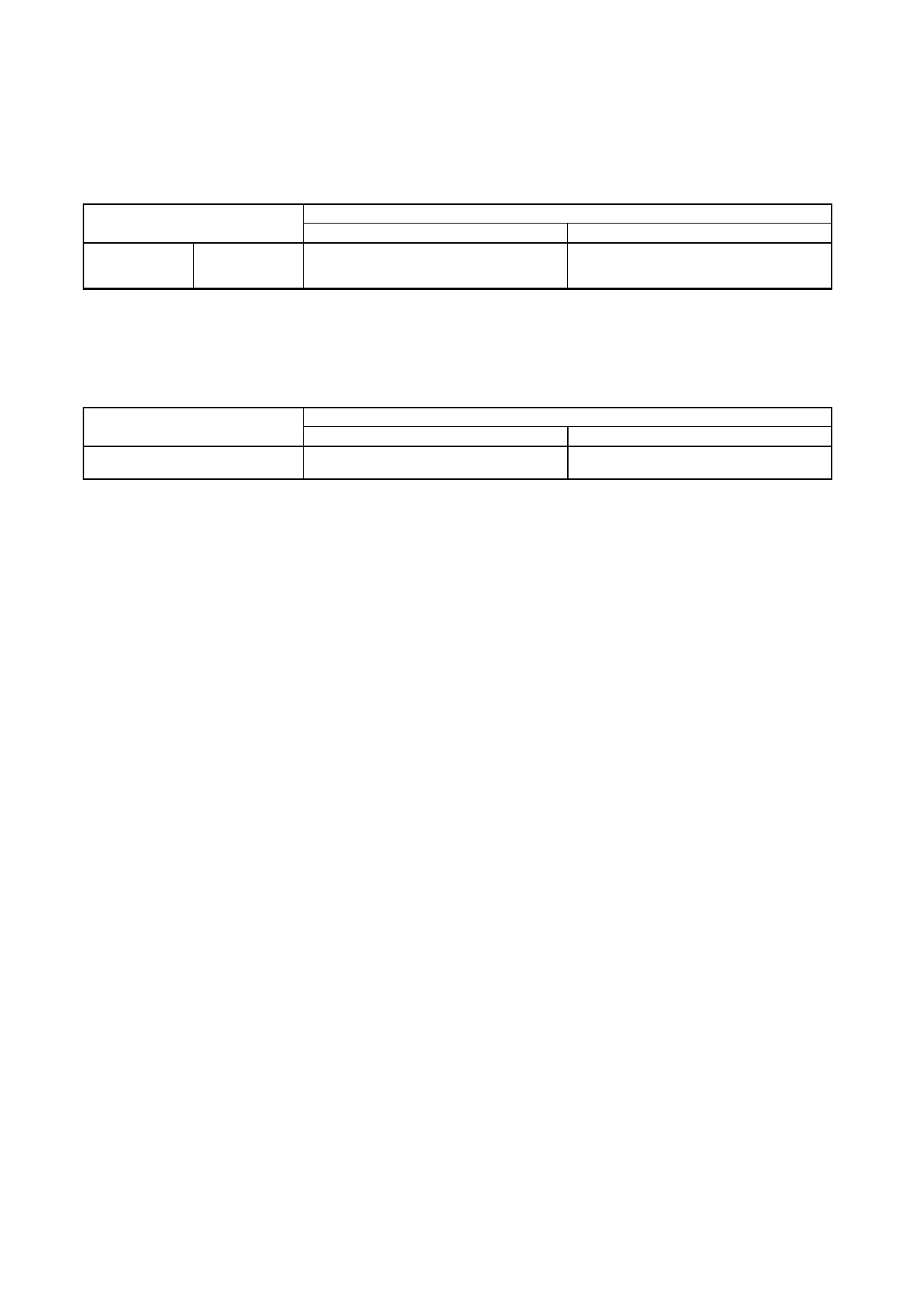

Specification Differences between Products

There are the following specification differences in these MCU products depending on the package.

Table 1 Specification Differences Depending on Packages

Chapter

9. Clock Generation 9.8.4 Notes on

Circuit

Sub-Clock

Specification Differences

Products with 40 pins or less

Products with 48 pins or more

Although sub-clock oscillator pins are not

At a cold start, initialize the sub-clock control

available, the sub-clock circuit must be initialized circuit regardless of whether the sub-clock is in

at a cold start.

use or not.

There are the following specification differences in these MCU products depending on the orderable part number.

Table 2 Specification Differences Depending on Orderable Part Numbers

Chapter

34. Capacitive Touch Sensing Unit

(CTSU)

Specification Differences

Orderable Number #3A, #2A

Orderable Number #30, #20

Supported

Not supported

5 Page

7.2.1

Option Function Select Register 0 (OFS0) ............................................................................... 137

7.2.2

Option Function Select Register 1 (OFS1) ............................................................................... 139

7.2.3

Endian Select Register (MDE) ................................................................................................. 141

7.3 Usage Note ........................................................................................................................................ 142

7.3.1

Setting Example of Option-Setting Memory ............................................................................ 142

8. Voltage Detection Circuit (LVDAa) ............................................................................................... 143

8.1 Overview ........................................................................................................................................... 143

8.2 Register Descriptions ......................................................................................................................... 146

8.2.1

Voltage Monitoring 1 Circuit Control Register 1 (LVD1CR1) ............................................... 146

8.2.2

Voltage Monitoring 1 Circuit Status Register (LVD1SR) ....................................................... 147

8.2.3

Voltage Monitoring 2 Circuit Control Register 1 (LVD2CR1) ............................................... 148

8.2.4

Voltage Monitoring 2 Circuit Status Register (LVD2SR) ....................................................... 149

8.2.5

Voltage Monitoring Circuit Control Register (LVCMPCR) .................................................... 150

8.2.6

Voltage Detection Level Select Register (LVDLVLR) ........................................................... 151

8.2.7

Voltage Monitoring 1 Circuit Control Register 0 (LVD1CR0) ............................................... 152

8.2.8

Voltage Monitoring 2 Circuit Control Register 0 (LVD2CR0) ............................................... 153

8.3 VCC Input Voltage Monitor .............................................................................................................. 154

8.3.1

Monitoring Vdet1 ..................................................................................................................... 154

8.3.2

Monitoring Vdet2 ..................................................................................................................... 154

8.4 Interrupt and Reset from Voltage Monitoring 1 ................................................................................ 155

8.5 Interrupt and Reset from Voltage Monitoring 2 ................................................................................ 157

8.6 Event Link Output ............................................................................................................................. 159

8.6.1

Interrupt Handling and Event Linking ...................................................................................... 159

9. Clock Generation Circuit .............................................................................................................. 160

9.1 Overview ........................................................................................................................................... 160

9.2 Register Descriptions ......................................................................................................................... 162

9.2.1

System Clock Control Register (SCKCR) ................................................................................ 162

9.2.2

System Clock Control Register 3 (SCKCR3) ........................................................................... 164

9.2.3

PLL Control Register (PLLCR) ............................................................................................... 165

9.2.4

PLL Control Register 2 (PLLCR2) .......................................................................................... 166

9.2.5

USB-dedicated PLL Control Register (UPLLCR) ................................................................... 167

9.2.6

USB-dedicated PLL Control Register 2 (UPLLCR2) .............................................................. 168

9.2.7

Main Clock Oscillator Control Register (MOSCCR) ............................................................... 169

9.2.8

Sub-Clock Oscillator Control Register (SOSCCR) .................................................................. 170

9.2.9

Low-Speed On-Chip Oscillator Control Register (LOCOCR) ................................................. 171

9.2.10 IWDT-Dedicated On-Chip Oscillator Control Register (ILOCOCR) ...................................... 172

9.2.11 High-Speed On-Chip Oscillator Control Register (HOCOCR) ............................................... 173

9.2.12 Oscillation Stabilization Flag Register (OSCOVFSR) ............................................................. 174

9.2.13 Oscillation Stop Detection Control Register (OSTDCR) ......................................................... 176

9.2.14 Oscillation Stop Detection Status Register (OSTDSR) ............................................................ 177

9.2.15 LCD Source Clock Control Register (LCDSCLKCR) ............................................................. 178

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet R5F51137ADFP.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| R5F51137ADFM | 32-Bit MCU | Renesas |

| R5F51137ADFP | 32-Bit MCU | Renesas |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |