|

|

PDF AT80C51RD2 Data sheet ( Hoja de datos )

| Número de pieza | AT80C51RD2 | |

| Descripción | 80C51 High Performance ROM 8-bit Microcontroller | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT80C51RD2 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Features

• 80C52 Compatible

– Four 8-bit I/O Ports

– Three 16-bit Timer/Counters

– 256 Bytes Scratch Pad RAM

– 8 Interrupt Sources with 4 Priority Levels

– Dual Data Pointer

• Variable Length MOVX for Slow RAM/Peripherals

• High-speed Architecture

– 10 to 40 MHz in Standard Mode

• 16K/32K Bytes On-Chip ROM Program

• AT80C51RD2 ROMless Versions

• On-Chip 1024 bytes Expanded RAM (XRAM)

– Software Selectable Size (0, 256, 512, 768, 1024 bytes)

– 256 Bytes Selected at Reset

• Keyboard Interrupt Interface on Port P1

• 8-bit Clock Prescaler

• 64K Program and Data Memory Spaces

• Improved X2 Mode with Independant Selection for CPU and Each Peripheral

• Programmable Counter Array 5 Channels with:

– High-speed Output

– Compare/Capture

– Pulse Width Modulator

– Watchdog Timer Capabilities

• Asynchronous Port Reset

• Full Duplex Enhanced UART

• Dedicated Baud Rate Generator for UART

• Low EMI (Inhibit ALE)

• Hardware Watchdog Timer (One-time Enabled with Reset-out)

• Power Control Modes

– Idle Mode

– Power-down Mode

– Power-off Flag

• Power Supply: 2.7V to 5.5V

• Temperature Ranges: Commercial (0 to +70°C) and Industrial (-40°C to +85°C)

• Packages: PDIL40, PLCC44, VQFP44

80C51 High

Performance

ROM 8-bit

Microcontroller

AT80C51RD2

1 page

AT80C51RD2

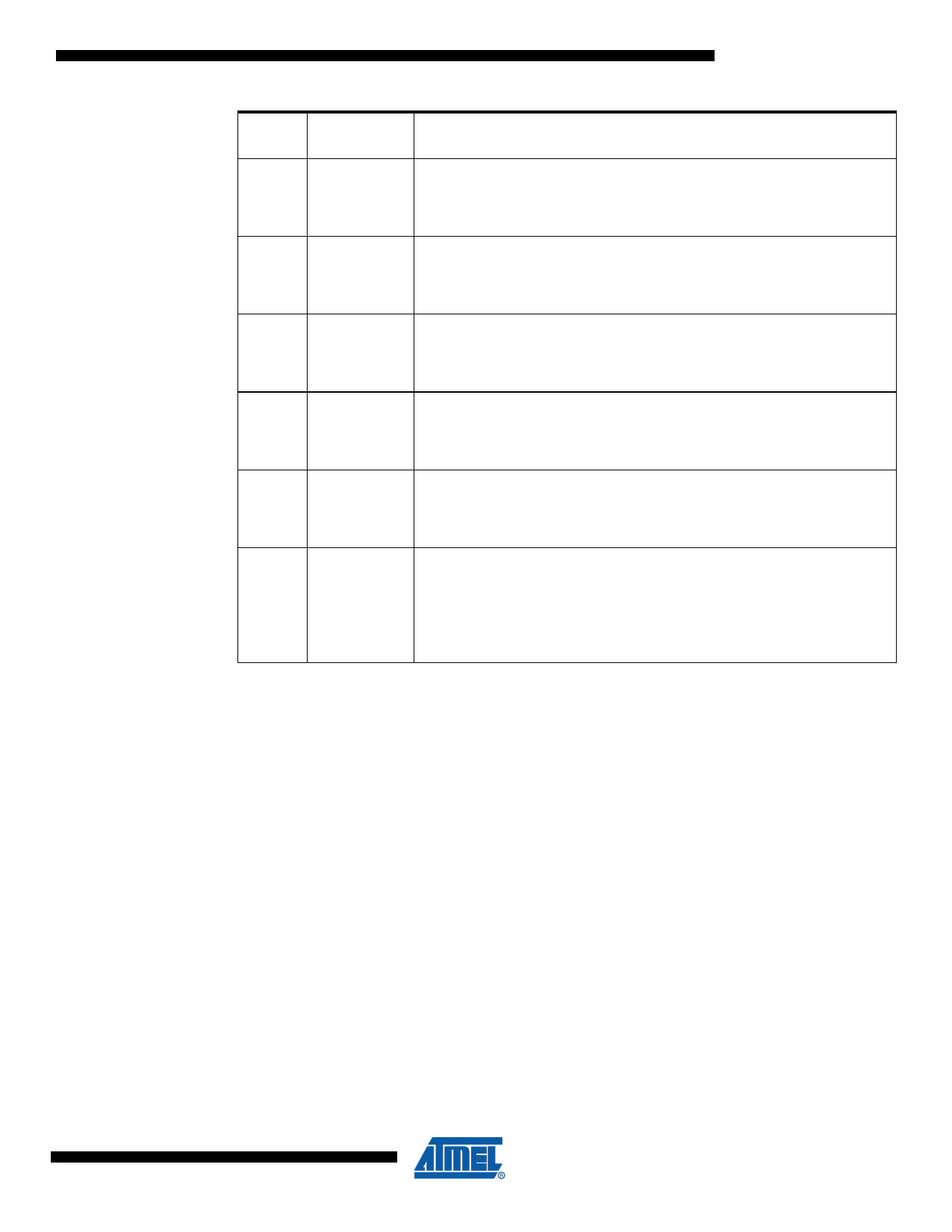

Table 3-1. Pin Description (Continued)

Mnemonic

P2.0 - P2.7

P3.0 - P3.7

RST

ALE/PROG

PSEN

EA

DIL

21 - 28

Pin Number

PLCC44 VQFP44 1.4

24 - 31

18 - 25

10 - 17

11,

13 - 19

5,

7 - 13

10 11

11 13

12 14

13 15

14 16

15 17

16 18

17 19

9 10

30 33

5

7

8

9

10

11

12

13

4

27

29 32

26

31 35

29

Type

I/O

I/O

I

O

I

I

I

I

O

O

I/O

O (I)

O

I

Name and Function

Port 2: Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins

that have 1s written to them are pulled high by the internal pull-ups and can be

used as inputs. As inputs, Port 2 pins that are externally pulled low will source

current because of the internal pull-ups. Port 2 emits the high-order address byte

during fetches from external program memory and during accesses to external

data memory that use 16-bit addresses (MOVX @DPTR). In this application, it

uses strong internal pull-ups emitting 1s. During accesses to external data memory

that use 8-bit addresses (MOVX @Ri), Port 2 emits the contents of the P2 SFR.

Some Port 2 pins receive the high order address bits during ROM reading and

verification:

P2.0 to P2.5 for 16 KB devices

P2.0 to P2.6 for 32 KB devices

Port 3: Port 3 is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins

that have 1s written to them are pulled high by the internal pull-ups and can be

used as inputs. As inputs, Port 3 pins that are externally pulled low will source

current because of the internal pull-ups. Port 3 also serves the special features of

the 80C51 family, as listed below.

RXD (P3.0): Serial input port

TXD (P3.1): Serial output port

INT0 (P3.2): External interrupt 0

INT1 (P3.3): External interrupt 1

T0 (P3.4): Timer 0 external input

T1 (P3.5): Timer 1 external input

WR (P3.6): External data memory write strobe

RD (P3.7): External data memory read strobe

Reset: A high on this pin for two machine cycles while the oscillator is running,

resets the device. An internal diffused resistor to VSS permits a power-on reset

using only an external capacitor to VCC. This pin is an output when the hardware

watchdog forces a system reset.

Address Latch Enable/Program Pulse: Output pulse for latching the low byte of

the address during an access to external memory. In normal operation, ALE is

emitted at a constant rate of 1/6 (1/3 in X2 mode) the oscillator frequency, and can

be used for external timing or clocking. Note that one ALE pulse is skipped during

each access to external data memory. This pin is also the program pulse input

(PROG) during Flash programming. ALE can be disabled by setting SFR’s AUXR.0

bit. With this bit set, ALE will be inactive during internal fetches.

Program Strobe Enable: The read strobe to external program memory. When

executing code from the external program memory, PSEN is activated twice each

machine cycle, except that two PSEN activations are skipped during each access

to external data memory. PSEN is not activated during fetches from internal

program memory.

External Access Enable: EA must be externally held low to enable the device to

fetch code from external program memory locations. If security level 1 is

programmed, EA will be internally latched on Reset.

4113D–8051–01/09

5

5 Page

AT80C51RD2

Bit

Number

Bit

Mnemonic

Description

Programmable Counter Array clock (This control bit is validated when the CPU

clock X2 is set; when X2 is low, this bit has no effect).

5

PCAX2

Cleared to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Enhanced UART clock (Mode 0 and 2) (This control bit is validated when the CPU

clock X2 is set; when X2 is low, this bit has no effect).

4

SIX2

Cleared to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer 2 clock (This control bit is validated when the CPU clock X2 is set; when X2 is

low, this bit has no effect).

3

T2X2

Cleared to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle.

Timer 1 clock (This control bit is validated when the CPU clock X2 is set; when X2 is

low, this bit has no effect).

2

T1X2

Cleared to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle

Timer 0 clock (This control bit is validated when the CPU clock X2 is set; when X2 is

low, this bit has no effect).

1

T0X2

Cleared to select 6 clock periods per peripheral clock cycle.

Set to select 12 clock periods per peripheral clock cycle

CPU clock

Cleared to select 12 clock periods per machine cycle (STD mode) for CPU and all the

peripherals.

0 X2

Set to select 6clock periods per machine cycle (X2 mode) and to enable the individual

peripherals "X2" bits.

Programmed by hardware after Power-up regarding Hardware Config Byte (HCB).

Reset Value = 0000 000’HCB.X2’b (see Hardware Config Byte)

Not bit addressable

4113D–8051–01/09

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AT80C51RD2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT80C51RD2 | 80C51 High Performance ROM 8-bit Microcontroller | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |