|

|

PDF HB8101Pk Data sheet ( Hoja de datos )

| Número de pieza | HB8101Pk | |

| Descripción | Remote controller | |

| Fabricantes | Cooperation Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HB8101Pk (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

浩博高科技

HB8101Pk Remote controller

Version

Date

V1.0.1

2013/01/23

S限te东东东 东东www密hbg限c密co高

Phone东东 东东86-东7技技-东866技64市市东

1 page

浩博高科技 ·

Shen Zhen Cooperation Technology Co., LTD.

Storage Temperature

TSTO

4.2 DC/AC Characteristics

-50 to 150

ºC

DC CHARACTERISTICS ( TA = 25 , VDD = 3V, unless otherwise noted )

PARAMETER

SYMBOL

TEST CONDITIONS

LIMIT

Min Typ

Operating voltage

VDD

- 1.8 -

Operating Current

VDD=3V , MCU run 2 MIPS

-

IOP1

0.45

Standby Current 1

ISTBY1

MCU stop, WDT off,

- 0.1

Standby Current 2

Input High Level

ISTBY2

VIH

MCU stop

All I/O port no loading

Key Scan option on

All I/O port

-

1.2

0.7*VDD

Input Low Level

VIL

All I/O port

- 0.4*VDD

Output Drive Current

IOH

VDD=3V , VOH=2.5V

-

All I/O port, except IROUT

Output Sink Current

IOL1

VDD=3V , VOL=0.5V

-

All I/O port, , except IROUT

IROUT PIN

IOL2 VDD=3V , VOL=0.3V -

Output Sink Current

Input Resistor

Rup

Pull up 150K ohm

135

LVR

VLVR

-7

20

210

150

1.5

SRAM Data Retention

voltage

VDR

1.4

Max

3.6

-

-

-

-

-

165

UNIT

V

mA

uA

uA

V

V

mA

mA

mA

K ohm

V

V

AC CHARACTERISTICS ( TA = 25 , VDD = 3V, unless otherwise noted )

PARAMETER

SYMBOL

TEST CONDITIONS

Min

LIMIT

Typ

Internal HRCOSC

Frequency

FOSC1

VDD = 1.8V~3.6V

Temp.= -20 ºC ~ 70 ºC

7.904

8 ± 1.2%

Max

8.096

UNIT

MHz

MCU

Operation

frequency

MCU

Operation

voltage

Internal LRCOSC

Frequency

FMCK

VOP

FLOSC

VDD=1.8V~3.6V

VDD=3V

2 ± 1.2%

MIPS

V

1.8 3.0 3.6

10KHz ± 50%

KHz

WDT period

TWDT

VDD=1.8V~3.6V

(2^20)/FMCK =0.262

Stable clock delay

after power on or

system reset

Stable clock delay

after wake up

CKstable1

CKstable2

( Note 1 )

System oscillator --HRCOSC

( Note 2 )

-

-

2318 x (1/ FMCK)

64 x (1/ FMCK)

Sec

us

us

Note1: The stable clock delay (CKstable1) is a delay between HRCOSC-started and 1st instruction-execution. This

delay will ensure stable system clock after power on or reset.

Note2: The stable clock delay (CKstable2) is a delay between HRCOSC-started and 1st instruction-execution of

wakeup. This delay will ensure stable system clock after wake up.

Note3: FMCK is MCU operating clock.

Page4/15

Jan. 2013

V1.0.1

5 Page

浩博高科技 ·

Shen Zhen Cooperation Technology Co., LTD.

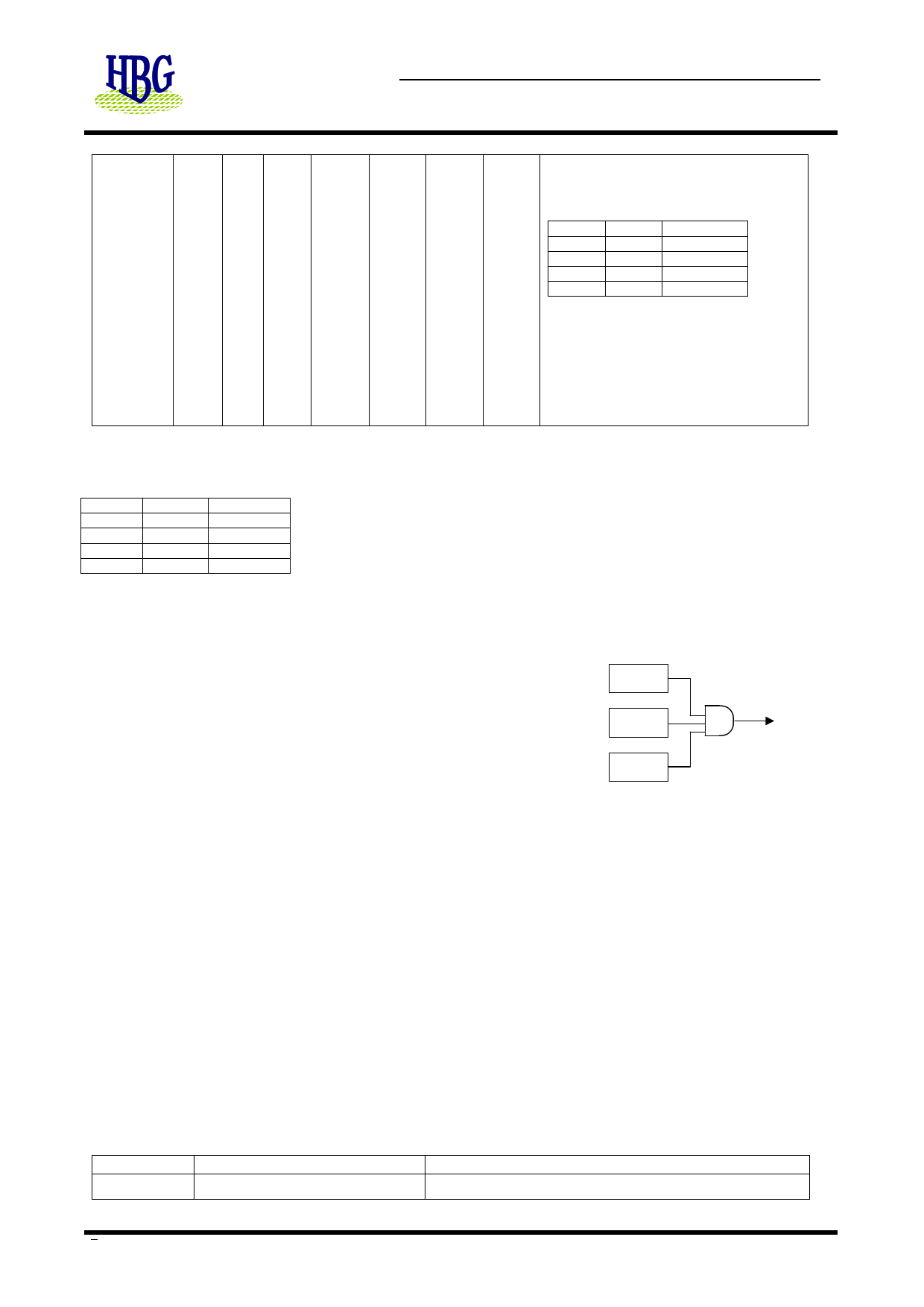

SCALER1 0EH

R/W

0000

TM1EN

TM1FG

T1DIV1

T1DIV0

T1DIV1~T1DIV0: The pre-scaler of

TIMER1

Timer 1 clock source definition table

FMCK = MCU operating clock

T1DIV1 T1DIV0 TM1CK

0 0 FMCK/8192

0 1 FMCK /4096

1 0 FMCK /2048

1 1 FMCK /1024

TM1FG: Timer 1 overflow flag

0: no overflow occurred.

1: overflow occurred, it can be cleared by

software.

TM1EN: Timer 1 enabled/disabled

0:Timer 1 disabled, the content of

Timer1 is cleared to all 00h.

1:Timer 1 enabled

The clock source of Timer 1 can come from the frequency divider, there are 4 kinds of clock rate selected by

register T1DIV1 and T1DIV0 in this divider, and the divider’s clock source is come from MCU operation clock.

TM1CK= Timer 1 clock source (FMCK = MCU operating clock)

T1DIV1 T1DIV0

TM1CK

0 0 FMCK /8192 The 8 bits content of Timer 1 can be reset to 00h by TMI1EN setting to 0, it will

0 1 FMCK /4096 be up count while Timer 1 clock source is rising after TIM1EN setting to 1. The

1

1

0

1

FMCK /2048

FMCK /1024

read operation sequence of TIM1.7~TIM1.0 must be follow low nibble (TIM1_L)

first and high nibble (TIM1_H) later. The Timer 1 will issue an overflow flag

( register TM1FG=1 ) when the content data of Timer 1 from FEh to FFh occurred, and Timer 1 will continue

counting from FFh, 00h, 01h… to FFh periodical repeat automatically.

5.6 Reset

Power on

reset ckt.

LVR

The actual system reset of this chip combines with three signals, which are

power on reset, low voltage reset (LVR) and WDT overflow reset. MCU will

go to NORMAL mode when system reset occurred.

WDT

5.7 Low Voltage Reset

SYSTEM

RESETB

When VDD power is applied to the chip, the low voltage reset circuit is enabled initially, it will be disabled when

in HALT mode. The internal system reset will be generated if VDD is lower than VLVR.

5.8 System Clock Oscillator

The HB8101Pk is provided an internal high speed RC oscillator (HRCOSC), this HRCOSC provided a

precision frequency deviation under ± 1.2% at VDD from 1.8V to 3.6V and temperature from -20 to

+70 .

Condition VDD=1.8V~3.6V

TYPE

OSC frequency

HRCOSC

8MHz ± 1.2%

MCU clock ( FMCK )

FHRCOSC /4 , MCU run 2 MIPS

Page10/15

Jan. 2013

V1.0.1

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet HB8101Pk.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HB8101Pk | Remote controller | Cooperation Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |