|

|

PDF XC9500XL Data sheet ( Hoja de datos )

| Número de pieza | XC9500XL | |

| Descripción | High-Performance CPLD | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XC9500XL (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

k

0

R XC9500XL High-Performance CPLD

Family Data Sheet

DS054 (v2.5) May 22, 2009

0 0 Product Specification

Features

• Optimized for high-performance 3.3V systems

- 5 ns pin-to-pin logic delays, with internal system

frequency up to 208 MHz

- Small footprint packages including VQFPs, TQFPs

and CSPs (Chip Scale Package)

- Pb-free available for all packages

- Lower power operation

- 5V tolerant I/O pins accept 5V, 3.3V, and 2.5V

signals

- 3.3V or 2.5V output capability

- Advanced 0.35 micron feature size CMOS

FastFLASH technology

• Advanced system features

- In-system programmable

- Superior pin-locking and routability with

FastCONNECT II switch matrix

- Extra wide 54-input Function Blocks

- Up to 90 product-terms per macrocell with

individual product-term allocation

- Local clock inversion with three global and one

product-term clocks

- Individual output enable per output pin with local

inversion

- Input hysteresis on all user and boundary-scan pin

inputs

- Bus-hold circuitry on all user pin inputs

- Supports hot-plugging capability

- Full IEEE Std 1149.1 boundary-scan (JTAG)

support on all devices

• Four pin-compatible device densities

- 36 to 288 macrocells, with 800 to 6400 usable

gates

• Fast concurrent programming

• Slew rate control on individual outputs

• Enhanced data security features

• Excellent quality and reliability

- 10,000 program/erase cycles endurance rating

- 20 year data retention

• Pin-compatible with 5V core XC9500 family in common

package footprints

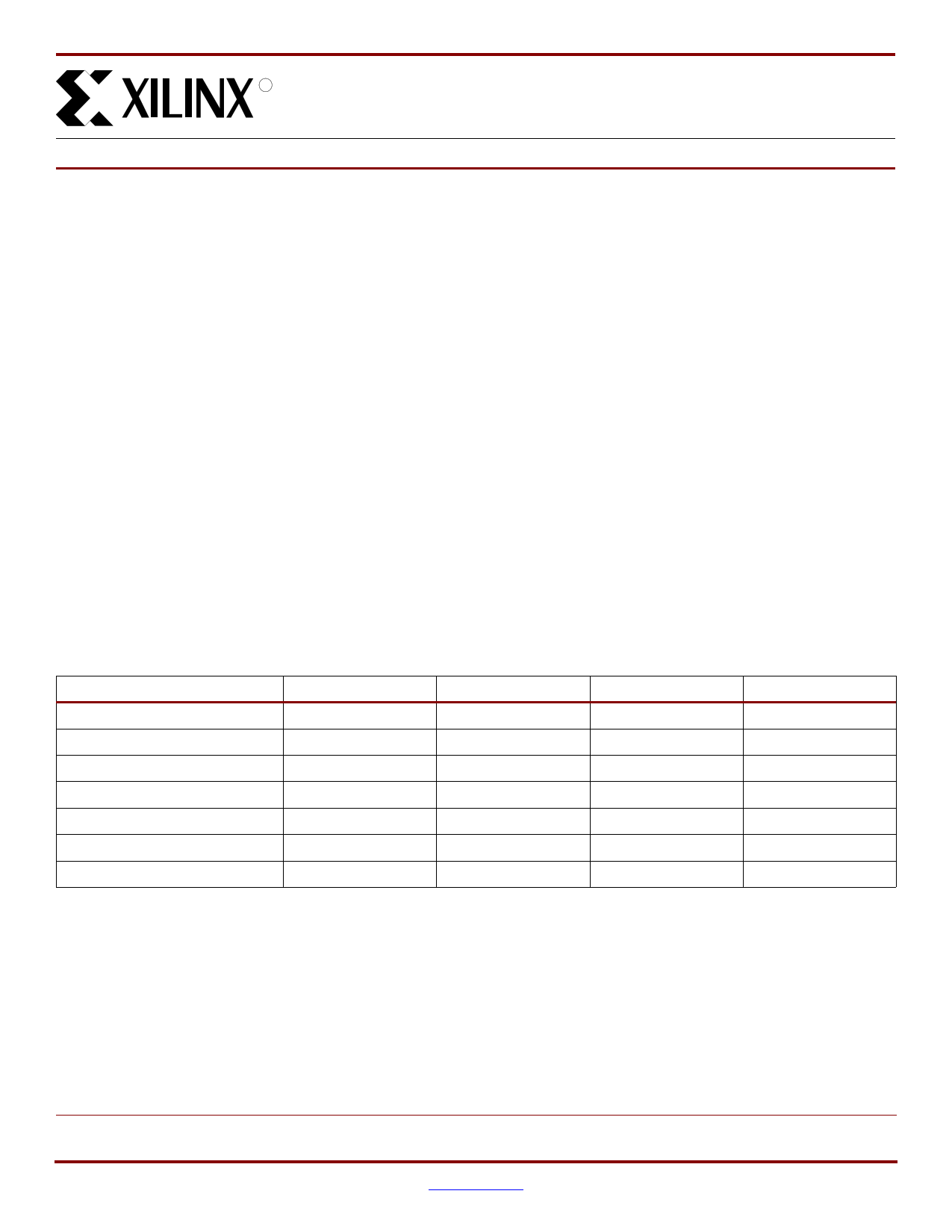

Table 1: XC9500XL Device Family

XC9536XL

XC9572XL

XC95144XL

XC95288XL

Macrocells

Usable Gates

36 72 144 288

800

1,600

3,200

6,400

Registers

TPD (ns)

TSU (ns)

TCO (ns)

fSYSTEM (MHz)

36 72 144 288

5556

3.7 3.7 3.7 4.0

3.5 3.5 3.5 3.8

178 178 178 208

© 1998–2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other

countries. All other trademarks are the property of their respective owners.

DS054 (v2.5) May 22, 2009

Product Specification

www.xilinx.com

1

1 page

R XC9500XL High-Performance CPLD Family Data Sheet

54 Global Global

Set/Reset Clocks

3

Additional

Product

Terms

(from other

macrocells)

Product Term Set

1

0

Product

Term

Allocator

Product Term Clock Enable

Product Term Clock

Product Term Reset

Product Term OE

S

D/T Q

CE

R

Additional

Product

Terms

(from other

macrocells)

Figure 3: XC9500XL Macrocell Within Function Block

All global control signals are available to each individual

macrocell, including clock, set/reset, and output enable sig-

nals. As shown in Figure 4, the macrocell register clock

originates from either of three global clocks or a product

term clock. Both true and complement polarities of the

selected clock source can be used within each macrocell. A

GSR input is also provided to allow user registers to be set

to a user-defined state.

To

FastCONNECTII

Switch Matrix

OUT

PTOE

To

I/O Blocks

DS054_03_042101

DS054 (v2.5) May 22, 2009

Product Specification

www.xilinx.com

5

5 Page

R XC9500XL High-Performance CPLD Family Data Sheet

I/O Block

The I/O Block (IOB) interfaces between the internal logic

and the device user I/O pins. Each IOB includes an input

buffer, output driver, output enable selection multiplexer,

and user programmable ground control. See Figure 10 for

details.

To other

Macrocells

I/O Block

To FastCONNECT

Switch Matrix

Macrocell

(Inversion in

AND-array)

Product Term OE

OUT

PTOE

I/O/GTS1

Global OE 1

Bus-Hold

I/O

1 User-

Programmable

Ground

0

Slew Rate

Control

I/O/GTS2

Global OE 2

I/O/GTS3

I/O/GTS4

Global OE 3

Global OE 4

Available in XC95144XL

and XC95288XL

Figure 10: I/O Block and Output Enable Capability

DS054_10_042101

The input buffer is compatible with 5V CMOS, 5V TTL, 3.3V

CMOS, and 2.5V CMOS signals. The input buffer uses the

internal 3.3V voltage supply (VCCINT) to ensure that the

input thresholds are constant and do not vary with the

VCCIO voltage. Each input buffer provides input hysteresis

(50 mV typical) to help reduce system noise for input signals

with slow rise or fall edges.

DS054 (v2.5) May 22, 2009

Product Specification

www.xilinx.com

11

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet XC9500XL.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XC9500XL | High-Performance CPLD | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |