|

|

PDF EN25Q128 Data sheet ( Hoja de datos )

| Número de pieza | EN25Q128 | |

| Descripción | 128 Megabit Serial Flash Memory | |

| Fabricantes | Eon Silicon Solution | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de EN25Q128 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

EN25Q128

EN25Q128

128 Megabit Serial Flash Memory with 4Kbyte Uniform Sector

FEATURES

• Single power supply operation

- Full voltage range: 2.7-3.6 volt

• Serial Interface Architecture

- SPI Compatible: Mode 0 and Mode 3

• 128 M-bit Serial Flash

- 128 M-bit/16,384 K-byte/65,536 pages

- 256 bytes per programmable page

• Standard, Dual or Quad SPI

- Standard SPI: CLK, CS#, DI, DO, WP#

- Dual SPI: CLK, CS#, DQ0, DQ1, WP#

- Quad SPI: CLK, CS#, DQ0, DQ1, DQ2, DQ3

• High performance

- 104MHz clock rate for Standard SPI

- 80MHz clock rate for two data bits

- 80MHz clock rate for four data bits

• Low power consumption

- 12 mA typical active current

- 1 μA typical power down current

• Uniform Sector Architecture:

- 4096 sectors of 4-Kbyte

- 256 blocks of 64-Kbyte

- Any sector or block can be erased individually

• Software and Hardware Write Protection:

- Write Protect all or portion of memory via

software

- Enable/Disable protection with WP# pin

• High performance program/erase speed

- Page program time: 0.8ms typical

- Sector erase time: 50ms typical

- Block erase time 200ms typical

- Chip erase time: 45 seconds typical

• Lockable 512 byte OTP security sector

• Minimum 100K endurance cycle

• Package Options

- 8 contact VDFN (5x6mm)

- 8 contact VDFN (6x8mm)

- 16 pins SOP 300mil body width

- 24 balls BGA (6x8mm)

- All Pb-free packages are RoHS compliant

• Industrial temperature Range

GENERAL DESCRIPTION

The EN25Q128 is a 128 Megabit (16,384K-byte) Serial Flash memory, with advanced write protection

mechanisms. The EN25Q128 supports the standard Serial Peripheral Interface (SPI), and a high

performance Dual output as well as Dual/Quad I/O using SPI pins: Serial Clock, Chip Select, Serial

DQ0(DI), DQ1(DO), DQ2(WP#) and DQ3(NC). SPI clock frequencies of up to 80MHz are supported

allowing equivalent clock rates of 160MHz (80MHz x 2) for Dual Output and 320MHz (80MHz x 4) for

Quad Output when using the Dual/Quad I/O Fast Read instructions. The memory can be programmed

1 to 256 bytes at a time, using the Page Program instruction.

The EN25Q128 is designed to allow either single Sector/Block at a time or full chip erase operation. The

EN25Q128 can be configured to protect part of the memory as the software protected mode. The

device can sustain a minimum of 100K program/erase cycles on each sector or block.

This Data Sheet may be revised by subsequent versions

or modifications due to changes in technical specifications.

1

©2004 Eon Silicon Solution, Inc.,

Rev. E, Issue Date: 2010/04/19

www.eonssi.com

1 page

Table 1. Pin Names

Symbol

CLK

DI (DQ0)

DO (DQ1)

CS#

WP# (DQ2)

NC(DQ3)

Vcc

Vss

NC

Pin Name

Serial Clock Input

Serial Data Input (Data Input Output 0) *1

Serial Data Output (Data Input Output 1) *1

Chip Enable

Write Protect (Data Input Output 2) *2

Not Connect (Data Input Output 3) *2

Supply Voltage (2.7-3.6V)

Ground

No Connect

Note:

1. DQ0 and DQ1 are used for Dual and Quad instructions.

2. DQ0 ~ DQ3 are used for Quad instructions.

EN25Q128

SIGNAL DESCRIPTION

Serial Data Input, Output and IOs (DI, DO and DQ0, DQ1, DQ2, DQ3)

The EN25Q128 support standard SPI, Dual SPI and Quad SPI operation. Standard SPI instructions

use the unidirectional DI (input) pin to serially write instructions, addresses or data to the device on the

rising edge of the Serial Clock (CLK) input pin. Standard SPI also uses the unidirectional DO (output) to

read data or status from the device on the falling edge CLK.

Dual and Quad SPI instruction use the bidirectional IO pins to serially write instruction, addresses or

data to the device on the rising edge of CLK and read data or status from the device on the falling edge

of CLK.

Serial Clock (CLK)

The SPI Serial Clock Input (CLK) pin provides the timing for serial input and output operations. ("See

SPI Mode")

Chip Select (CS#)

The SPI Chip Select (CS#) pin enables and disables device operation. When CS# is high the device is

deselected and the Serial Data Output (DO, or DQ0, DQ1, DQ2 and DQ3) pins are at high impedance.

When deselected, the devices power consumption will be at standby levels unless an internal erase,

program or status register cycle is in progress. When CS# is brought low the device will be selected,

power consumption will increase to active levels and instructions can be written to and data read from

the device. After power-up, CS# must transition from high to low before a new instruction will be

accepted.

Write Protect (WP#)

The Write Protect (WP#) pin can be used to prevent the Status Register from being written. Used in

conjunction with the Status Register’s Block Protect (BP0, BP1, BP2 and BP3) bits and Status Register

Protect (SRP) bits, a portion or the entire memory array can be hardware protected. The WP# function

is only available for standard SPI and Dual SPI operation, when during Quad SPI, this pin is the Serial

Data IO (DQ2) for Quad I/O operation.

This Data Sheet may be revised by subsequent versions

or modifications due to changes in technical specifications.

5

©2004 Eon Silicon Solution, Inc.,

Rev. E, Issue Date: 2010/04/19

www.eonssi.com

5 Page

OPERATING FEATURES

EN25Q128

Standard SPI Modes

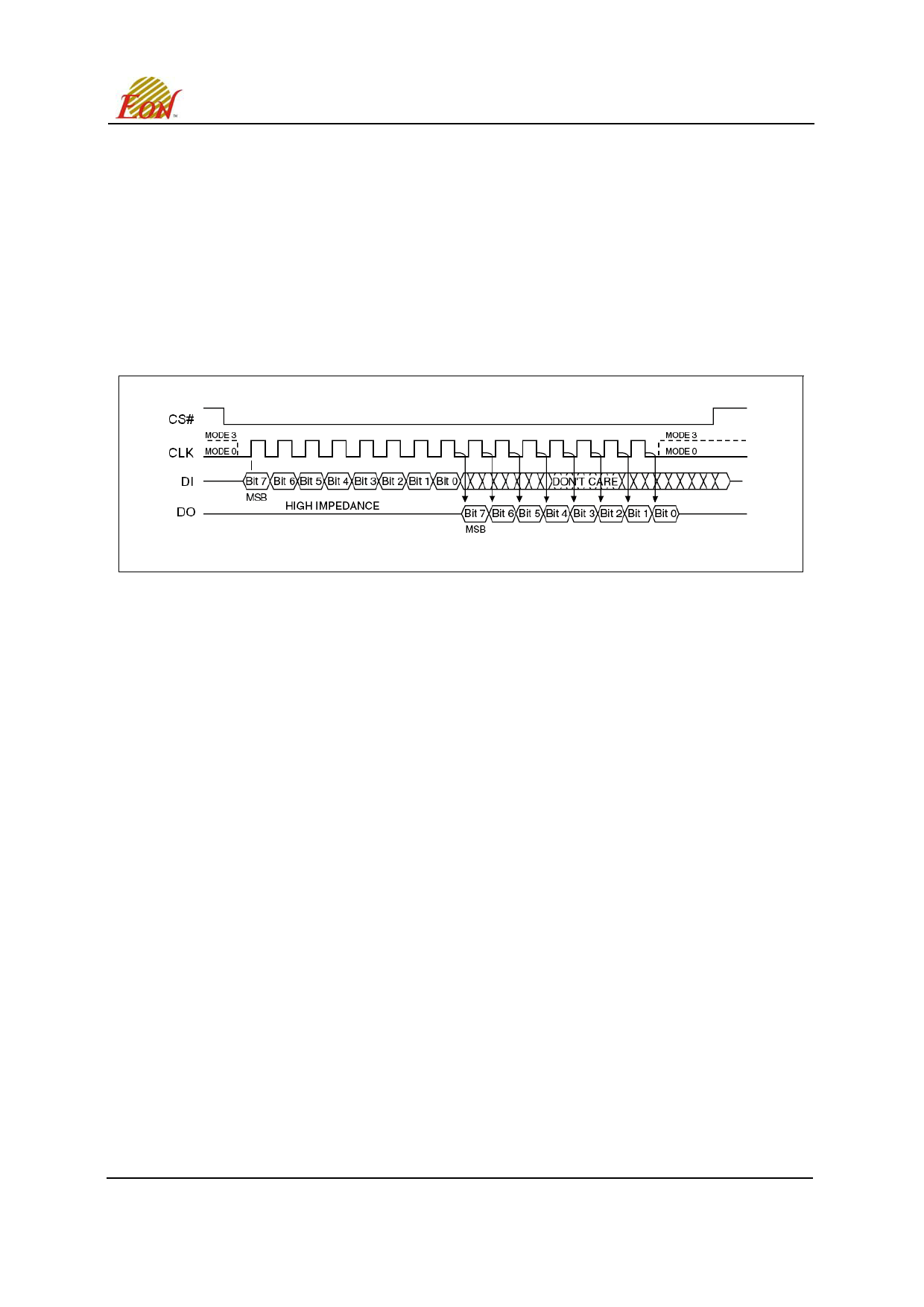

The EN25Q128 is accessed through a SPI compatible bus consisting of four signals: Serial Clock

(CLK), Chip Select (CS#), Serial Data Input (DI) and Serial Data Output (DO). Both SPI bus operation

Modes 0 (0,0) and 3 (1,1) are supported. The primary difference between Mode 0 and Mode 3, as

shown in Figure 3, concerns the normal state of the CLK signal when the SPI bus master is in standby

and data is not being transferred to the Serial Flash. For Mode 0 the CLK signal is normally low. For

Mode 3 the CLK signal is normally high. In either case data input on the DI pin is sampled on the rising

edge of the CLK. Data output on the DO pin is clocked out on the falling edge of CLK.

Figure 3. SPI Modes

Dual SPI Instruction

The EN25Q128 supports Dual SPI operation when using the “Dual Output Fast Read and Dual I/O

Fast Read “ (3Bh and BBh) instructions. These instructions allow data to be transferred to or from the

Serial Flash memory at two to three times the rate possible with the standard SPI. The Dual Read

instructions are ideal for quickly downloading code from Flash to RAM upon power-up (code-shadowing)

or for application that cache code-segments to RAM for execution. The Dual output feature simply

allows the SPI input pin to also serve as an output during this instruction. When using Dual SPI

instructions the DI and DO pins become bidirectional I/O pins; DQ0 and DQ1. All other operations use

the standard SPI interface with single output signal.

Quad SPI Instruction

The EN25Q128 supports Quad output operation when using the Quad I/O Fast Read (EBh).This

instruction allows data to be transferred to or from the Serial Flash memory at four to six times the rate

possible with the standard SPI. The Quad Read instruction offer a significant improvement in

continuous and random access transfer rates allowing fast code-shadowing to RAM or for application

that cache code-segments to RAM for execution. The EN25Q128 also supports full Quad Mode

function while using the Enable Quad I/O (EQIO) (38h). When using Quad SPI instruction the DI and

DO pins become bidirectional I/O pins; DQ0 and DQ1, and the WP# and NC pins become DQ2 and DQ3

respectively.

This Data Sheet may be revised by subsequent versions

or modifications due to changes in technical specifications.

11

©2004 Eon Silicon Solution, Inc.,

Rev. E, Issue Date: 2010/04/19

www.eonssi.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EN25Q128.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EN25Q128 | 128 Megabit Serial Flash Memory | Eon Silicon Solution |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |