|

|

PDF TC58NVG4S2FTA00 Data sheet ( Hoja de datos )

| Número de pieza | TC58NVG4S2FTA00 | |

| Descripción | 16 GBIT (2G x 8 BIT) CMOS NAND E2PROM | |

| Fabricantes | Toshiba | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TC58NVG4S2FTA00 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

TOSHIBA CONFIDENTIAL TC58NVG4S2FTA00

TENTATIVE TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

16 GBIT (2G × 8 BIT) CMOS NAND E2PROM

DESCRIPTION

The TC58NVG4S2F is a single 3.3V 16 Gbit (18,621,267,968 bits) NAND Electrically Erasable and

Programmable Read-Only Memory (NAND E2PROM) organized as (8192 + 576) bytes × 64 pages × 4148blocks.

The device has two 8768-byte static registers which allow program and read data to be transferred between the

register and the memory cell array in 8768-byte increments. The Erase operation is implemented in a single block

unit (512 Kbytes + 36 Kbytes: 8768 bytes × 64 pages).

The TC58NVG4S2F is a serial-type memory device which utilizes the I/O pins for both address and data

input/output as well as for command inputs. The Erase and Program operations are automatically executed making

the device most suitable for applications such as solid-state file storage, voice recording, image file memory for still

cameras and other systems which require high-density non-volatile memory data storage.

FEATURES

• Organization

Memory cell array

Register

Page size

Block size

x8

8768 × 259.25K × 8

8768 × 8

8768 bytes

(512K + 36K) bytes

• Modes

Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Page Copy,

Multi Page Program, Multi Block Erase, Multi Page Copy, Multi Page Read

• Mode control

Serial input/output

Command control

• Number of valid blocks

Min 4016 blocks

Max 4148 blocks

• Power supply

VCC = 2.7V to 3.6V

• Access time

Cell array to register TBD µs max

Serial Read Cycle

25 ns min (CL=50pF)

• Program/Erase time

Auto Page Program

Auto Block Erase

TBD µs/page typ.

TBD ms/block typ.

• Operating current

Read (25 ns cycle)

Program (avg.)

Erase (avg.)

Standby

30 mA max.

30 mA max

30 mA max

50 µA max

• Package

TSOP I 48-P-1220-0.50 (Weight: 0.53 g typ.)

• TBD bit ECC for each 512Byte is required.

1 2009-10-02C

1 page

TOSHIBA CONFIDENTIAL TC58NVG4S2FTA00

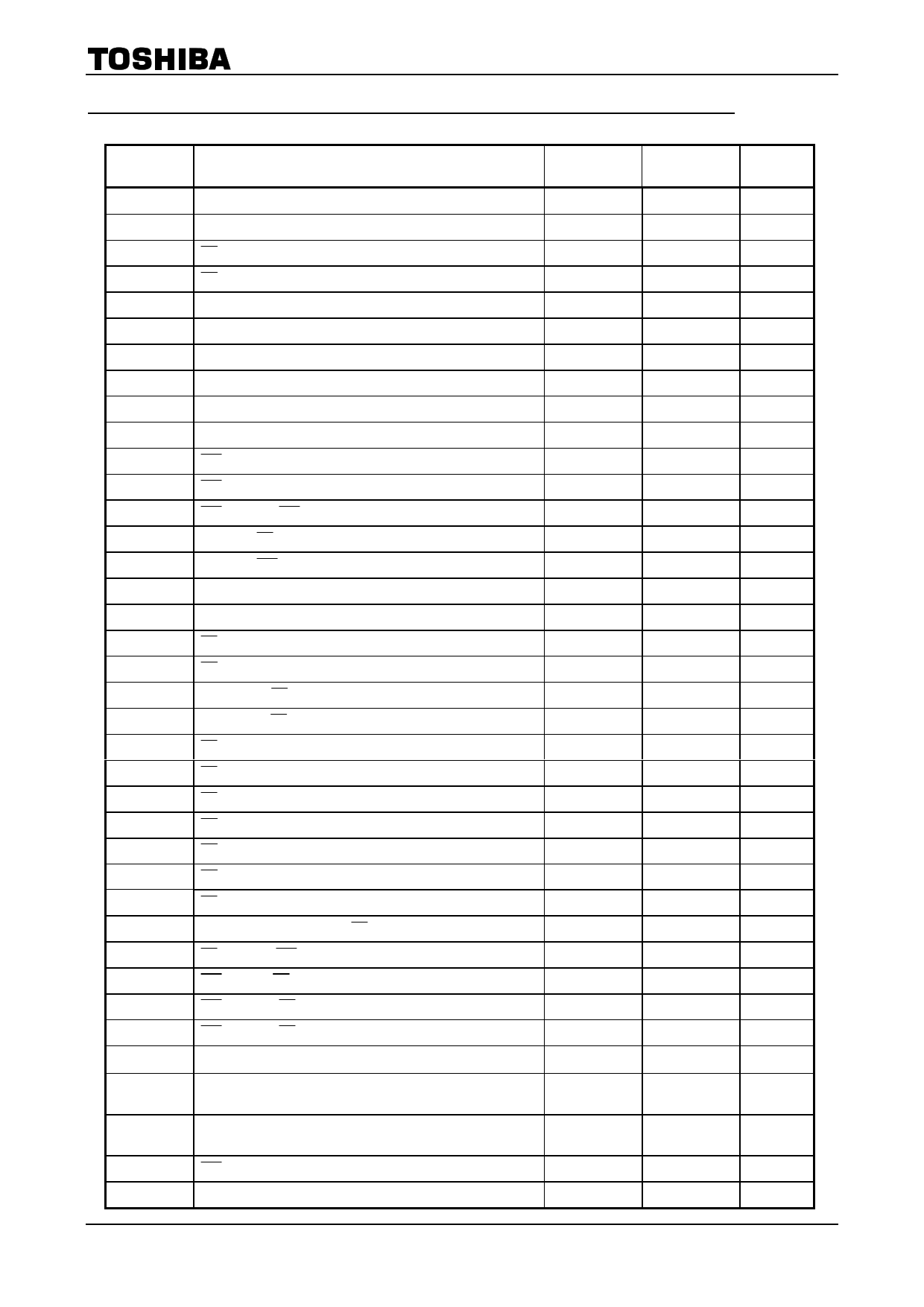

AC CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS

(Ta = 0 to 70 , VCC = 2.7 to 3.6V)

SYMBOL

PARAMETER

tCLS

tCLH

tCS

tCH

tWP

tALS

tALH

tDS

tDH

tWC

tWH

tWHW

tWW

tRR

tRW

tRP

tRC

tREA

tCEA

tCLR

tAR

tRHOH

tRLOH

tRHZ

tCOH

tCHZ

tCSD

tREH

tIR

tRHW

tWHC

tWHR

tWHR2

tR

CLE Setup Time

CLE Hold Time

CE Setup Time

CE Hold Time

Write Pulse Width

ALE Setup Time

ALE Hold Time

Data Setup Time

Data Hold Time

Write Cycle Time

WE High Hold Time

WE High Hold Time from final address to first data

WP High to WE Low

Ready to RE Falling Edge

Ready to WE Falling Edge

Read Pulse Width

Read Cycle Time

RE Access Time

CE Access Time

CLE Low to RE Low

ALE Low to RE Low

RE High to Output Hold Time

RE Low to Output Hold Time

RE High to Output High Impedance

CE High to Output Hold Time

CE High to Output High Impedance

CE High to ALE or CLE Don’t Care

RE High Hold Time

Output-High-impedance-to- RE Falling Edge

RE High to WE Low

WE High to CE Low

WE High to RE Low (Status Read)

WE High to RE Low (Column Address Change in Read)

Memory Cell Array to Starting Address

tDCBSYR1

Data Cache Busy in Read Cache (following 31h and 3Fh)

MIN

15

5

20

5

12

15

5

12

5

25

10

300

100

20

20

12

25

⎯

⎯

10

10

25

5

⎯

15

⎯

0

10

0

30

30

180

300

⎯

⎯

MAX

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

⎯

20

25

⎯

⎯

⎯

⎯

60

⎯

30

⎯

⎯

⎯

⎯

⎯

⎯

⎯

TBD

TBD

UNIT

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

µs

µs

tDCBSYR2

tWB

tRST

Data Cache Busy in Page Copy (following 3Ah)

WE High to Busy

Device Reset Time (Ready/Read/Program/Erase)

5

⎯

TBD

µs

⎯ 100 ns

⎯

10/10/30/500

µs

2009-10-02C

5 Page

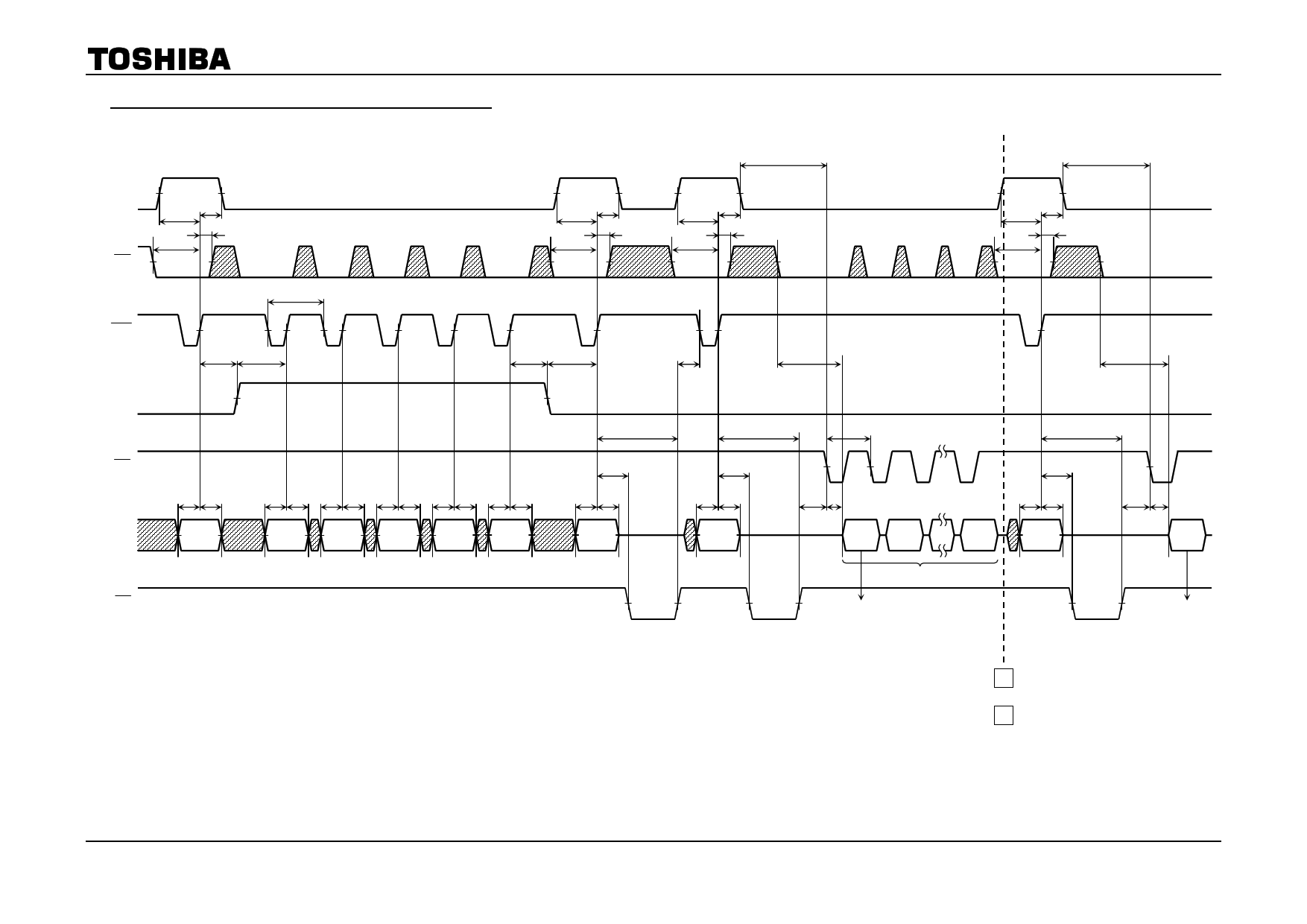

Read Cycle with Data Cache Timing Diagram (1/2)

TOSHIBA CONFIDENTIAL TC58NVG4S2FTA00

CLE

CE

tCLS tCLH

tCH

tCS

tWC

WE

tALH tALS

tCLS tCLH

tCH

tCS

tCLR

tCLS tCLH

tCH

tCS

tALH tALS

tRW tCEA

tCLR

tCLS tCLH

tCH

tCS

tCEA

ALE

RE

I/O

RY / BY

tDS tDH

00h

tDS tDH tDS tDH tDS tDH tDS tDH tDS tDH

CA0 CA8

to 7 to 13

Column address

N*

PA0 PA8 PA16

to 7 to 15 to 18

Page address

M

tR

tWB

tDS tDH

30h

tDCBSYR1

tRC

tDCBSYR1

tWB

tDS tDH

31h

tRR tREA

DOUT DOUT

01

tWB

tDS tDH

DOUT

31h

Page address M

Col. Add. 0

tRR tREA

DOUT

0

Page address

M+1

Col. Add. 0

* The column address will be reset to 0 by the 31h command input.

1

Continues to 1 of next page

11 2009-10-02C

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet TC58NVG4S2FTA00.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TC58NVG4S2FTA00 | 16 GBIT (2G x 8 BIT) CMOS NAND E2PROM | Toshiba |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |