|

|

PDF GAL18V10 Data sheet ( Hoja de datos )

| Número de pieza | GAL18V10 | |

| Descripción | High Performance E2CMOS PLD Generic Array Logic | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de GAL18V10 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

GAL18V10

High Performance E2CMOS PLD

Generic Array Logic™

Features

• HIGH PERFORMANCE E2CMOS® TECHNOLOGY

— 7.5 ns Maximum Propagation Delay

— Fmax = 111 MHz

— 5.5 ns Maximum from Clock Input to Data Output

— TTL Compatible 16 mA Outputs

— UltraMOS® Advanced CMOS Technology

• LOW POWER CMOS

— 75 mA Typical Icc

• ACTIVE PULL-UPS ON ALL PINS

• E2 CELL TECHNOLOGY

— Reconfigurable Logic

— Reprogrammable Cells

— 100% Tested/100% Yields

— High Speed Electrical Erasure (<100ms)

— 20 Year Data Retention

• TEN OUTPUT LOGIC MACROCELLS

— Uses Standard 22V10 Macrocell Architecture

— Maximum Flexibility for Complex Logic Designs

• PRELOAD AND POWER-ON RESET OF REGISTERS

— 100% Functional Testability

• APPLICATIONS INCLUDE:

— DMA Control

— State Machine Control

— High Speed Graphics Processing

— Standard Logic Speed Upgrade

• ELECTRONIC SIGNATURE FOR IDENTIFICATION

Description

The GAL18V10, at 7.5 ns maximum propagation delay time, com-

bines a high performance CMOS process with Electrically Eras-

able (E2) floating gate technology to provide a very flexible 20-pin

PLD. CMOS circuitry allows the GAL18V10 to consume much less

power when compared to its bipolar counterparts. The E2 technol-

ogy offers high speed (<100ms) erase times, providing the ability

to reprogram or reconfigure the device quickly and efficiently.

By building on the popular 22V10 architecture, the GAL18V10

eliminates the learning curve usually associated with using a new

device architecture. The generic architecture provides maximum

design flexibility by allowing the Output Logic Macrocell (OLMC)

to be configured by the user. The GAL18V10 OLMC is fully com-

patible with the OLMC in standard bipolar and CMOS 22V10 de-

vices.

Unique test circuitry and reprogrammable cells allow complete AC,

DC, and functional testing during manufacture. As a result, Lattice

Semiconductor delivers 100% field programmability and function-

ality of all GAL products. In addition, 100 erase/write cycles and

data retention in excess of 20 years are specified.

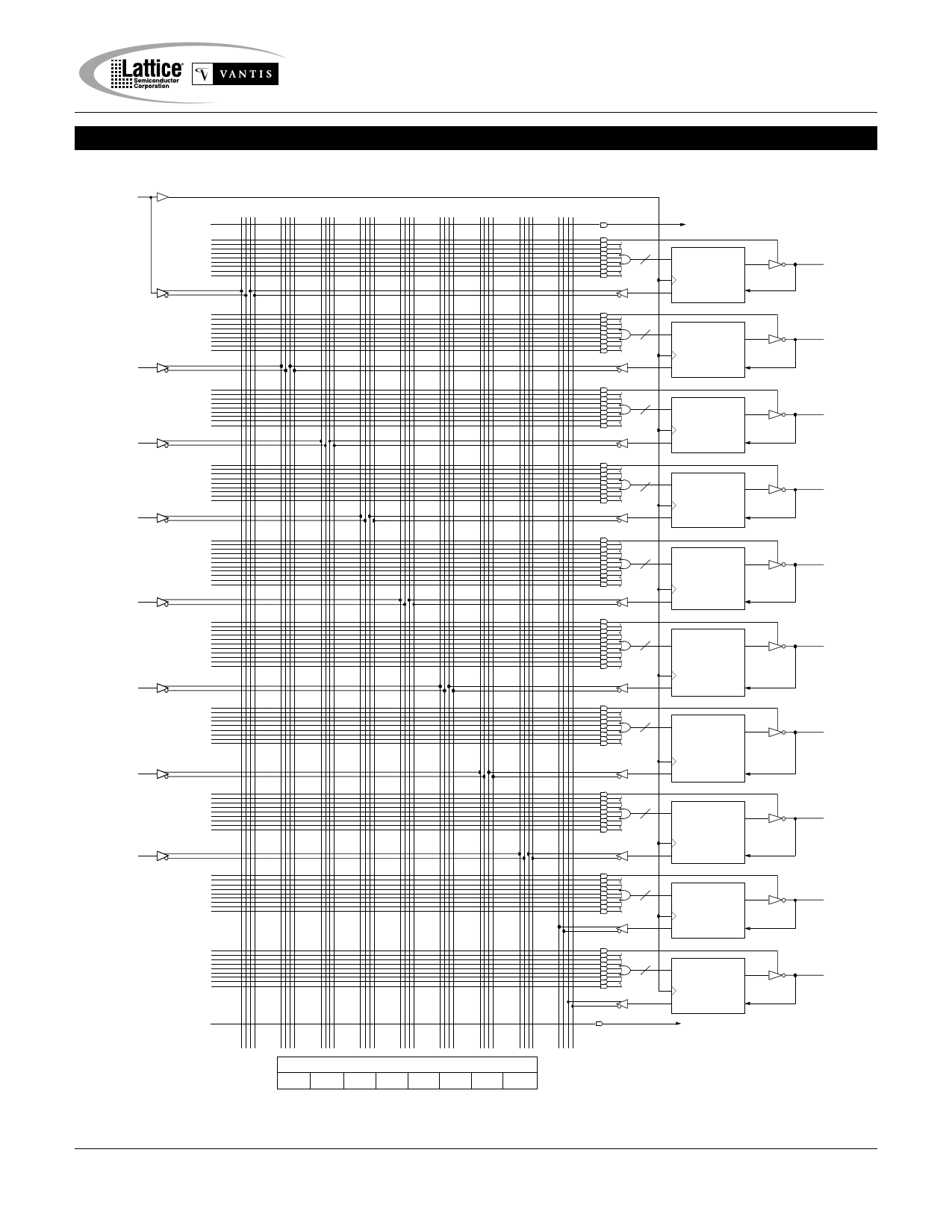

Functional Block Diagram

I/CLK

I

I

I

I

I

I

I

RESET

8

OLMC

8

OLMC

8

OLMC

8

OLMC

10

OLMC

10

OLMC

8

OLMC

8

OLMC

8

OLMC

8

OLMC

PRESET

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

I/O/Q

Pin Configuration

PLCC

I

I4

I I/CLK Vcc I/O/Q

2 20

18 I/O/Q

I I/O/Q

I 6 GAL18V10 16 I/O/Q

I

Top View

I/O/Q

I8

14 I/O/Q

9 11 13

I/O/Q GND I/O/Q I/O/Q I/O/Q

DIP

I/CLK

I

I

I

I

I

I

I

I/O/Q

GND

1 20 Vcc

I/O/Q

GAL

18V10

5

I/O/Q

I/O/Q

I/O/Q

15 I/O/Q

I/O/Q

I/O/Q

I/O/Q

10 11 I/O/Q

Copyright © 1997 Lattice Semiconductor Corp. All brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject

to change without notice.

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A.

Tel. (503) 681-0118; 1-888-ISP-PLDS; FAX (503) 681-3037; http://www.latticesemi.com

July 1997

18v10_03

1

1 page

Specifications GAL18V10

GAL18V10 Logic Diagram/JEDEC Fuse Map

DIP and PLCC Package Pinouts

1

0 4 8 12 16 20 24 28 32

0000

0036

.

.

.

0324

0360

.

.

.

0648

2

0684

.

.

.

0972

3

1008

.

.

.

1296

4

1332

.

.

.

.

1692

5

1728

.

.

.

.

2088

6

2124

.

.

.

2412

7

2448

.

.

.

2736

8

2772

.

.

.

3060

3096

.

.

.

3384

3420

3476, 3477 ... Electronic Signature

... 3538, 3539

Byte 7 Byte 6 Byte 5 Byte 4 Byte 3 Byte 2 Byte 1 Byte 0

ML

SS

BB

ASYNCHRONOUS RESET

(TO ALL REGISTERS)

8 OLMC

S0

3456

S1

3457

19

8 OLMC

S0

3458

S1

3459

18

8 OLMC

SO

3460

S1

3461

17

8 OLMC

S0

3462

S1

3463

16

10 OLMC

S0

3464

S1

3465

15

10 OLMC

S0

3466

S1

3467

14

8 OLMC

S0

3468

S1

3469

13

8 OLMC

S0

3470

S1

3471

12

8 OLMC

S0

3472

S1

3473

11

8 OLMC

S0

3474

S1

3475

9

SYNCHRONOUS PRESET

(TO ALL REGISTERS)

5

5 Page

fmax Descriptions

CLK

LOGIC

ARRAY

REGISTER

tsu tco

fmax with External Feedback 1/(tsu+tco)

Note: fmax with external feedback is cal-

culated from measured tsu and tco.

CLK

LOGIC

ARRAY

REGISTER

tsu + th

fmax with No Feedback

Note: fmax with no feedback may be less

than 1/(twh + twl). This is to allow for a

clock duty cycle of other than 50%.

Switching Test Conditions

Input Pulse Levels

Input Rise and

-7/-10

Fall Times

-15/-20

Input Timing Reference Levels

Output Timing Reference Levels

Output Load

GND to 3.0V

2ns 10% – 90%

3ns 10% – 90%

1.5V

1.5V

See Figure

3-state levels are measured 0.5V from steady-state active

level.

Output Load Conditions (see figure)

Test Condition

R1 R2

CL

A

B Active High

Active Low

C Active High

Active Low

300Ω

∞

300Ω

∞

300Ω

390Ω

390Ω

390Ω

390Ω

390Ω

50pF

50pF

50pF

5pF

5pF

Specifications GAL18V10

LOGIC

ARRAY

CLK

REGISTER

t cf

t pd

fmax with Internal Feedback 1/(tsu+tcf)

Note: tcf is a calculated value, derived by sub-

tracting tsu from the period of fmax w/internal

feedback (tcf = 1/fmax - tsu). The value of tcf is

used primarily when calculating the delay from

clocking a register to a combinatorial output

(through registered feedback), as shown above.

For example, the timing from clock to a combi-

natorial output is equal to tcf + tpd.

+5V

R1

FROM OUTPUT (O/Q)

UNDER TEST

R2

TEST POINT

C L*

*C L INCLUDES TEST FIXTURE AND PROBE CAPACITANCE

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet GAL18V10.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GAL18V10 | High Performance E2CMOS PLD Generic Array Logic | Lattice Semiconductor |

| GAL18V10-15LJ | High Performance E2CMOS PLD Generic Array Logic | Lattice Semiconductor |

| GAL18V10-15LP | High Performance E2CMOS PLD Generic Array Logic | Lattice Semiconductor |

| GAL18V10-20LJ | High Performance E2CMOS PLD Generic Array Logic | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |