|

|

PDF NT5CB128M8AN Data sheet ( Hoja de datos )

| Número de pieza | NT5CB128M8AN | |

| Descripción | 1Gb DDR3 SDRAM A-Die | |

| Fabricantes | Nanya | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NT5CB128M8AN (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

1Gb DDR3 SDRAM A-Die

NT5CB256M4AN / NT5CB128M8AN / NT5CB64M16AP

Feature

1.5V ± 0.075V (JEDEC Standard Power Supply)

8 Internal memory banks (BA0- BA2)

Differential clock input (CK, )

Programmable Latency: 5, 6, 7, 8, 9

Programmable Additive Latency: 0, CL-1, CL-2

Programmable Sequential / Interleave Burst Type

Programmable Burst Length: 4, 8

8 bit prefetch architecture

Output Driver Impedance Control

Write Leveling

OCD Calibration

Dynamic ODT (Rtt_Nom & Rtt_WR)

Auto Self-Refresh

Self-Refresh Temperature

Partial Array Self-Refresh

RoHS Compliance

Packages:

78-Ball BGA for x4 & x8 components

96-Ball BGA for x16 components

Description

The 1Gb Double-Data-Rate-3 (DDR3) DRAMs is a high-speed CMOS Double Data Rate32 SDRAM containing 1,073,741,824 bits. It is

internally configured as an octal-bank DRAM.

The 1Gb chip is organized as 32Mbit x 4 I/O x 8, 16Mbit x 8 I/O x 8 bank or 8Mbit x 16 I/O x 8 bank device. These synchronous devices

achieve high speed double-data-rate transfer rates of up to 1600 Mb/sec/pin for general applications.

The chip is designed to comply with all key DDR3 DRAM key features and all of the control and address inputs are synchronized with a

pair of externally supplied differential clocks. Inputs are latched at the cross point of differential clocks (CK rising and falling). All

I/Os are synchronized with a single ended DQS or differential DQS pair in a source synchronous fashion.

These devices operate with a single 1.5V ± 0.75V power supply and are available in BGA packages.

REV 1.2

01 / 2009

1

1 page

1Gb DDR3 SDRAM A-Die

NT5CB256M4AN / NT5CB128M8AN / NT5CB64M16AP

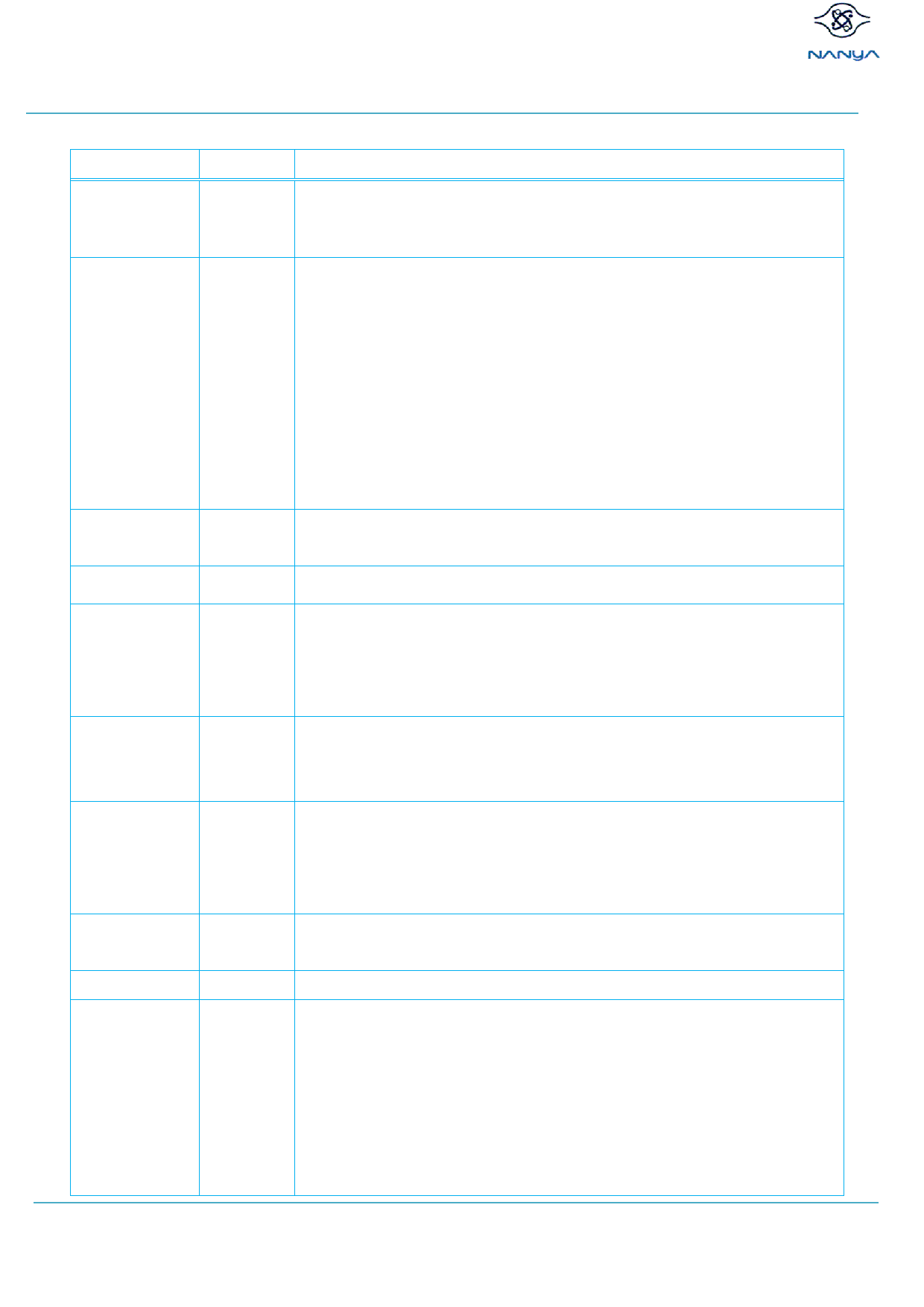

Input / Output Functional Description

Symbol

Type

Function

CK,

Input

Clock: CK and are differential clock inputs. All address and control input signals are sampled on

the crossing of the positive edge of CK and negative edge of .

CKE

, ,

DM, (DMU, DML)

BA0 - BA2

A0 – A13

A12 / BC#

DQ

DQU, DQL

DQS, ()

DQSL, (),

DQSU,()

Input

Input

Clock Enable: CKE high activates, and CKE low deactivates, internal clock signals and device

input buffers and output drivers. Taking CKE low provides Precharge Power-Down and

Self-Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is

synchronous for power down entry and exit and for Self-Refresh entry. CKE is asynchronous for

Self-Refresh exit. After VREF has become stable during the power on and initialization sequence, it

must be maintained for proper operation of the CKE receiver. For proper self-refresh entry and exit,

VREF must maintain to this input. CKE must be maintained high throughout read and write

accesses. Input buffers, excluding CK, , ODT and CKE are disabled during Power Down. Input

buffers, excluding CKE, are disabled during Self-Refresh.

Chip Select: All commands are masked when is registered high. provides for external rank

selection on systems with multiple memory ranks. is considered part of the command code.

Input

Command Inputs: , and (along with ) define the command being entered.

Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is

Input

sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges

of DQS. For x8 device, the function of DM or TDQS / is enabled by Mode Register A11

setting in MR1

Bank Address Inputs: BA0, BA1, and BA2 define to which bank an Active, Read, Write or

Input

Precharge command is being applied. Bank address also determines which mode register is to be

accessed during a MRS cycle.

Address Inputs: Provide the row address for Activate commands and the column address for

Input

Read/Write commands to select one location out of the memory array in the respective bank.

(A10/AP and A12/BC# have additional function as below. The address inputs also provide the

Input

op-code during Mode Register Set commands. A13 did not apply on x16 device.

Burst Chop: A12/ is sampled during Read and Write commands to determine if burst chop (on

the fly) will be performed. (HIGH - no burst chop; LOW - burst chopped).

Input/output Data Inputs/Output: Bi-directional data bus.

Data Strobe: output with read data, input with write data. Edge aligned with read data, centered

with write data. For the x16, DQSL corresponds to the data on DQL0 - DQL7; DQSU corresponds to

the data on DQU0-DQU7. The data strobes DQS, DQSL, DQSU are paired with differential signals

Input/output , , , respectively, to provide differential pair signaling to the system during both

reads and writes. DDR3 SDRAM supports differential data strobe only and does not support

single-ended.

REV 1.2

01 / 2009

5

5 Page

1Gb DDR3 SDRAM A-Die

NT5CB256M4AN / NT5CB128M8AN / NT5CB64M16AP

DDR3 Reset and Initialization Sequence at Power-on Ramping

Ta Tb Tc Td Te Tf Tg Th

tCKSRX

CK

CK

Ti Tj

Tk

RESET

CKE

10ns

tIS

Valid

ODT

Static LOW in case RTT_Nom is enabled at time Tg, otherwise static HIGH or LOW

Valid

Command

NOP*

MRS

MRS

MRS

MRS

ZQCL

NOP*

Valid

BA0-BA2

VDD,

VDDQ

T=200us

Do Not

Care

T=500us

Time break

MR2

MR3

MR1

MR0

Valid

tXPR

tMRD

tMRD

tMRD

tDLLK

tMOD

tZQinit.

* From time point Td until Tk. NOP or DES commands must be applied between MRS and ZQcal commnads.

DDR3 Reset Procedure at Power Stable Condition

The following sequence is required for RESET at no power interruption initialization.

1. Asserted RESET below 0.2*VDD anytime when reset is needed (all other inputs may be undefined). RESET needs to be maintained

for minimum 100ns. CKE is pulled “Low” before RESET being de-asserted (min. time 10ns).

2. Follow Power-up Initialization Sequence step 2 to 11.

3. The Reset sequence is now completed. DDR3 SDRAM is ready for normal operation.

Ta Tb Tc Td Te Tf Tg Th

tCKSRX

CK

CK

RESET

CKE

10ns

tIS

Ti

Tj Tk

Valid

ODT

Static LOW in case RTT_Nom is enabled at time Tg, otherwise static HIGH or LOW

Valid

Command

NOP*

MRS

MRS

MRS

MRS

ZQCL

NOP*

Valid

BA0-BA2

VDD,

VDDQ

T=100ns

Do Not

Care

T=500us

Time break

MR2

MR3

MR1

MR0

Valid

tXPR

tMRD

tMRD

tMRD

tDLLK

tMOD

tZQinit.

* From time point Td until Tk. NOP or DES commands must be applied between MRS and ZQcal commnads.

REV 1.2

01 / 2009

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet NT5CB128M8AN.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NT5CB128M8AN | 1Gb DDR3 SDRAM A-Die | Nanya |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |