|

|

PDF GD25Q16B Data sheet ( Hoja de datos )

| Número de pieza | GD25Q16B | |

| Descripción | Dual and Quad Serial Flash | |

| Fabricantes | GigaDevice | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de GD25Q16B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Uniform Sector

Dual and Quad Serial Flash

GD25Q16B

GD25Q16B

DATASHEET

1

1 page

Uniform Sector

Dual and Quad Serial Flash

2. GENERAL DESCRIPTION

GD25Q16B

The GD25Q16B (16M-bit) Serial flash supports the standard Serial Peripheral Interface (SPI), and supports the

Dual/Quad SPI: Serial Clock, Chip Select, Serial Data I/O0 (SI), I/O1 (SO), I/O2 (WP#), and I/O3 (HOLD#). The Dual I/O

data is transferred with speed of 240Mbits/s and the Quad I/O & Quad output data is transferred with speed of

480Mbits/s.

CONNECTION DIAGRAM

CS# 1

8 VCC

SO

WP#

27

Top View

36

HOLD#

SCLK

VSS

45

8–LEAD SOP/DIP

SI

CS# 1

8 VCC

SO 2

WP# 3

Top View

7 HOLD#

6 SCLK

VSS 4

5 SI

8–LEAD WSON/USON

Top View

4

NC VCC WP# HOLD# NC NC

3

NC VSS NC SI NC NC

2

NC SCLK CS# SO NC NC

1

NC NC NC NC NC NC

A BCDE F

24-BALL TFBGA

PIN DESCRIPTION

Pin Name

I/O

CS# I

SO (IO1)

I/O

WP# (IO2)

I/O

VSS

SI (IO0)

I/O

SCLK

I

HOLD# (IO3)

I/O

VCC

Description

Chip Select Input

Data Output (Data Input Output 1)

Write Protect Input (Data Input Output 2)

Ground

Data Input (Data Input Output 0)

Serial Clock Input

Hold Input (Data Input Output 3)

Power Supply

5

5 Page

Uniform Sector

Dual and Quad Serial Flash

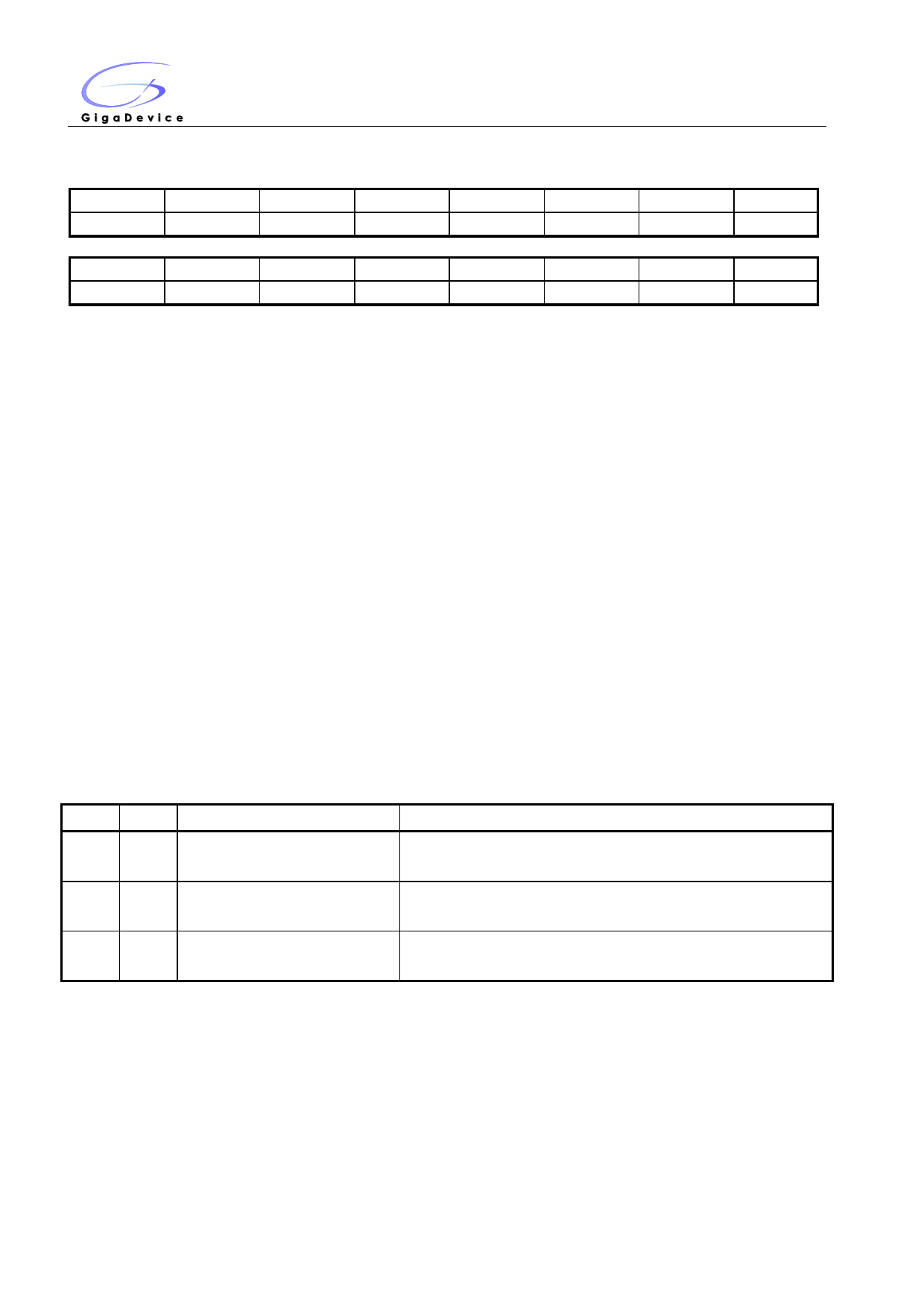

6. STATUS REGISTER

GD25Q16B

S15

SUS

S14

CMP

S13

Reserved

S12

Reserved

S11

Reserved

S10

LB

S9 S8

QE Reserved

S7 S6 S5 S4 S3 S2 S1 S0

SRP

BP4

BP3

BP2

BP1

BP0

WEL

WIP

The status and control bits of the Status Register are as follows:

WIP bit.

The Write In Progress (WIP) bit indicates whether the memory is busy in program/erase/write status register progress.

When WIP bit sets to 1, means the device is busy in program/erase/write status register progress, when WIP bit sets 0,

means the device is not in program/erase/write status register progress.

WEL bit.

The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1 the internal

Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset and no Write Status Register, Program or

Erase command is accepted.

BP4, BP3, BP2, BP1, BP0 bits.

The Block Protect (BP4, BP3, BP2, BP1, BP0) bits are non-volatile. They define the size of the area to be software

protected against Program and Erase commands. These bits are written with the Write Status Register (WRSR) command.

When the Block Protect (BP4, BP3, BP2, BP1, BP0) bits are set to 1, the relevant memory area (as defined in

Table1).becomes protected against Page Program (PP), Sector Erase (SE) and Block Erase (BE) commands. The Block

Protect (BP4, BP3, BP2, BP1, BP0) bits can be written provided that the Hardware Protected mode has not been set. The

Chip Erase (CE) command is executed, if the Block Protect (BP2, BP1, BP0) bits and CMP are all 0 or all 1.

SRP bit.

The Status Register Protect (SRP) bit is non-volatile Read/Write bits in the status register. The SRP bit controls the

method of write protection: software protection, hardware protection, power supply lock-down or one time programmable

protection.

SRP #WP

Status Register

Description

0X

Software Protected

The Status Register can be written to after a Write Enable

command, WEL=1.(Default)

10

Hardware Protected

WP#=0, the Status Register locked and can not be written to.

11

Hardware Unprotected

WP#=1, the Status Register is unlocked and can be written to after

a Write Enable command, WEL=1.

QE bit.

The Quad Enable (QE) bit is a non-volatile Read/Write bit in the Status Register that allows Quad operation. When

the QE bit is set to 0 (Default) the WP# pin and HOLD# pin are enable. When the QE pin is set to 1, the Quad IO2 and IO3

pins are enabled. (The QE bit should never be set to 1 during standard SPI or Dual SPI operation if the WP# or HOLD#

pins are tied directly to the power supply or ground)

LB bit.

The LB bit is a non-volatile One Time Program (OTP) bit in Status Register (S10) that provide the write protect control

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet GD25Q16B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GD25Q16 | 16Mbit Dual and Quad SPI Flash | GigaDevice |

| GD25Q16B | Dual and Quad Serial Flash | GigaDevice |

| GD25Q16B | Uniform sector dual and quad serial flash | ELM |

| GD25Q16C | 3.3V Uniform Sector Dual and Quad Serial Flash | ELM |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |