|

|

PDF VS8063a Data sheet ( Hoja de datos )

| Número de pieza | VS8063a | |

| Descripción | MP3 / OGG VORBIS ENCODER AND AUDIO CODEC CIRCUIT | |

| Fabricantes | VLSI | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de VS8063a (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

VS1063a Datasheet

VS1063a / VS1163a / VS8063a

MP3 / OGG VORBIS ENCODER

AND AUDIO CODEC CIRCUIT

Key Features

Description

• Encoders:

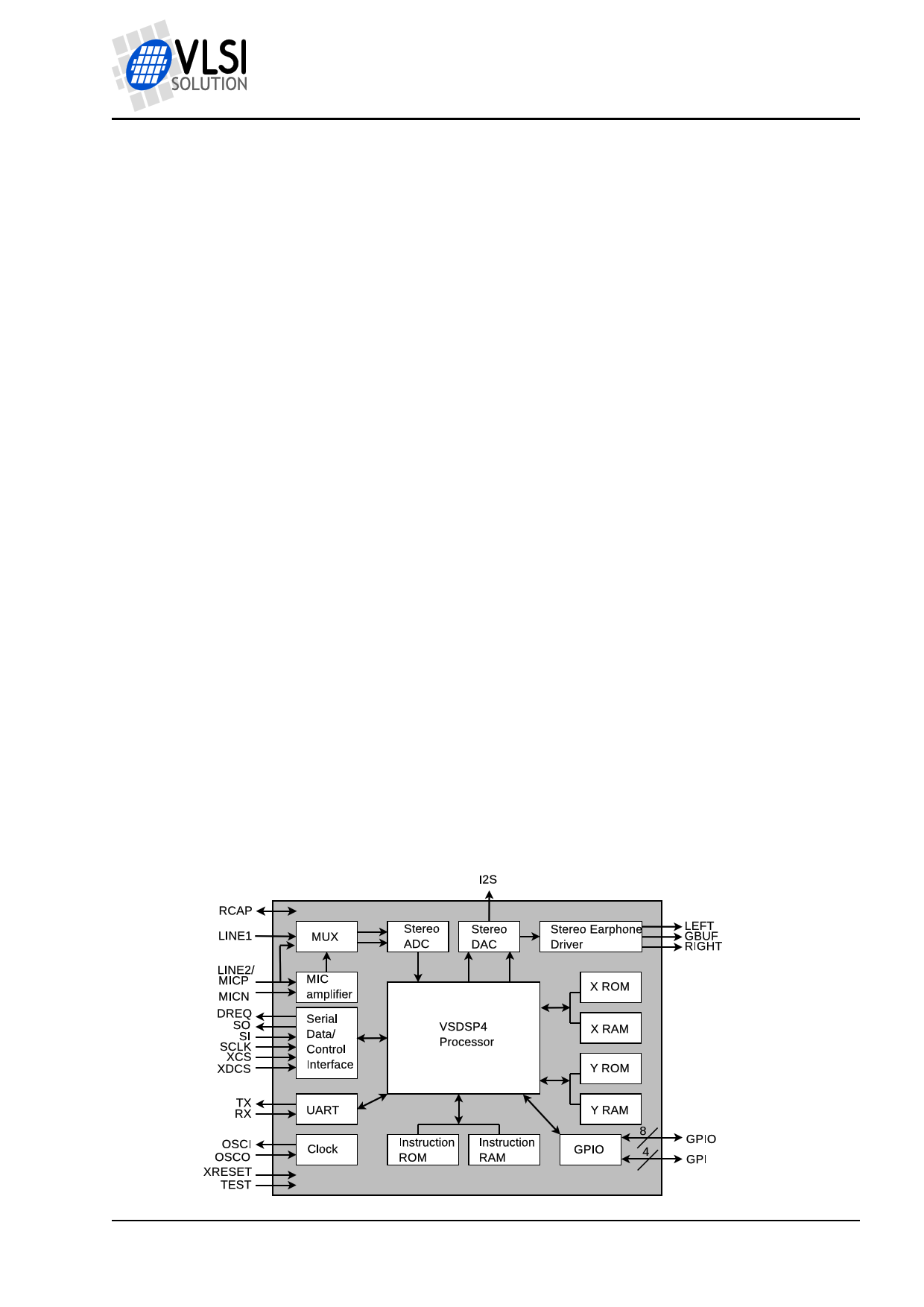

VS1063a is an easy-to-use, versatile encoder,

MP3; Ogg Vorbis; PCM; IMA ADPCM; decoder and codec for a multitude of audio

G.711 (µ-law, A-law); G.722 ADPCM

formats.

• Decoders:

MP3 (MPEG 1 & 2 audio layer III (CBR VS1063a contains a high-performance, pro-

+VBR +ABR));

prietary low-power DSP core VS_DSP4, ROM

MP2 (layer II) (optional);

memories, 16 KiB instruction RAM and upto

MPEG4 / 2 AAC-LC(+PNS),

80 KiB data RAM for user applications run-

HE-AAC v2 (Level 3) (SBR + PS);

ning simultaneously with any built-in decoder,

Ogg Vorbis; FLAC;

serial control and input data interfaces, upto

WMA 4.0/4.1/7/8/9 all profiles (5-384 kbps); 12 general purpose I/O pins, a UART, as well

WAV (PCM, IMA ADPCM, G.711 µ-law/A- as a high-quality variable-sample-rate stereo

law, G.722 ADPCM)

DAC and a stereo ADC, followed by an ear-

• Full Duplex Codecs with optional AEC: phone amplifier and a common voltage buffer.

PCM; G.711 (µ-law, A-law); G.722 ADPCM;

IMA ADPCM

VS1063a can act both as an “MP3 decoder

• Streaming support

IC” or “MP3 encoder IC” slave in a system

• Upto 96 KiB RAM for user code and data with a microcontroller, or as a stand-alone cir-

• Unique ID for user code protection

cuit that boots from external SPI memory.

• Quiet power-on and power-off

• I2S output interface for external DAC

Applications

• Serial control and data interfaces

• Can be used either as a slave co-processor

or as a standalone processor

• UART for debugging purposes

• New functions may be added with soft-

• MP3-recording audio player

• Streaming server and client

• Wireless audio transfer

• Standalone player and recorder

ware and upto 12 GPIO pins

• Internet phones

Version: 1.20, 2016-03-24

1

1 page

VS1063a Datasheet

CONTENTS

11.6.2 The Encoding Procedure . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.3 Reading Encoded Data Through SCI . . . . . . . . . . . . . . . . . .

11.6.4 File Headers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.5 Playing Encoded Data . . . . . . . . . . . . . . . . . . . . . . . . . .

11.6.6 Encoder Samplerate Considerations . . . . . . . . . . . . . . . . . .

11.6.7 Encode Monitoring Volume . . . . . . . . . . . . . . . . . . . . . . . .

11.6.8 MP3 (format 5) Encoder Specific Considerations (VS1063a Only) . .

11.6.9 Ogg Vorbis (format 6) Encoder Specific Considerations . . . . . . . .

11.6.10 Estimated Minimum Encoder/Decoder Delays . . . . . . . . . . . . .

11.7 Codec Mode (Full-Duplex) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.8 SPI Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.9 I2C Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.10 Extra Parameters (Parametric Structure) . . . . . . . . . . . . . . . . . . . . . .

11.10.1 Parametric: chipID, version, config1 . . . . . . . . . . . . . . . . . . .

11.10.2 Parametric: Player Configurations . . . . . . . . . . . . . . . . . . . .

11.10.3 Parametric: VU Meter . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.10.4 Parametric: AD Mixer . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.10.5 Parametric: PCM Mixer . . . . . . . . . . . . . . . . . . . . . . . . . .

11.10.6 Parametric: EQ5 5-band Equalizer . . . . . . . . . . . . . . . . . . .

11.10.7 Parametric: Speed Shifter . . . . . . . . . . . . . . . . . . . . . . . .

11.10.8 Parametric: EarSpeaker . . . . . . . . . . . . . . . . . . . . . . . . .

11.10.9 Parametric: Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.10.10Parametric: WMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.10.11Parametric: AAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.10.12Parametric: Ogg Vorbis . . . . . . . . . . . . . . . . . . . . . . . . . .

11.11 SDI Tests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.11.1 Sine Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.11.2 Pin Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.11.3 SCI Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.11.4 Memory Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.11.5 New Sine and Sweep Tests . . . . . . . . . . . . . . . . . . . . . . .

11.12 I2S Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.13 Clock Speed Requirents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11.13.1 Clock Speed Requirements for Decoders . . . . . . . . . . . . . . . .

11.13.2 Clock Speed Requirements for Encoders . . . . . . . . . . . . . . . .

11.13.3 Clock Speed Requirements for DSP Algorithms . . . . . . . . . . . .

61

62

63

64

64

64

65

65

66

67

68

68

69

70

71

73

74

75

76

78

78

79

80

81

82

83

83

83

83

84

84

85

86

86

86

87

12 VS1063a Version Changes

88

12.1 Firmware Changes Between VS1053b and VS1063a, 2011-04-13 . . . . . . . . 88

13 VS1063a Errata

90

14 Latest Document Version Changes

92

15 Contact Information

94

Version: 1.20, 2016-03-24

5

5 Page

VS1063a Datasheet

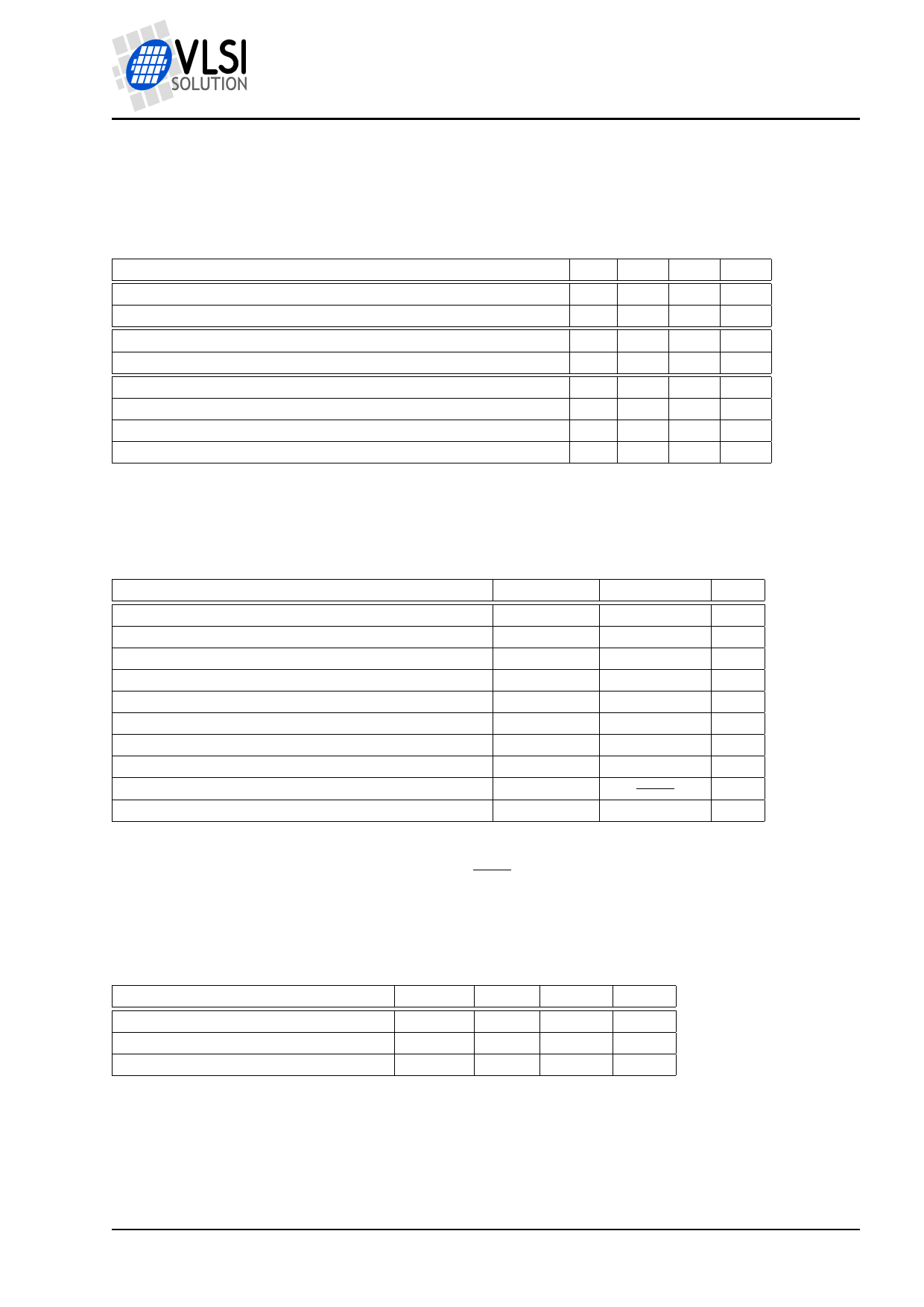

5 CHARACTERISTICS & SPECIFICATIONS

5.4 Power Consumption

Tested with an Ogg Vorbis 128 kbps sample and generated sine. Output at full volume. Internal

clock multiplier 3.0×. TA=+25◦C.

Parameter

Min Typ Max Unit

Power Supply Consumption AVDD, Reset

Power Supply Consumption CVDD = 1.8V, Reset

0.6 5.0 µA

12 20.0 µA

Power Supply Consumption AVDD, sine test, 30 Ω + GBUF 30 36.9 60 mA

Power Supply Consumption CVDD = 1.8V, sine test

8 10 15 mA

Power Supply Consumption AVDD, no load

Power Supply Consumption AVDD, output load 30 Ω

Power Supply Consumption AVDD, 30 Ω + GBUF

Power Supply Consumption CVDD = 1.8V

5 mA

11 mA

11 mA

11 mA

5.5 Digital Characteristics

Parameter

High-Level Input Voltage (xRESET, XTALI, XTALO)

High-Level Input Voltage (other input pins)

Low-Level Input Voltage

High-Level Output Voltage at XTALO = -0.1 mA

Low-Level Output Voltage at XTALO = 0.1 mA

High-Level Output Voltage at IO = -1.0 mA

Low-Level Output Voltage at IO = 1.0 mA

Input Leakage Current

SPI Input Clock Frequency 2

Rise time of all output pins, load = 50 pF

Min

0.7×IOVDD

0.7×CVDD

-0.2

0.7×IOVDD

0.7×IOVDD

-1.0

Max

IOVDD+0.31

IOVDD+0.31

0.3×CVDD

0.3×IOVDD

0.3×IOVDD

1.0

C LK I

7

50

Unit

V

V

V

V

V

V

V

µA

MHz

ns

1 Must not exceed 3.6V

2

Value

for

SCI

reads.

SCI

and

SDI

writes

allow

C

LK

4

I

.

5.6 Switching Characteristics - Boot Initialization

Parameter

XRESET active time

XRESET inactive to software ready

Power on reset, rise time to CVDD

Symbol

Min

2

22000

10

Max

500001

Unit

XTALI

XTALI

V/s

1 DREQ rises when initialization is complete. Do not send any data or commands before that.

Version: 1.20, 2016-03-24

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet VS8063a.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| VS8063a | MP3 / OGG VORBIS ENCODER AND AUDIO CODEC CIRCUIT | VLSI |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |