|

|

PDF 74S112 Data sheet ( Hoja de datos )

| Número de pieza | 74S112 | |

| Descripción | STTL double-J-K flip-flop | |

| Fabricantes | TW | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 74S112 (archivo pdf) en la parte inferior de esta página. Total 3 Páginas | ||

|

No Preview Available !

典型参数:

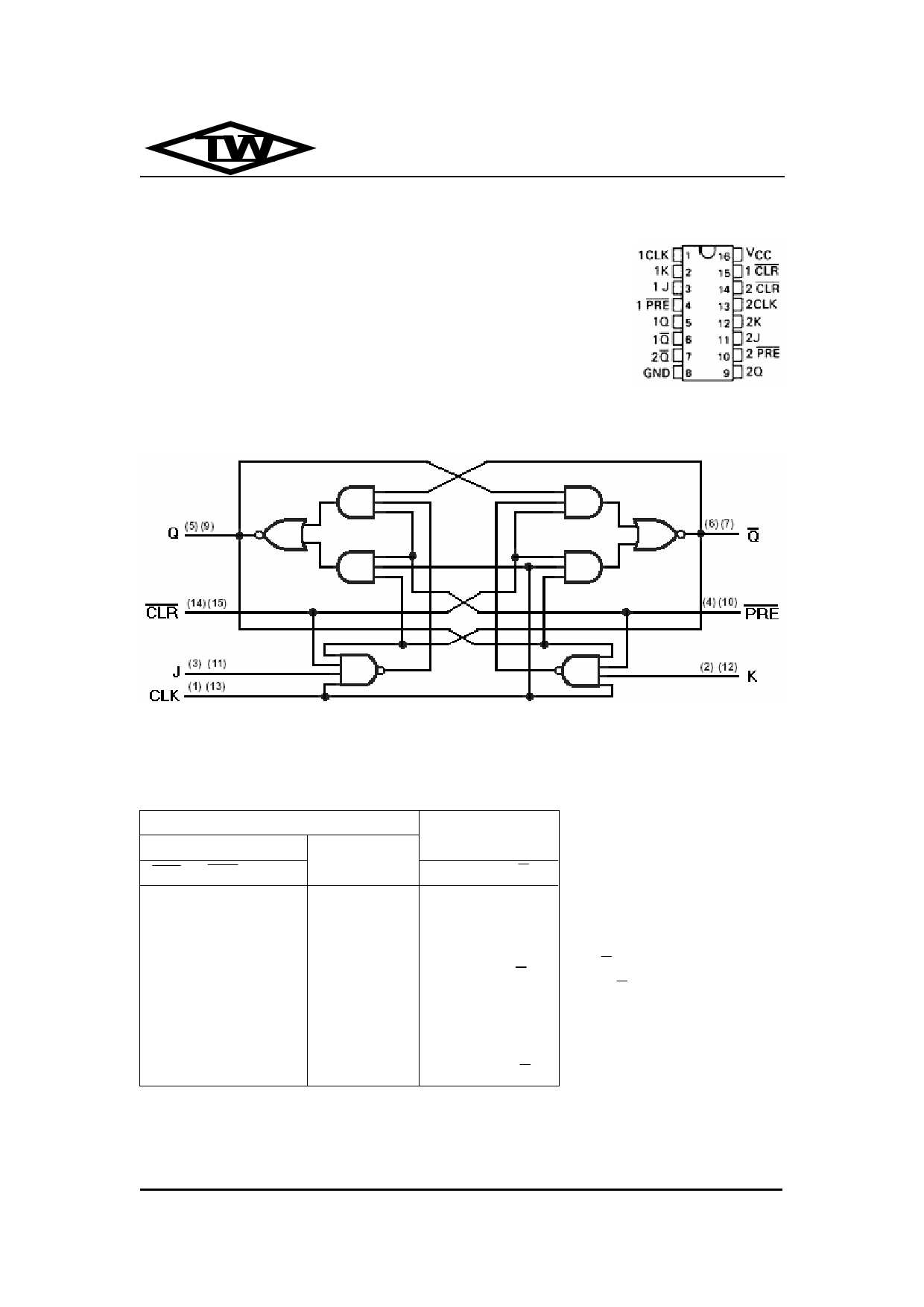

54S112/74S112

STTL 型双 J-K 触发器(负沿触发、带清零和预置)

外引线排列图

f 工作频率=125MHz

Pd=75mW

逻辑图

功能表

输

预置 清除

PRE CLR

LH

HL

LL

HH

HH

HH

HH

HH

时钟

CLK

×

×

×

↓

↓

↓

↓

H

入

JK

××

××

××

LL

HL

LH

HH

××

输出

QQ

HL

LH

H* H*

QO Q0

HL

LH

翻转

QO Q0

H=高电平 L=低电平

×=不定

↓=从高电平过渡到低电平

QO=建立稳态输入条件之前

的 Q 电平

Q0 =建立稳态输入条件之前

的 Q 电平

* 这种情况是不稳定的,即

当预置和清除输入回到高电

平时,状态将不能保持。

www.BDTIC.comBDTIC 半导体事业部 www.bdtic.com/Semiconductor

1 page | ||

| Páginas | Total 3 Páginas | |

| PDF Descargar | [ Datasheet 74S112.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74S112 | Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flop | Fairchild Semiconductor |

| 74S112 | STTL double-J-K flip-flop | TW |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |