|

|

PDF XP2-30 Data sheet ( Hoja de datos )

| Número de pieza | XP2-30 | |

| Descripción | FPGA fabric | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de XP2-30 (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

LatticeXP2™ Family Data Sheet

DS1009 Version 01.8, January 2012

1 page

Lattice Semiconductor

Architecture

LatticeXP2 Family Data Sheet

Figure 2-1. Simplified Block Diagram, LatticeXP2-17 Device (Top Level)

sysIO Buffers,

Pre-Engineered Source

Synchronous Support

On-chip

Oscillator

Programmable

Function Units

(PFUs)

SPI Port

sysMEM Block

RAM

DSP Blocks

JTAG Port

Flash

sysCLOCK PLLs

Flexible Routing

PFU Blocks

The core of the LatticeXP2 device is made up of logic blocks in two forms, PFUs and PFFs. PFUs can be pro-

grammed to perform logic, arithmetic, distributed RAM and distributed ROM functions. PFF blocks can be pro-

grammed to perform logic, arithmetic and ROM functions. Except where necessary, the remainder of this data

sheet will use the term PFU to refer to both PFU and PFF blocks.

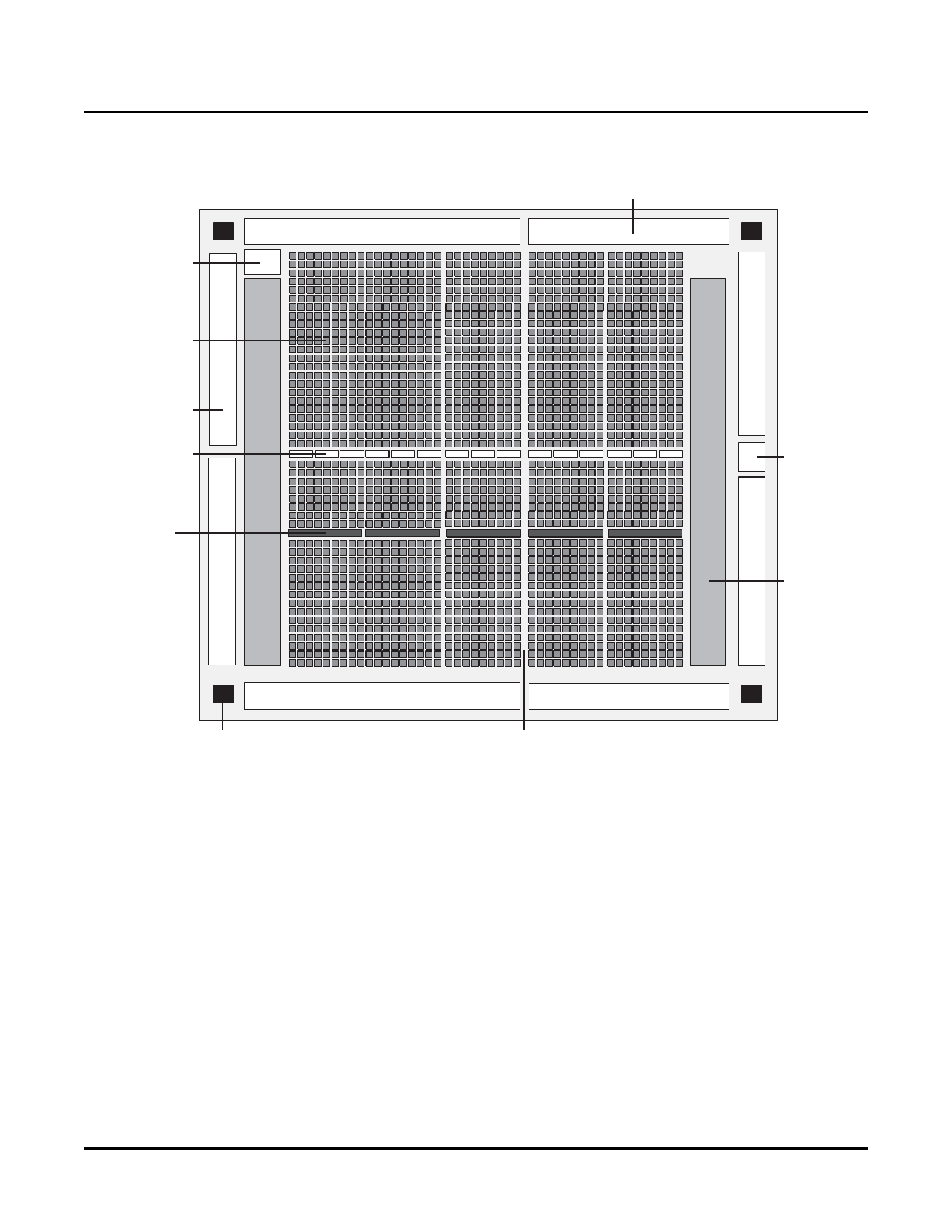

Each PFU block consists of four interconnected slices, numbered Slice 0 through Slice 3, as shown in Figure 2-2.

All the interconnections to and from PFU blocks are from routing. There are 50 inputs and 23 outputs associated

with each PFU block.

2-2

5 Page

Lattice Semiconductor

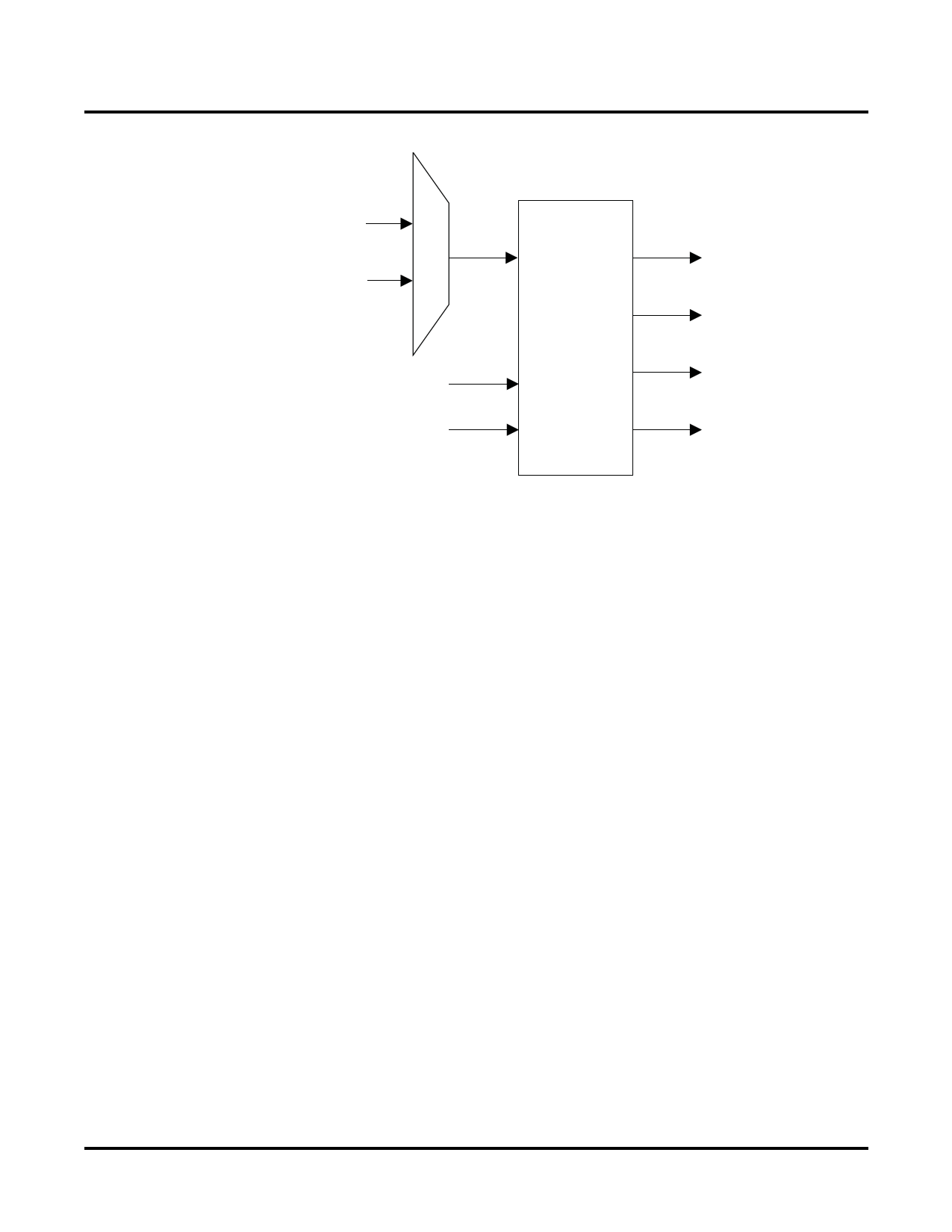

Figure 2-5. Clock Divider Connections

Architecture

LatticeXP2 Family Data Sheet

ECLK

CLKOP (GPLL)

RST

RELEASE

CLKDIV

÷1

÷2

÷4

÷8

Clock Distribution Network

LatticeXP2 devices have eight quadrant-based primary clocks and between six and eight flexible region-based sec-

ondary clocks/control signals. Two high performance edge clocks are available on each edge of the device to sup-

port high speed interfaces. The clock inputs are selected from external I/Os, the sysCLOCK PLLs, or routing. Clock

inputs are fed throughout the chip via the primary, secondary and edge clock networks.

Primary Clock Sources

LatticeXP2 devices derive primary clocks from four sources: PLL outputs, CLKDIV outputs, dedicated clock inputs

and routing. LatticeXP2 devices have two to four sysCLOCK PLLs, located in the four corners of the device. There

are eight dedicated clock inputs, two on each side of the device. Figure 2-6 shows the primary clock sources.

2-8

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet XP2-30.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XP2-30 | FPGA fabric | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |