|

|

PDF FLI2200 Data sheet ( Hoja de datos )

| Número de pieza | FLI2200 | |

| Descripción | Digital Component Video Deinterlacer / Line DOubler | |

| Fabricantes | Faroudja Labs | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de FLI2200 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Faroudja Laboratories

a Division of Sage, Inc.

Rev. 1.04

January 19, 2001

Company Confidential

FLI 2200

Digital Component Video

Deinterlacer/Line Doubler

1 page

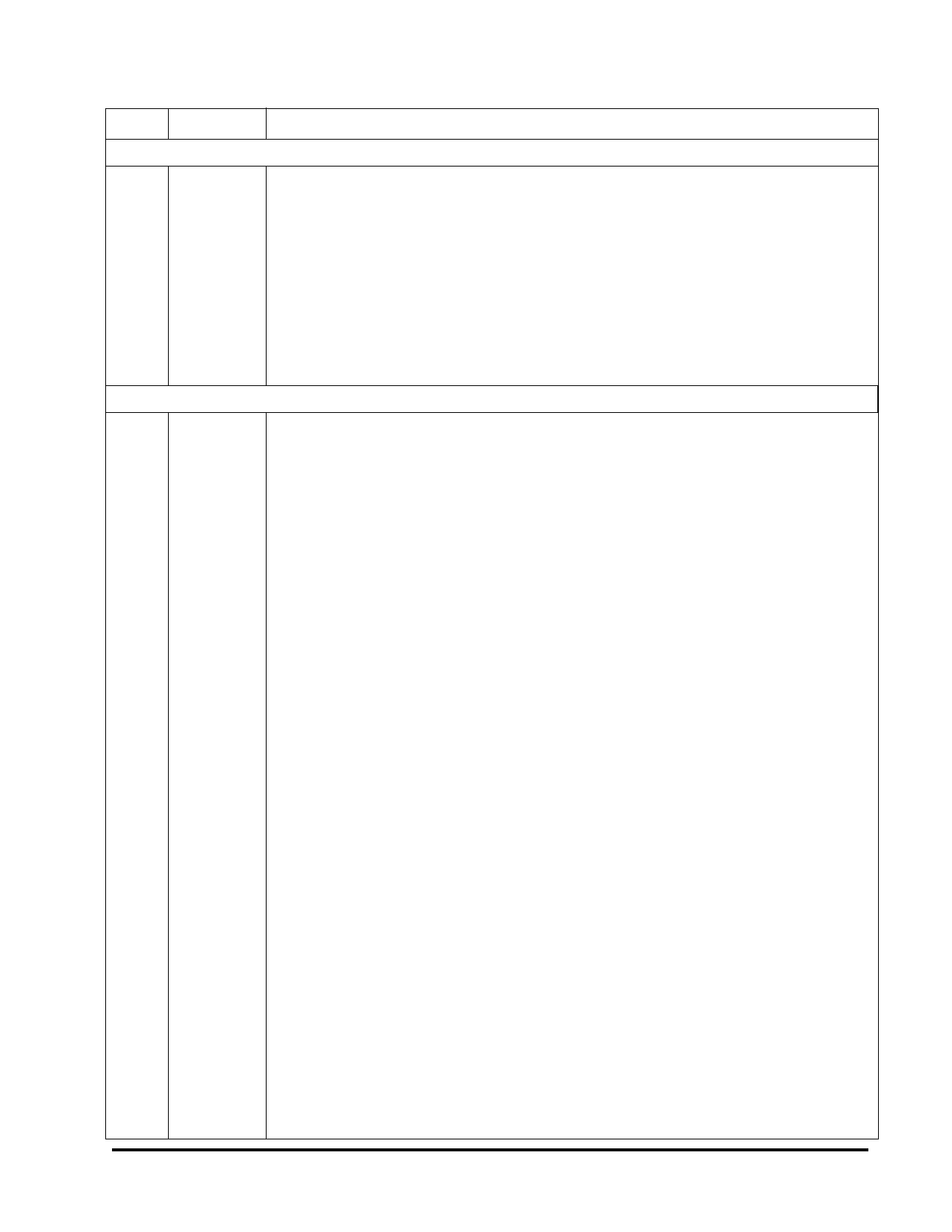

Pin Connections and Functions

Pin # Name

Description

Power Supply Connections (not shown on Block diagram)

See list VSS

Ground connections. Connect to the digital ground plane. Pins: 2, 17, 34, 55, 64, 74, 85,

96, 106, 115, 124, 132, 138, 145, 152, 159, 168

See list VDD33

Pad Ring digital power connections. Connect to the digital 3.3 volt power supply and

decouple to the digital ground plane. Pins: 1, 33, 63, 73, 84, 95, 105, 114, 123, 137, 144,

151, 167

See list VDD25

Core Logic digital power connections. Connect to the digital 2.5 volt power supply and

decouple to the digital ground plane. Pins: 16, 54, 107, 158

43 AVSS

42 AVDD

Control Signals

Ground connection for the clock PLL circuits. Connect to the digital ground plane

Analog power connections for the clock PLL circuit. Connect to a separately decoupled 2.5

volt power supply and decouple directly to the AVSS pin..

49 RESETB Reset. When this input is set low it will reset all the internal registers to the default states.

Refer to the section on the control registers for details of these states. The device must be

reset after it is powered-up.

53 OE

When this pin is set high the outputs of the FLI2200 will be enabled; when it is set low the

outputs will be set into a high-impedance state.

56-58

59-61

44-45

IFORMAT2-0 Input signal format control. The settings of these pins set the format of the input signal.

This can be overridden by the IFmtOvr bit, bit 3 in register 00H, allowing this function to be

set or changed via the I2C bus. Please refer to the description of register 00H for details.

OFORMAT2-0 Output signal format control. The settings of these pins set the format of the output signal.

This can be overridden by the OFmtOvr bit, bit 3 in register 07H, allowing this function to be

set or changed via the I2C bus. Please refer to the description of register 07H for details.

DADDR1-0

The settings of DADDR1-0 allow the device address of the control bus to be programmed to

prevent conflict with the other devices connected to the bus. DADDR1-0 allow the device

address to be set to any of the following values: C0/C1H, C2/C3H, E0/E1H, E2/E3H. Please refer

to the section “Control Bus Operation and Protocol” for further information.

46 MODE When this pin is set low the control bus will operate in the slave mode; allowing the device to

programmed from an external controller. When it is set high the FLI2200 will self-program from

an external I2C memory connected to the bus. Please refer to the “Control Bus Operation and

Control Protocol” section for more details.

47 SDA

2-wire serial control bus data. Data can be written to the control registers via this pin when it

is in the input mode and data can be read from the status registers when it is in the output

mode. Refer to the section on the serial port for timing and format details and to the section on

the registers for programming information.

48 SCL

2-wire serial control bus clock. When the control port operates in slave mode this pin will be

an input and when it operates in the self programming mode it will be an output.

40

PIXCLK

Pixel clock input. This clock is used to drive all the circuits in the FLI2200. An internal PLL is

used to upconvert this clock to provide the master clock signal and other clocks used

internally. Note that when the FLI2200 is used in the D1 input mode the PIXCLK input

should run at the rate of two cycles per pixel (one for luma and one for chroma).

62 N/P/IN/OUT NTSC/PAL input or output. The default function of this pin is NTSC/PAL signal indicator

output. When the input video signal is a 525 line signal this pin will be set high and when it

is a 625 line signal the pin is set low. This function of this pin can be programmed to be an

input according to the setting of this pin if the NPOp1-0 bits, bits 5-4 in register 03H, are set

to 00H, overriding the internal line counter. i.e., it will treat the signal as a 525 line signal

when it is set high and a 625 line signal when it is set low.

© 2000-2001 Faroudja Labs, Inc.

Company Confidential

5 Rev. 1.04, 1/19/01 FLI2200

5 Page

Memory Map

Register

Bits

Default

Addr. Name 7 6 5 4 3 2 1 0 Value

00H INPUT CClmpEn YClmpEn SOnYG Sync/Ref IFmtOvr

IFormat2-0

D0H

01H YCLAMP

YClamp7-0

40H

02H CCLAMP

CClamp7-0

00H

03H NP

x

NPStat NPOp1-0

CClamp9-8

YClamp9-8

18H

04H DELAY

CDelay3-0

CSwapI

YDelay2-0

B4H

05H MODE1 Fm2430 x

Test Test DCDiOn FilmOn NMOvr NoMem 0CH/8CH

06H MODE2 CSync VITSEn F30Hz F30Inv Force30 Motion1-0

PComp 05H

07H OUTPUT CSwapO ChrPhs CIntDis OBlnkEn OFmtOvr

OFormat2-0

10H

08H IOSEL D1Valid CInSel COutSel D1InSel1-0

FSyncDel2-0

52H

09H GAIN x x x x x x YInGain CInGain 03H

0AH FDELAY

BSStart7-0

4AH

10H HSSTN

HSStartN7-0

00H

11H HSSPN

HSStopN7-0

00H

12H HRSTN

HRStartN7-0

00H

13H HRSPN

HRStopN7-0

00H

14H VMSN VSStartN5-4

VSStopN5-4

VRStartN5-4

VRStopN5-4

00H

15H VSSSN

VSStartN3-0

VSStopN3-0

00H

16H VRSSN

VRStartN3-0

VRStopN3-0

00H

17H VBIMSN x

VBStartN4 x

VBStopN4 VBIStartN5-4

VBIStopN5-4

00H

18H VBTN

VBStartN3-0

VBStopN3-0

00H

19H VBITN

VBIStartN3-0

VBIStopN3-0

00H

20H HSSTP

HSStartP7-0

00H

21H HSSPP

HSStopP7-0

00H

22H HRSTP

HRStartP7-0

00H

23H HRSPP

HSRtopP7-0

00H

24H HMSP HSStartP9-8

HSStopP9-8

HRStartP9-8

HRStopP9-8

00H

25H VSSTP

VSStartP7-0

00H

26H VSSPP

VSStopP7-0

00H

27H VRSTP

VRStartP7-0

01H

28H VRSPP

VRStopP7-0

01H

29H VBSTP

VBStartP7-0

01H

2A VBSPP

VBStopP7-0

00H

2B VBISTP

VBIStartP7-0

02H

2C VBISPP

VBIStopP7-0

08H

2EH VBTP Test

x

x

UseHSize x

HSize10-8

03H

2FH HSIZE

HSize7-0

60H

30H INV1

ISyncInv ORefInv OSyncInv DatBlnk HDatBlnk Test

Test

CCSOn 05H

31H EDBL

EdBlnkL7-0

E0H

© 2000-2001 Faroudja Labs, Inc.

Company Confidential

11 Rev. 1.04, 1/19/01 FLI2200

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet FLI2200.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FLI2200 | Digital Component Video Deinterlacer / Line DOubler | Faroudja Labs |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |