|

|

PDF ICM7245 Data sheet ( Hoja de datos )

| Número de pieza | ICM7245 | |

| Descripción | 8-Character 16-Segment Microprocessor Compatible LED Display Decoder Driver | |

| Fabricantes | INTERSIL | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICM7245 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

8-Character, 16-Segment, Microprocessor Compatible,

LED Display Decoder Driver

ICM7245

The ICM7245 is an 8-character, alphanumeric display driver

and controller which provides all the circuitry required to

interface a microprocessor or digital system to a 16-segment

display with internal pull-up resistors. It is primarily intended

for use in microprocessor systems, where it minimizes

hardware and software overhead. Incorporated on-chip are a

64-character ASClI decoder, 8x6 memory, high power

character and segment drivers, and the multiplex scan

circuitry.

6-bit ASCll data to be displayed is written into the memory

directly from the microprocessor data bus. Data location

depends upon the selection of either Sequential (MODE = 1) or

Random access mode (MODE = 0). In the Sequential Access

mode the first entry is stored in the lowest location and

displayed in the “left-most” character position. Each

subsequent entry is automatically stored in the next higher

location and displayed to the immediate “right” of the previous

entry. A DISPlay FULL signal is provided after 8 entries; this

signal can be used for cascading devices together. A CLR pin is

provided to clear the memory and reset the location counter.

The Random Access mode allows the processor to select the

memory address and display digit for each input word.

The character multiplex scan runs whenever data is not being

entered. It scans the memory and CHARacter drivers, and

ensures that the decoding from memory to display is done in

the proper sequence. Intercharacter blanking is provided to

avoid display ghosting.

Features

• Single supply +3.3V operation

• 16-Segment fonts with decimal point

• Up to 8 character display driver

• Has internal pull-up resistors of 136Ω Typical

• Microprocessor compatible

• Directly drives LED common cathode displays

• Cascadable without additional hardware

• Standby feature turns display off; puts chip in low power

mode

• Sequential entry or random entry of data into display

• Character and segment drivers, All MUX scan circuitry, 8x6

static memory and 64-character ASCll font generator

included on-chip

• Pb-free (RoHS compliant)

Ordering Information

PART NUMBER

(Note 2)

PART MARKING

TEMP. RANGE

(°C)

PACKAGE

(Pb-Free)

PKG. DWG. #

ICM7245AIM44Z

ICM7245 AIM44Z

-25°C to +85°C

44 Ld MQFP

Q44.10x10

ICM7245AIM44ZT (Note 1)

ICM7245 AIM44Z

-25°C to +85°C

44 Ld MQFP (Tape and Reel) Q44.10x10

NOTES:

1. Please refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil

Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for ICM7245. For more information on MSL, please see tech brief TB363.

October 29, 2013

FN8587.0

1

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Copyright Intersil Americas LLC 2013. All Rights Reserved

Intersil (and design) is a trademark owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.

http://www.Datasheet4U.com

1 page

ICM7245

Capacitance

PARAMETER

SYMBOL

TEST CONDITIONS

Input Capacitance

ClN

(Note 7)

Output Capacitance

CO

(Note 7)

NOTES:

6. In Sequential mode WR high must be ≥ TSEN +TWDF.

7. For design reference only, not tested.

Timing Waveforms

MIN

-

-

CS

tCS

ADDRESS

WRITE

DATA

tAH

tAS

VALID

tWC

tWPI

tWHP

tDS tT

tT tDH

VALID

FIGURE 1. RANDOM ACCESS TIMING

TYP

5

5

MAX

-

-

UNITS

pF

pF

WR

CLEAR

CHAR

1

tSEN

CHAR

2

CHAR

8

tWPH

SEN

DISPLAY FULL

FIGURE 2. SEQUENTIAL ACCESS MODE TIMING (MODE = 1)

tWDF

5 FN8587.0

October 29, 2013

5 Page

ICM7245

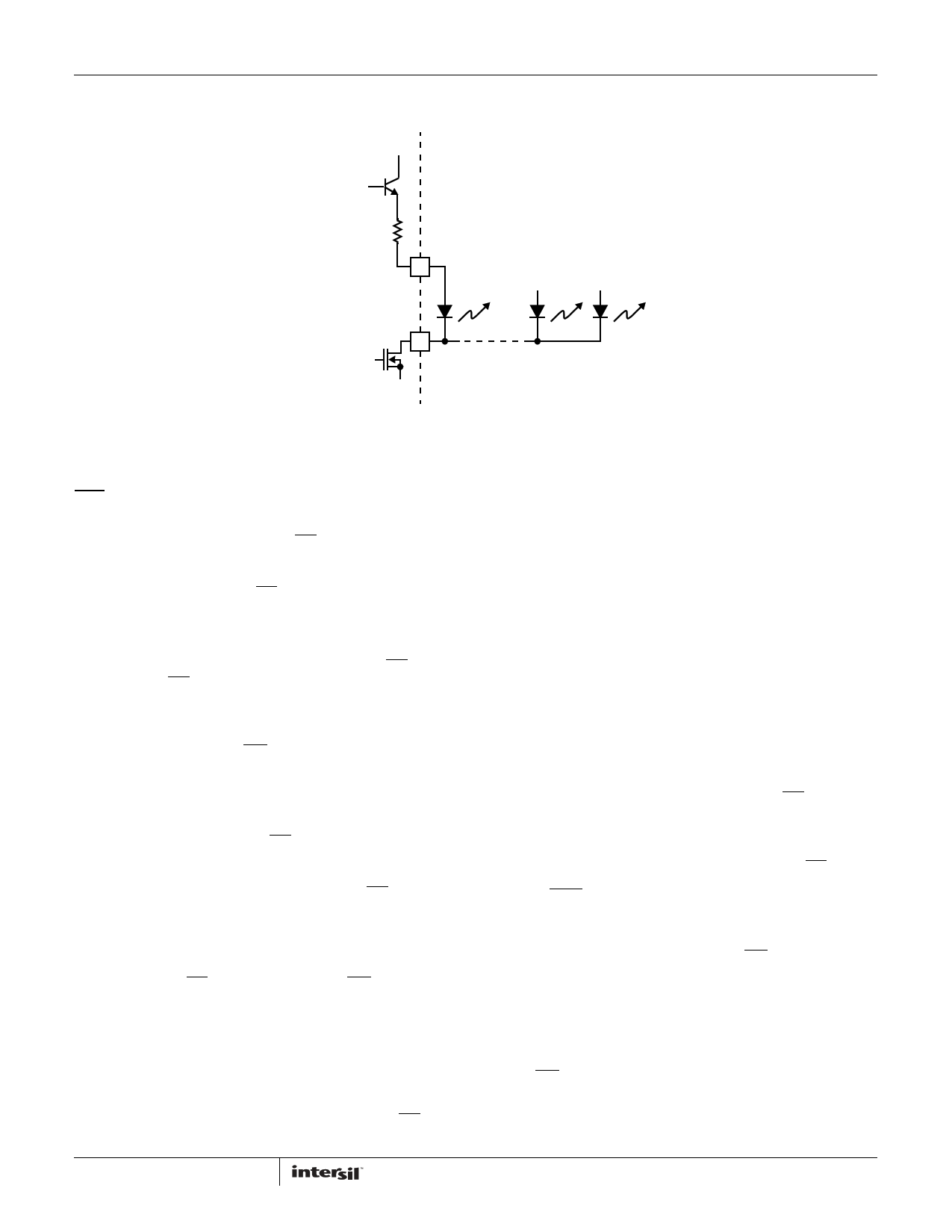

Display Font and Segment Assignments (Continued)

SEGMENT

DRIVER

VDD

VLED = 2V

RTYPICAL =136Ω

R

SEG x DISPLAY

CHARACTER

DRIVER

rDS(ON) ~ 7.4Ω VSS

CHAR N

SEGMENT LEDs

FIGURE 10. SEGMENT AND CHARACTER DRIVERS OUTPUT CIRCUIT

Detailed Description

WR, CS

These pins are immediately functionally ANDed, so all actions

described as occurring on an edge of WR, with CS enabled, will

occur on the equivalent (last) enabling or (first) disabling edge

of any of these inputs. The delays from CS pins are slightly

(about 5ns) greater than from WR due to the additional

inverter required on the former.

MODE

The MODE pin input is latched on the falling edge of WR (or its

equivalent, see WR description). The location (in Data

Memory) where incoming data will be placed is determined

either from the Address pins or the Sequential Address

Counter. This is controlled by MODE input. MODE also controls

the function of A0/SEN, A1/CLR, and A2/DlSPlay FULL lines.

Random Access Mode

When the internal mode latch is set for Random Access (RA)

(MODE latched low), the Address input on A0, A1 and A2 will

be latched by the falling edge of WR (or its equivalent).

Subsequent changes on the Address lines will not affect device

operation. This allows use of a multiplexed 6-bit bus controlling

both address and data, with timing controlled by WR.

Sequential Access Mode

If the internal latch is set for Sequential Access (SA), (MODE

latched high), the Serial ENable input or SEN will be latched on

the falling edge of WR (or its equivalent). The CLR input is

asynchronous, and will force-clear the Sequential Address

Counter to address 000 (CHARacter 1), and set all Data

Memory contents to 100000 (blank) at any time. The DISPlay

FULL output will be active in SA mode to indicate the overflow

status of the Sequential Address Counter. If this output is low,

and SEN is (latched) high, the contents of the Counter will be

used to establish the Data Memory location for the Data input.

The Counter is then incremented on the rising edge of WR. If

SEN is low, or DISPlay FULL is high, no action will occur. This

allows easy “daisy-chaining” of display drivers for multiple

character displays in a Sequential Access mode.

Changing Modes

Care must be exercised in any application involving changing

from one mode to another. The change will occur only on a

falling edge of WR (or its equivalent). When changing mode

from Sequential Access to Random Access, note that

A2/DlSPlay FULL will be an output until WR has fallen low, and

an Address drive here could cause a conflict. When changing

from Random Access to Sequential Access, A1/CLR should be

high to avoid inadvertent clearing of the Data Memory and

Sequential Address Counter. DISPlay FULL will become active

immediately after the rising edge of WR.

Data Entry

The input Data is latched on the rising edge of WR (or its

equivalent) and then stored in the Data Memory location

determined as described above. The six Data bits can be

multiplexed with the Address information on the same lines in

Random Access mode. Timing is controlled by the WR input.

OSC/OFF

The device includes a relaxation oscillator with an internal

capacitor and a nominal frequency of 200kHz. By adding

external capacitance to VDD at the OSC/OFF pin, this

frequency can be reduced as far as desired. Alternatively, an

external signal can be injected on this pin. The oscillator (or

external) frequency is pre-divided by 64, and then further

divided by 8 in the Multiplex Counter, to drive the CHARacter

drive lines (Figure 3). An inter-character blanking signal is

derived from the pre-divider. An additional comparator on the

OSC/OFF input detects a level lower than the relaxation

oscillator's range, and blanks the display, disables the DISPlay

FULL output (if active), and clears the pre-divider and Multiplex

Counter. This puts the circuit in a low-power-dissipation mode

11 FN8587.0

October 29, 2013

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet ICM7245.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICM7240 | (ICM7240 - ICM7260) Fixed And Programmable Timer/Counters | Maxim Integrated Products |

| ICM7242 | Long Range Fixed Timer | Intersil Corporation |

| ICM7242 | (ICM7240 - ICM7260) Fixed And Programmable Timer/Counters | Maxim Integrated Products |

| ICM7243 | LED Display Decoder Driver | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |