|

|

PDF KT0803L Data sheet ( Hoja de datos )

| Número de pieza | KT0803L | |

| Descripción | Monolithic Digital Stereo FM Transmitter | |

| Fabricantes | KTMicro | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de KT0803L (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

Monolithic Digital Stereo FM Transmitter

Radio-Station-on-a-Chip™

KT0803L

Features

Hardware compatible with KT0803K and KT0803M

Additional features to KT0803K and KT0803M

Software standby;

Automatic power down power amplifier

when silence is detected;

Multiple reference clock support

including from 32.768KHz to 26MHz;

ALC (Automatic Level Control)

Higher SNR (Stereo: 66dB)

Increased audio frequency response

Software controlled XTAL selection

Professional Grade Performance:

SNR ≥ 66 dB

Stereo Separation > 40 dB

International compatible 70MHz ~ 108MHz

Ultra-Low Power Consumption:

< 17 mA operation current

< 3 µA standby current

Simple Interface:

Single power supply

Standard 2-wire I2C MCU interface

Advanced Digital Audio Signal Processing:

On-chip 20-bit ΔΣ Audio ADC

On-chip DSP core

On-chip 24dB PGA with optional 1dB step

Automatic calibration against process

and temperature

1.6V ~ 3.6V supply

Programmable transmit level

Programmable pre-emphasis (50/75 µs)

Pb-free and RoHS Compliant

SOP-16 package

Applications

MP3 Player, Cellular Phone, PDA, PND,

Portable Personal Media player and its accessory,

Laptop Computer, Wireless Speaker

Rev. 1.3

Information furnished by KT Micro is believed to be accurate

and reliable. However, no responsibility is assumed by KT

Micro for its use, nor for any infringements of patents or

other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any

patent or patent rights of KT Micro, Inc..

Figure 1: KT0803L System Diagram

General Description

KT0803L, our new generation of low cost Monolithic

Digital FM Transmitter, is designed to process high-fidelity

stereo audio signal and transmit modulated FM signal over

a short range. It’s based on the architecture of award-

winning KT0801 and it’s also an upgrade of KT0803K and

KT0803M. The additional features added to KT0803L are

standby mode through software, ALC(automatic level

control), multiple reference clock, increased SNR

performance and frequency response.

The KT0803L features dual 20-bit ΔΣ audio ADCs, a high-

fidelity digital stereo audio processor and a fully integrated

radio frequency (RF) transmitter. An on-chip low-drop-out

regulator (LDO) allows the chip to be integrated in a wide

range of low-voltage battery-operated systems with power

supply ranging from 1.6V to 3.6V.

The KT0803L is configured as an I2C slave and

programmed through the industry standard 2-wire MCU

interface.

Thanks to its high integration level, the KT0803L is

mounted in a generic 16-pin SOP package. It only requires

a single low-voltage supply. No external tuning is required

that makes design-in effort minimum.

KT Micro Inc., 22391 Gilberto, Suite D

Rancho Santa Margarita, CA 92688

Tel: 949.713.4000 http://www.ktmicro.com

Fax: 949.713.4004 Copyright ©2010, KT Micro, Inc.

Free Datasheet http://www.Datasheet4U.com

1 page

KT0803L

CURRENT ADDRESS READ: The internal data register address counter maintains the last address

accessed during the last read or write operation, incremented by one. This address stays valid between

operations as long as the chip power is maintained.

Once the device address with the read/write select bit set to “1” is clocked in and acknowledged by the

KT0803L, the current address data word is serially clocked out. The microcontroller does not respond with

an input “0” but does generate a following stop condition (see Figure 4).

CURRENT REGISTER READ PROCEDURE

S 0 1 1 1 1 1 0 RA

7 bit address

data

Acknowledge

START condition READ command

AP

STOP condition

NO Acknowledge

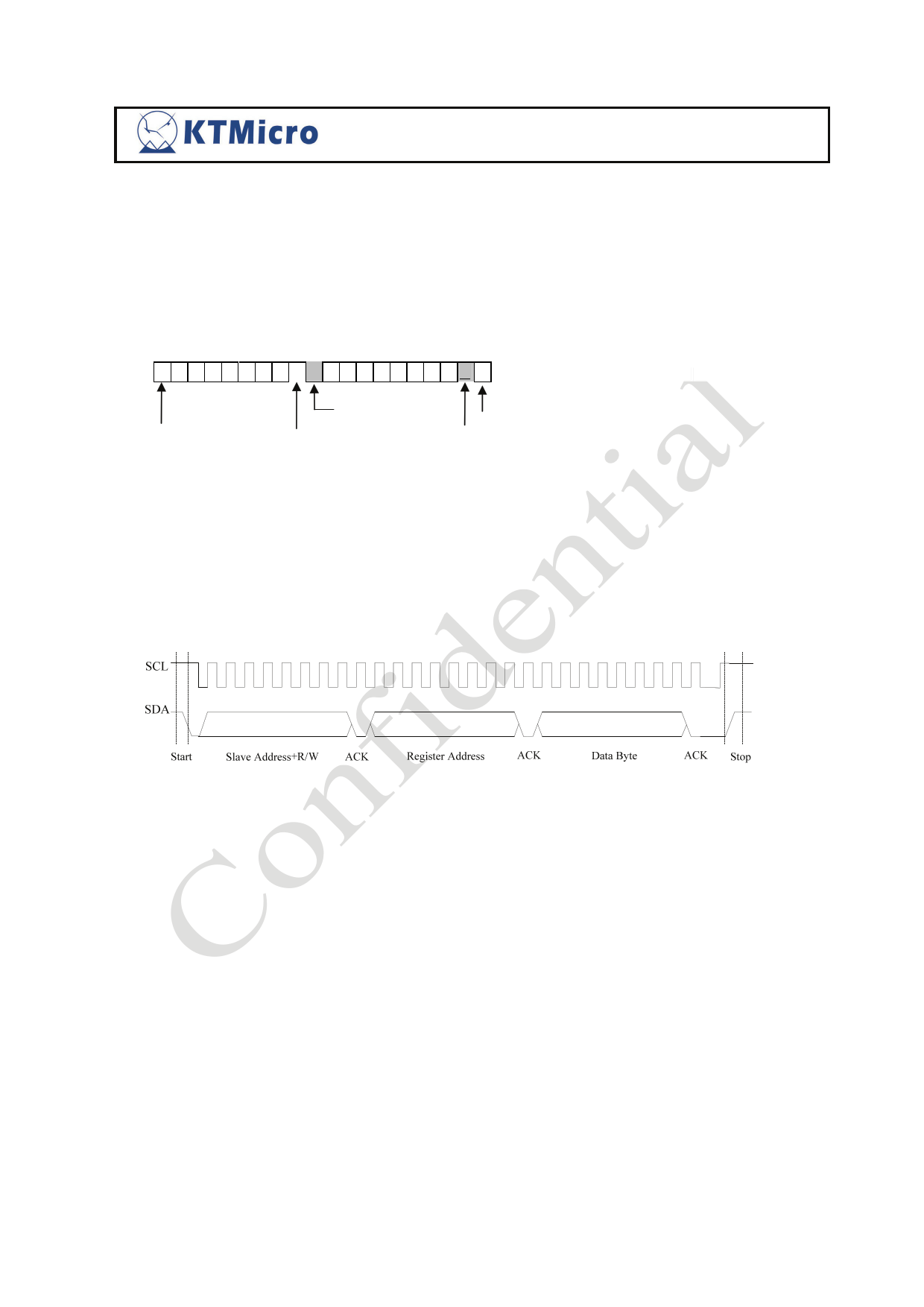

Figure 4: Serial Interface Protocol

Note: The serial controller supports slave mode only. Any register can be addressed randomly.

The address of the slave in the first 7 bits and the 8th bit tells whether the master is receiving data from the

slave or transmitting data to the slave. The I2C write address is 0x7C and the read address is 0x7D.

3.2 Slave Mode Protocol

With reference to the clocking scheme shown in Figure 5, the serial interface operates in the following

manner:

Figure 5: Serial Interface Slave Mode Protocol

CLOCK and DATA TRANSITIONS: The SDA pin is normally pulled high with an external device. Data

on the SDA pin may change only during SCL low time periods (see Figure 6). Data changes during SCL

high periods will indicate a start or stop condition as defined below.

START CONDITION: A high-to-low transition of SDA with SCL high is a start condition which must

precede any other command (see Figure 7).

STOP CONDITION: A low-to-high transition of SDA with SCL high is a stop condition. After a read

sequence, the stop command will place the KT0803L in a standby power mode (see Figure 7).

ACKNOWLEDGE: All addresses and data words are serially transmitted to and from the KT0803L in 8-

bit words. The KT0803L sends a “0” to acknowledge that it has received each word. This happens during

the ninth clock cycle (see Figure 8).

Copyright ©2010, KT Micro, Inc.

5

Free Datasheet http://www.Datasheet4U.com

5 Page

KT0803L

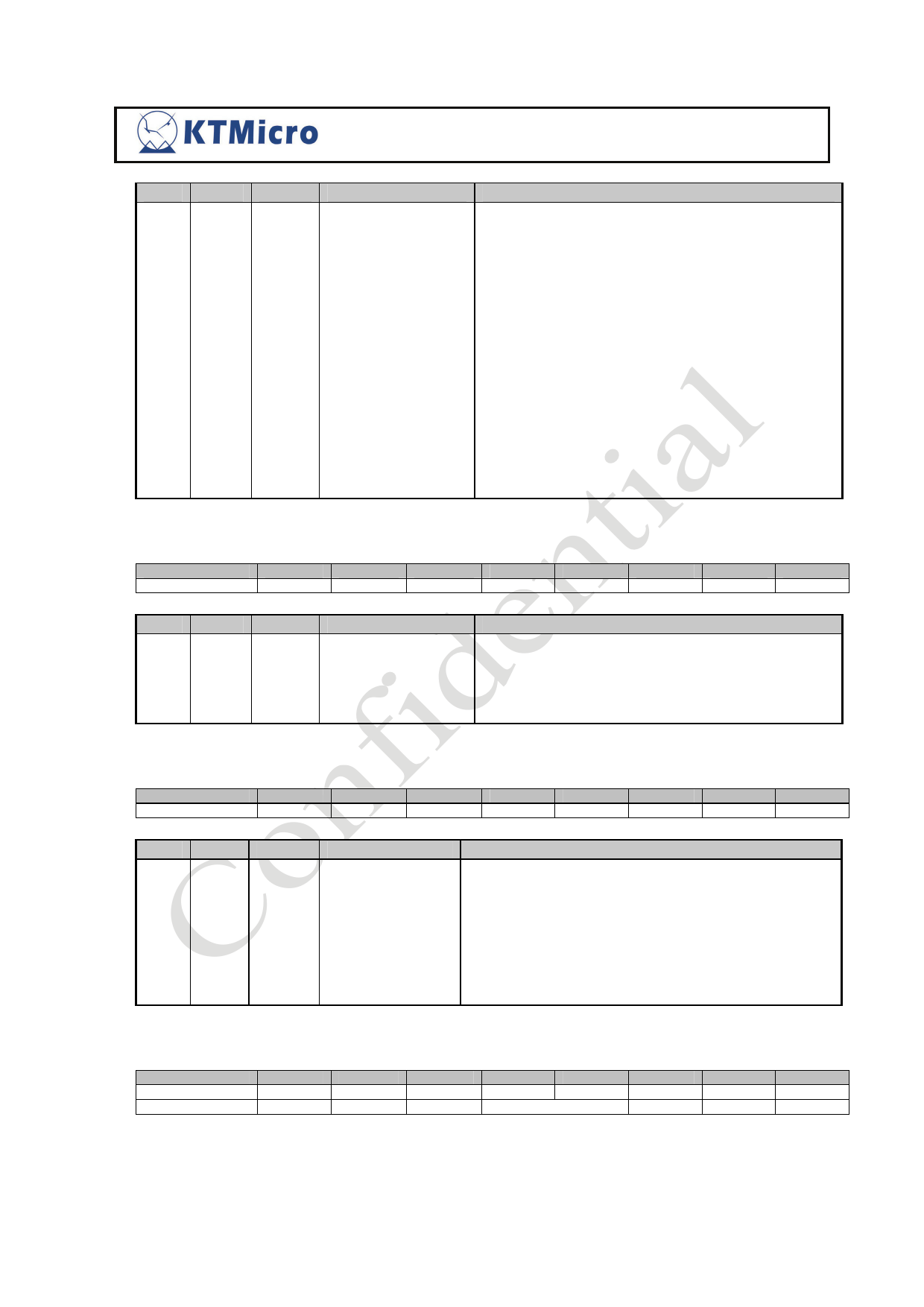

Bits Type Default Label

Description

3:0 RW 0000 ALC_ATTACK_TIM ALC Attack Time Selection

E[3:0]

0000 = 25us

0001 = 50us

0010 = 75us

0011 = 100us

0100 = 125us

0101 = 150us

0110 = 175us

0111 = 200us

1000 = 50ms

1001 = 100ms

1010 = 150ms

1011 = 200ms

1100 = 250ms

1101 = 300ms

1110 = 350ms

1111 = 400ms

4.7 Register 0x0E (Address: 0x0E, Default: 0x02)

Bit 7 6 5 4

KT0803L - - - -

3

-

21

- PA_BIAS

Bits Type Default Label

7:2 RW 0x00 Reserved

1 RW 1

PA_BIAS

0 RW 0

Reserved

Description

Reserved

PA Bias Current Enhancement.

0 = Disable PA bias

1 = Enable PA bias

Reserved

0

-

4.8 Register 0x0F (Address: 0x0F, Read only)

Bit 7 6 5 4 3 2

KT0803L - - - PW_OK - SLNCID

Bits Type Default Label

7 R NA Reserved

6 R NA Reserved

5 R NA Reserved

4 R NA PW_OK

3 R NA Reserved

2 R NA SLNCID

1 R NA Reserved

0 R NA Reserved

Description

Reserved

Reserved

Reserved

Power OK Indicator

Reserved

1 when Silence is Detected

Reserved

Reserved

1

-

0

-

4.9 Register 0x10 (Address: 0x10, Default: 0xA8)

Bit 7 6 5 4 3 2 1 0

KT0803L - - - - - - - PGAMOD

KT0803K/M

-

-

-

LMTLVL[1:0]

- - PGAMOD

Copyright ©2010, KT Micro, Inc.

11

Free Datasheet http://www.Datasheet4U.com

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet KT0803L.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KT0803K | Monolithic Digital Stereo FM Transmitter | KTMicro |

| KT0803L | Monolithic Digital Stereo FM Transmitter | KTMicro |

| KT0803M | Monolithic Digital Stereo FM Transmitter | KTMicro |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |