|

|

PDF K4J52324QE Data sheet ( Hoja de datos )

| Número de pieza | K4J52324QE | |

| Descripción | 512Mbit GDDR3 SDRAM | |

| Fabricantes | Samsung | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de K4J52324QE (archivo pdf) en la parte inferior de esta página. Total 58 Páginas | ||

|

No Preview Available !

K4J52324QE

512M GDDR3 SDRAM

512Mbit GDDR3 SDRAM

Revision 1.3

Feb 2008

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS,

AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE,

EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE,

TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL

INFORMATION IN THIS DOCUMENT IS PROVIDED

ON AS "AS IS" BASIS WITHOUT GUARANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar

applications where Product failure could result in loss of life or personal or physical harm, or any military or

defense application, or any governmental procurement to which special terms or provisions may apply.

* Samsung Electronics reserves the right to change products or specification without notice.

- 1/58 -

Rev. 1.3 Feb 2008

Free Datasheet http://www.datasheetlist.com/

1 page

K4J52324QE

512M GDDR3 SDRAM

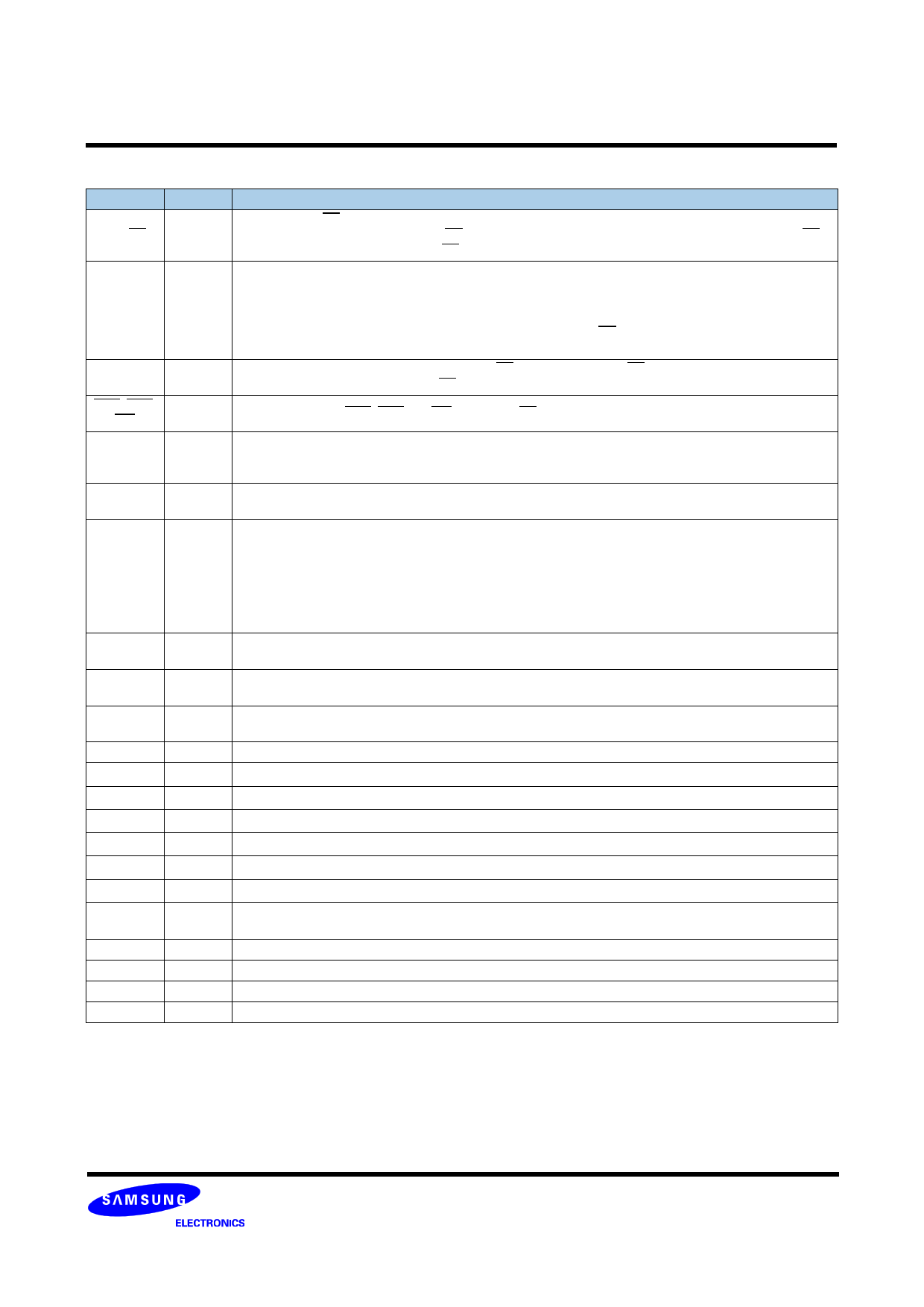

5.0 INPUT/OUTPUT FUNCTIONAL DESCRIPTION

Symbol

CK, CK

CKE

CS

RAS, CAS,

WE

DM0

~DM3

BA0 ~ BA2

A0 ~ A11

DQ0

~ DQ31

RDQS0

~ RDQS3

WDQS0

~ WDQS3

NC/RFU

VDDQ

VSSQ

VDD

VSS

VDDA

VSSA

VREF

MF

ZQ

RES

SEN

Type

Input

Input

Input

Function

Clock: CK and CK are differential clock inputs. CMD, ADD inputs are sampled on the crossing of the posi-

tive edge of CK and negative edge of CK. Output (read) data is referenced to the crossings of CK and CK

(both directions of crossing). CK and CK should be maintained stable except self-refresh mode.

Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buff-

ers and output drivers. Taking CKE Low provides Precharge Power-Down and Self Refresh operation (all

banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for power down entry and

exit, and for self refresh entry. CKE is asynchronous for self refresh exit. CKE must be maintained high

throughout read and write accesses. Input buffers, excluding CK, CK and CKE are disabled during power-

down. Input buffers, excluding CKE, are disabled during self refresh.

Chip Select: All commands are masked when CS is registered HIGH. CS provides for external bank selec-

tion on systems with multiple banks. CS is considered part of the command code.

Input Command Inputs: RAS, CAS and WE (along with CS) define the command being entered.

Input

Input

Input

Input/

Output

Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled

HIGH coincident with that input data during a Write access. DM is sampled on both edges of clock. Although

DM pins are input only, the DM loading matches the DQ and WDQS loading.

Bank Address Inputs: BA0, BA1 and BA2 define to which bank an Active, Read, Write or Precharge com-

mand is being applied.

Address Inputs: Provided the row address for Active commands and the column address and Auto Pre-

charge bit for Read/Write commands to select one location out of the memory array in the respective bank.

A8 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A8

LOW) or all banks (A8 HIGH). If only one bank is to be precharged, the bank is selected by BA0, BA1,BA2.

The address inputs also provide the op-code during Mode Register Set commands.

Row addresses : RA0 ~ RA11, Column addresses : CA0 ~ CA7, CA9 . Column address CA8 is used for auto

precharge.

Data Input/ Output: Bi-directional data bus.

Output READ Data Strobe: Output with read data. RDQS is edge-aligned with read data.

Input WRITE Data Strobe: Input with write data. WDQS is center-aligned to the inout data.

No Connect: No internal electrical connection is present.

Supply DQ Power Supply

Supply DQ Ground

Supply Power Supply

Supply Ground

Supply DLL Power Supply

Supply DLL Ground

Supply

Reference voltage: 0.7*VDDQ ,

2 Pins : (H12) for Data input , (H1) for CMD and ADDRESS

Input Mirror Function for clamshell mounting of DRAMs. VDDQ CMOS input.

Reference Resistor connection pin for On-die termination.

Input Reset pin: RESET pin is a VDDQ CMOS input

Input Scan enable : Must tie to the ground in case not in use. VDDQ CMOS input.

- 5/58 -

Rev. 1.3 Feb 2008

Free Datasheet http://www.datasheetlist.com/

5 Page

K4J52324QE

512M GDDR3 SDRAM

CAS LATENCY (READ LATENCY)

The CAS latency is the delay, in clock cycles, between the registration of a READ command and the availability of the first bit of output

data. The latency can be set to 4~11 clocks. If a READ command is registered at clock edge n, and the latency is m clocks, the data will

be available nominally coincident with clock edge n+m. Below table indicates the operating frequencies at which each CAS latency set-

ting can be used. Reserved states should not be used as unknown operation or incompatibility with future versions may result.

SPEED

-BJ1A

-BJ11

-BC12

-BC14

CL=12

≤ 1000

CL=11

≤ 900

≤ 800

CAS Latency

Allowable operating frequency (MHz )

CL=10

CL=9

--

≤ 700

-

CL=8

-

-

CL=7

-

-

T0

/CK

CK

COMMAND

READ

0

RDQS

DQ

T5 T6

NOP

CL = 7

NOP

T7 T7n

NOP

/CK

CK

COMMAND

RDQS

DQ

T0

READ

T6 T7

NOP

CL = 8

NOP

T8 T8n

NOP

Burst Length = 4 in the cases shown

Shown with nominal tAC and nominal tDSDQ

DON’T CARE

TRANSITIONING DATA

- 11/58 -

Rev. 1.3 Feb 2008

Free Datasheet http://www.datasheetlist.com/

11 Page | ||

| Páginas | Total 58 Páginas | |

| PDF Descargar | [ Datasheet K4J52324QE.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K4J52324QE | 512Mbit GDDR3 SDRAM | Samsung |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |