|

|

PDF DAP011C Data sheet ( Hoja de datos )

| Número de pieza | DAP011C | |

| Descripción | PWM Current-Mode Controller | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DAP011C (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

Customer Specific Device from ON Semiconductor

DAP011/DAP011C

PWM Current−Mode

Controller for High−Power

Universal Off−Line Supplies

Housed in an SO−14 package, the DAP011/DAP011C

represents an enhanced version of the Maximus, DAP008,

controller. Due to its high drive capability, SpeedKing drives

large gate−charge MOSFETs which, together with internal

ramp compensation and a user selectable frequency

jittering, ease the design of modern AC/DC adapters.

With an internal structure operating at a fixed 65/100 kHz

frequency, the controller directly connects to the

high−voltage rail for a loss less and clean startup sequence.

Current−mode control also provides an excellent input

audio−susceptibility and inherent pulse−by−pulse control.

Internal ramp compensation easily prevents subharmonic

oscillations from taking place in continuous conduction

mode designs.

When the current setpoint falls below a given value, e.g. the

output power demand diminishes, the IC automatically enters

the so−called skip cycle mode and provides excellent

efficiency at light loads. Because this occurs at a user

adjustable low peak current, no acoustic noise takes place. Due

to a proprietary SoftSkip technique, the absence of sharp

transitions during skip mode significantly reduces acoustical

noise.

The DAP011/DAP011C features an efficient protective

circuitry which, in presence of an overcurrent condition,

disables the output pulses while the device enters a safe burst

mode, trying to restart. Once the default has gone, the device

auto−recovers. By implementing a timer to acknowledge a

fault condition, independently from the auxiliary supply, the

designer’s task is eased when stringent fault mode

conditions need to be met.

A dedicated input helps triggering a latch−off circuitry

which permanently disables output pulses.

Features

• Current−Mode Control with Adjustable Skip−Cycle

Capability

• Internal Ramp Compensation

• Adjustable Frequency Jittering for Better EMI

Signature

• Auto−Recovery Internal Output Short−Circuit

Protection

• Adjustable Timer for Improved Short−Circuit

Protection

• Dedicated Latch Input

• +500 mA/−800 mA Peak Current Capability

• Fixed Frequency Versions at 65/100 kHz

• 5.0 V – 5.0 mA Reference Voltage

• Internal Temperature Shutdown

• Direct Optocoupler Connection

• Extremely Low No−Load Standby Power

• Adjustable Soft−Start

• This is a Pb−Free Device*

Typical Applications

• High Power AC/DC Converters for TVs, Set−Top

Boxes, etc.

• Offline Adapters for Notebooks

• All Power Supplies

14

1

MARKING

DIAGRAM

14

SOIC−14

D SUFFIX

CASE 751A

DAP011/DAP011C

AWLYWWG

1

A = Assembly Location

WL = Wafer Lot

Y = Year

WW = Work Week

G = Pb−Free Package

PIN CONNECTIONS

NC

LATCH

CTIMER

JITTER

SKIP

FB

CS

1

2

3

4

5

6

7

14

HV

13 NC

12 NC

11 REF

10

VCC

9 DRV

8

GND

(Top View)

Device

DAP011

DAP011C

ORDERING INFORMATION

fosc

Package

Shipping†

(65 kHz)

(100 kHz)

SO−14 2500 / Tape & Reel

(Pb−Free)

†For information on tape and reel specifications, including part

orientation and tape sizes, please refer to our Tape and Reel

Packaging Specifications Brochure, BRD8011/D.

*For additional information on our Pb−Free strategy and soldering

details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

© Semiconductor Components Industries, LLC, 2005

November, 2005 − Rev. 2

1

Publication Order Number:

DAP011/D

Free Datasheet http://www.datasheet4u.com/

1 page

DAP011/DAP011C

ELECTRICAL CHARACTERISTICS (For typical values TJ = 25°C, for min/max values TJ = −5°C to +125°C, Max TJ = 150°C,

VCC = 12 V unless otherwise noted.)

Characteristic

Symbol

Pin Min

Typ

Max Unit

SUPPLY SECTION

VCC Increasing Level at which the Current Source Turns−Off

VCCON

10 11.8 12.8

VCC Level at which Output Pulses are Stopped

VCC(min) 10 8.0 9.0

VCC Decreasing Level at which the Latch−Off Phase Ends

VCClatch

10

−

6.5

Internal Latch Reset Level

VCCreset

10

−

5.0

Minimum Voltage Difference between VCClatch and VCCReset

resetHyst − 1.0

−

Internal IC Consumption, No Output Load on Pin 9

DAP011

DAP011C

ICC1

10 − 1.2

− 1.3

13.8 V

10 V

−V

−V

−V

− mA

−

Internal IC Consumption, 1.0 nF Output Load on Pin 9

DAP011

DAP011C

ICC2

10 − 1.9

− 2.5

− mA

−

Internal IC Consumption, Latch−Off Phase

ICC3

10

−

Reference Voltage, Iout = 1.0 mA, TJ = 25°C

Vref1

11 4.9 5.0

Reference Voltage, Iout = 5.0 mA

Vref2

11 4.8

−

Maximum Output Current Capability

IrefOut

11 5.0

−

Decoupling Capacitor Connected to Pin 11

Cref

11 100

−

INTERNAL STARTUP CURRENT SOURCE (TJ > −5°C) – High−voltage pin biased to 60 V DC.

High−Voltage Current Source, VCC = 10 V (Note 4)

IC2 14 2.0 4.0

High−Voltage Current Source, VCC = 0

IC1 14 200 500

VCC Transition Level for IC1 to IC2 Toggling Point

VTh 14 − 1.8

Leakage Current for the High Voltage Source, Vpin 14 = 250 Vdc

Ileak

14 −

35

DRIVE OUTPUT (Lothar like)

0.6 mA

5.1 V

5.13 V

− mA

− nF

− mA

650 mA

−V

− mA

Output Voltage Rise−Time @ CL = 1.0 nF, 10−90% of a 12 V Output Signal

Output Voltage Fall−Time @ CL = 1.0 nF, 10−90% of a 12 V Output Signal

Source Resistance

Sink Resistance

CURRENT COMPARATOR

Tr

Tf

ROH

ROL

9 − 40

9 − 15

9 − 12

9 − 7.0

− ns

− ns

−W

−W

Input Bias Current @ 1.0 V Input Level on Pin 7

Maximum Internal Current Setpoint – TJ = 25°C

Maximum Internal Current Setpoint – TJ from −5° to 125°C

Default Internal Voltage Setpoint for Skip Cycle Operation

Propagation Delay from Current Detection to Gate OFF State

Leading Edge Blanking Duration

Soft−Start Duration, Ctimer = 0.22 mF

INTERNAL OSCILLATOR

IIB

ILimit1

ILimit2

VLskip

TDEL

TLEB

TSS

7 − 0.02

7 0.95 1.0

7 0.93 1.0

7 − 350

7 − 100

7 − 200

− − 10

− mA

1.05 V

1.07 V

− mV

150 ns

− ns

− ms

Oscillation Frequency

DAP011

DAP011C

fOSC

− 60 65

70 kHz

92 100

108

Maximum Duty−Cycle

Frequency Jittering in Percentage of fOSC

DAP011

DAP011C

Dmax

fjitter

− 76 80

84 %

− − "5.0 − %

− "6.0

−

Swing Frequency with a 22 nF Capacitor to Pin 4

Jittering Modulator Charging Current

Jittering Capacitor Peak Voltage

Jittering Capacitor Valley Voltage

4. Min. value for TJ = 125°C (See Figure 10).

fswing

ICjit

VCjitP

VCjitV

4 − 300

4 − 20

4 − 2.15

4 − 0.75

− Hz

− mA

−V

−V

http://onsemi.com

5

Free Datasheet http://www.datasheet4u.com/

5 Page

DAP011/DAP011C

Startup Sequence

When the power supply is first connected to the mains

outlet, the internal current source is biased and charges up

the VCC capacitor. When the voltage on this VCC capacitor

reaches the VCCON level (typically 12.8 V), the current

source turns off, reducing the amount of power being

dissipated. At this time, the VCC capacitor only supplies the

controller, and the auxiliary supply should take over before

VCC collapses below VCC(min). Figure 20 shows the internal

arrangement of this structure:

and IC2. At power−up, as long as VCC is below a certain

level (1.8 V typical), the source delivers IC1 (around

500 mA typical), then, when VCC reaches 1.8 V, the source

smoothly transitions to IC2 and delivers its nominal value.

As a result, in case of short−circuit between VCC and GND,

the power dissipation will drop to 370 x 500 m = 185 mW.

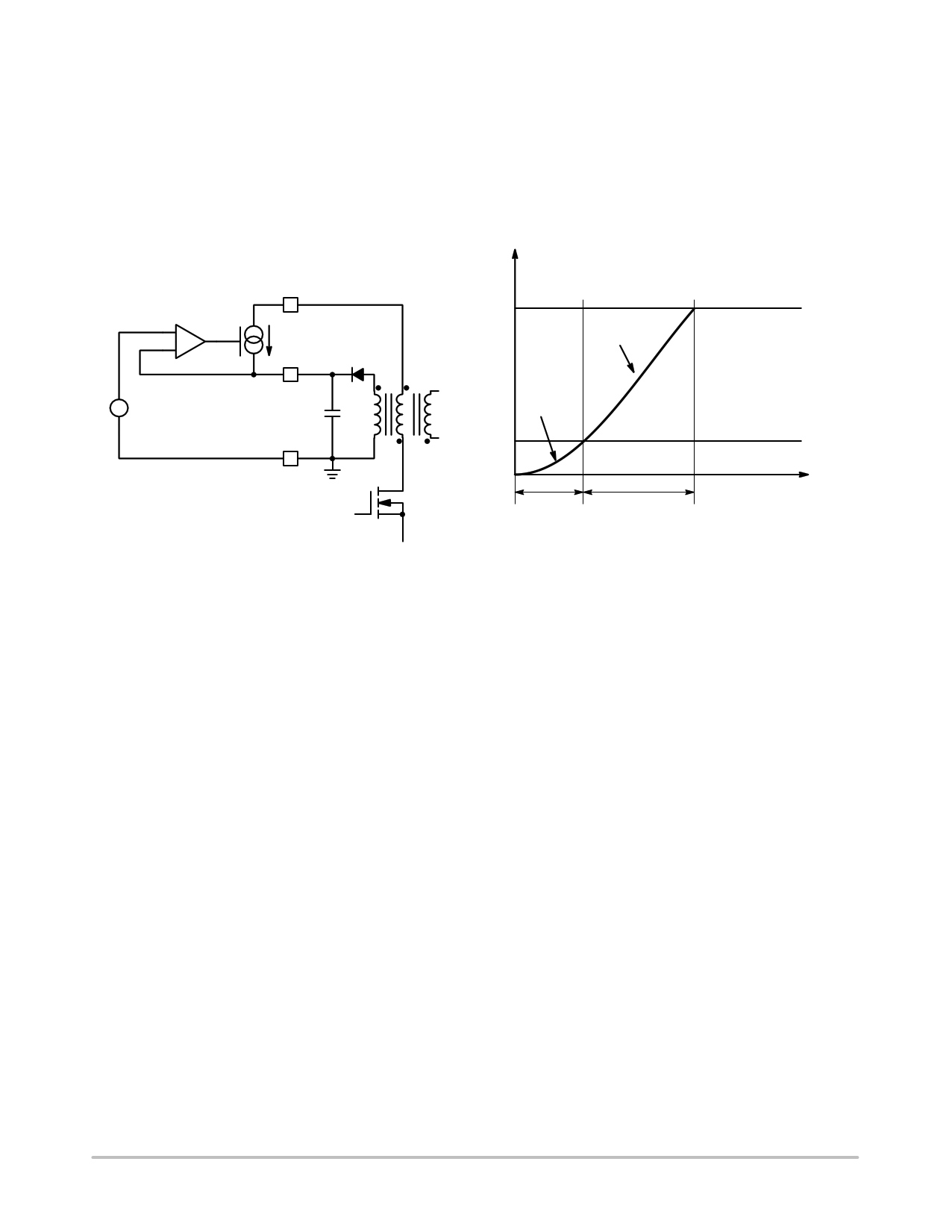

Figure 21 portrays this particular behavior:

VCC

+

−

+ VCC ON

VCC latch

14

IC1 or 0

10

HV

8

IC2 min

IC1 min

VCCON

CVCC = 22 mF

Vth

Figure 20. The Current Source brings VCC above 15 V

and then turns off

In some fault situations, a short−circuit can purposely

occur between VCC and GND. In high line conditions

(VHV = 370 VDC) the current delivered by the startup

device will seriously increase the junction temperature. For

instance, since IC1 equals 2 mA (the minimum corresponds

to the highest Tj), the device would dissipate

370 x 2 m = 740 mW. To avoid this situation, the controller

includes a novel circuitry made of two startup levels, IC1

t1 t2

Figure 21. The Startup Source Now Features a Dual

Level Startup Current

The first startup period is calculated by the formula C x V

= I x t, which implies a 22 m x 1.5 / 350 m = 94ms startup time

for the first sequence. The second sequence is obtained by

changing to 2 mA with a DV of VCCON – VCCth = 12.8 – 1.5

= 11.3 V, which finally leads to a second startup time of 12.8

x 22 m / 2 m = 140 ms. The total startup time becomes 94 m

+ 140 m = 235 ms. Please note that this calculation is

approximated by the presence of the knee in the vicinity of

the transition.

http://onsemi.com

11

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet DAP011C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DAP011 | PWM Current-Mode Controller | ON Semiconductor |

| DAP011C | PWM Current-Mode Controller | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |