|

|

PDF DS3508 Data sheet ( Hoja de datos )

| Número de pieza | DS3508 | |

| Descripción | 8-Channel Gamma Buffer | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de DS3508 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

Rev 1; 3/08

I2C, 8-Channel Gamma Buffer with EEPROM

General Description

The DS3508 is a programmable 8-channel gamma volt-

age generator with one byte of on-chip EEPROM and

one byte of SRAM memory per channel. Each channel

is composed of an independent 8-bit DAC with an asso-

ciated EEPROM/SRAM pair. At power-up, nonvolatile

(NV) EEPROM gamma data is loaded into its corre-

sponding SRAM register that drives the associated 8-bit

DAC. An on-chip control register allows selectable con-

trol of writing to SRAM/EEPROM or SRAM only.

The DS3508 is designed for low-power operation and

draws less than 2mA (typ) from the VDD supply.

Programming occurs through an I2C-compatible serial

interface with support for speeds up to 400kHz.

TFT-LCD Gamma Buffer

Industrial Controls

Applications

Typical Operating Circuit

Features

o 8-Bit Gamma DACs, 8 Channels

o 1 Byte EEPROM and 1 Byte SRAM per Channel

o Ultra-Low Power (2mA IDD, typ)

o 400kbps I2C Interface

o 9.0V to 15.5V Analog Supply

o 2.7V to 5.5V Digital Supply

o 20-Pin TSSOP Package

o Address Pin Allows Two DS3508s to Reside on

the Same I2C Bus

Ordering Information

PART

TEMP RANGE

DS3508E+

-45°C to +95°C

DS3508E+T&R

-45°C to +95°C

+Denotes a lead-free package.

T&R = Tape and reel.

PIN-PACKAGE

20 TSSOP

20 TSSOP

Pin Configuration

TOP VIEW

5.0V

I2C

MASTER

15.0V

14.8V 8.0V

VCC VDD

SDA

SCL

A0

GND

VHH VHM

GM1

GM2

GM3

GM4

DS3508

VLL

GM5

GM6

GM7

GM8

VLM

0.2V 7.0V

8

SOURCE DRIVER

LIQUID-CRYSTAL

DISPLAY

SCL 1

SDA 2

GND 3

A0 4

VHH 5

VHM 6

VLM 7

VLL 8

VDD 9

N.C. 10

DS3508

TSSOP

20 VCC

19 GM1

18 GM2

17 GM3

16 GM4

15 GM5

14 GM6

13 GM7

12 GM8

11 N.C.

________________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

Free Datasheet http://www.datasheet4u.com/

1 page

I2C, 8-Channel Gamma Buffer with EEPROM

Typical Operating Characteristics (continued)

(VDD = 15.0V, VCC = 5.0V, TA = +25°C, unless otherwise noted.)

ANALOG SUPPLY CURRENT

vs. TEMPERATURE

4.0

3.5

3.0

2.5

2.0

1.5

1.0

0.5

0

-45 -25 -5 15 35 55 75 95

TEMPERATURE (°C)

GAMMA OUTPUT vs. SETTING

15

12

VDD = 15.0V

VHH = 14.8V

9 VHM = 8.0V

VLM = 7.0V

VLL = 0.2V

6

GM1–GM4

3 GM5–GM8

0

0 32 64 96 128 160 192 224 256

GAMMA SETTING (DEC)

GAMMA OFFSET vs. TEMPERATURE

10

8

6 GM1 = VHH = 14.5V

4

GM1 = VHH = 12.0V

2

0

-2 GM8 = VLM = 8.5V

-4 GM8 = VLL = 0.5V

-6

GM1 = VHM = 6.5V

-8

-10

-45 -25 -5 15 35 55 75 95

TEMPERATURE (°C)

1.00

VDD = 15.0V

0.75 VHH = 14.8V

VHM = 8.0V

0.50

GM1 DNL

0.25

0

-0.25

-0.50

-0.75

-1.00

0

32 64 96 128 160 192 224 256

GAMMA SETTING (DEC)

1.00

VDD = 15.0V

0.75 VHH = 14.8V

VHM = 8.0V

0.50

GM1 INL

0.25

0

-0.25

-0.50

-0.75

-1.00

0

32 64 96 128 160 192 224 256

GAMMA SETTING (DEC)

1.00

VDD = 15.0V

0.75 VLM = 7.0V

VLL = 0.2V

0.50

GM8 DNL

0.25

0

-0.25

-0.50

-0.75

-1.00

0

32 64 96 128 160 192 224 256

GAMMA SETTING (DEC)

1.00

VDD = 15.0V

0.75 VLM = 7.0V

VHM = 0.2V

0.50

GM8 INL

0.25

0

-0.25

-0.50

-0.75

-1.00

0

32 64 96 128 160 192 224 256

GAMMA SETTING (DEC)

_______________________________________________________________________________________ 5

Free Datasheet http://www.datasheet4u.com/

5 Page

I2C, 8-Channel Gamma Buffer with EEPROM

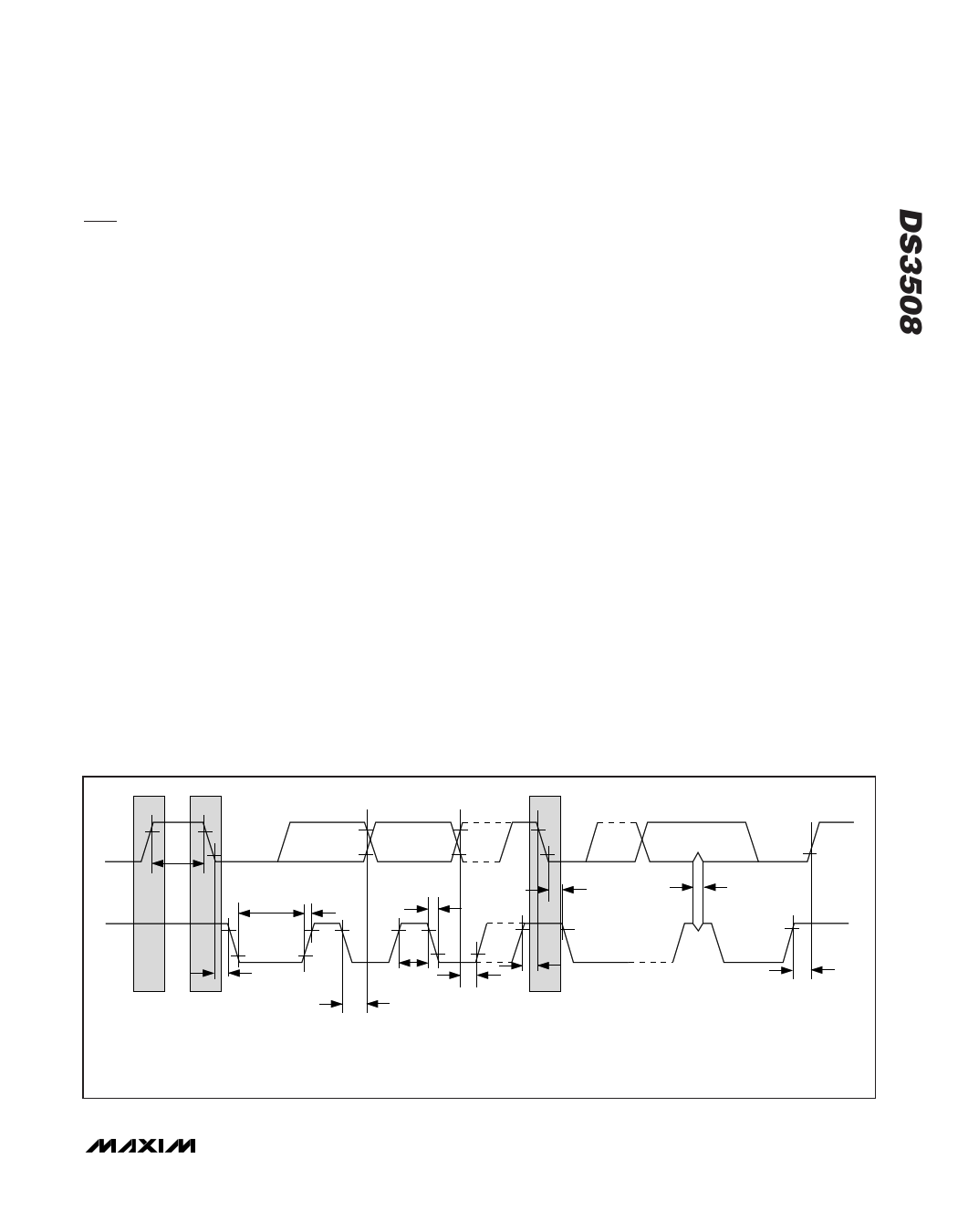

I2C Serial Interface Description

I2C Definitions

The following terminology is commonly used to describe

I2C data transfers. (See Figure 4 and the I2C Electrical

Characteristics table for additional information.)

Master device: The master device controls the slave

devices on the bus. The master device generates SCL

clock pulses and START and STOP conditions.

Slave devices: Slave devices send and receive data at

the master’s request.

Bus idle or not busy: Time between STOP and START

conditions when both SDA and SCL are inactive and in

their logic-high states.

START condition: A START condition is generated by

the master to initiate a new data transfer with a slave.

Transitioning SDA from high to low while SCL remains

high generates a START condition.

STOP condition: A STOP condition is generated by

the master to end a data transfer with a slave.

Transitioning SDA from low to high while SCL remains

high generates a STOP condition.

Repeated START condition: The master can use a

repeated START condition at the end of one data trans-

fer to indicate that it will immediately initiate a new data

transfer following the current one. Repeated STARTS are

commonly used during read operations to identify a spe-

cific memory address to begin a data transfer. A repeat-

ed START condition is issued identically to a normal

START condition.

Bit write: Transitions of SDA must occur during the low

state of SCL. The data on SDA must remain valid and

unchanged during the entire high pulse of SCL plus the

setup and hold time requirements. Data is shifted into the

device during the rising edge of the SCL.

Bit read: At the end of a write operation, the master

must release the SDA bus line for the proper amount of

setup time before the next rising edge of SCL during a

bit read. The device shifts out each bit of data on SDA at

the falling edge of the previous SCL pulse and the data

bit is valid at the rising edge of the current SCL pulse.

Remember that the master generates all SCL clock puls-

es, including when it is reading bits from the slave.

Acknowledge (ACK and NACK): An Acknowledge

(ACK) or Not Acknowledge (NACK) is always the 9th bit

transmitted during a byte transfer. The device receiving

data (the master during a read or the slave during a

write operation) performs an ACK by transmitting a 0

during the 9th bit. A device performs a NACK by trans-

mitting a 1 during the 9th bit. Timing for the ACK and

NACK is identical to all other bit writes. An ACK is the

acknowledgment that the device is properly receiving

data. A NACK is used to terminate a read sequence or

indicates that the device is not receiving data.

Byte write: A byte write consists of 8 bits of information

transferred from the master to the slave (most signifi-

cant bit first) plus a 1-bit acknowledgment from the

slave to the master. The 8 bits transmitted by the mas-

ter are done according to the bit write definition and the

acknowledgment is read using the bit read definition.

SDA

tBUF

SCL

STOP

START

tLOW

tHD:STA

tR tF

tHD:STA

tHD:DAT

tHIGH

tSU:DAT

tSU:STA

REPEATED

START

tSP

tSU:STO

NOTE: TIMING IS REFERENCED TO VIL(MAX) AND VIH(MIN).

Figure 4. I2C Timing Diagram

______________________________________________________________________________________ 11

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet DS3508.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS3501 | I2C POT | Maxim Integrated |

| DS3502 | I2C POT | Maxim Integrated |

| DS3503 | Stepper Potentiometer | Maxim Integrated |

| DS3508 | 8-Channel Gamma Buffer | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |