|

|

PDF UPC3250T7L Data sheet ( Hoja de datos )

| Número de pieza | UPC3250T7L | |

| Descripción | SiGe CMOS/BiCMOS Integrated Circuit | |

| Fabricantes | Renesas | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPC3250T7L (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

PreliminaryData Sheet

μPC3250T7L

SiGe CMOS/BiCMOS Integrated Circuit

IF Down-converter MMIC for Ku-band LNB Converter

R09DS0052EJ0100

Rev.1.00

Oct 23, 2012

DESCRIPTION

The μPC3250T7L is a CMOS/BiCMOS MMIC for Ku-band LNB converter.

This device is housed in a 24-pin plastic QFN (Quad Flat Non-Leaded) (T7L) package.

FEATURES

• Low power consumption

: 3.3 V/63 mA, 208 mW

• Switched LO frequency

: 9.75 G Hz, 10.6 GHz, 10.75 GHz

• 2 step Gain selected function : 41 dB/36 dB

• Low noise figure

: 7.5 dB

• Fully integrated Mixer/Oscillator/PLL synthesizer/IF Amplifier/4-channel FET bias supply circuit/

Polarity control voltage detector/Tone control signal detector

• Integrated power save detector

• 24-pin plastic QFN (T7L) package (4.0 × 4.0 × 0.6 mm)

APPLICATIONS

• Ku-band Low Noise Block (LNB) converters for satellite receiver (DVB-S, ABS-S application)

ORDERING INFORMATION

Part Number

Order Number

Package

Marking

Supplying Form

μPC3250T7L-E1

μPC3250T7L-E1-A 24-pin plastic QFN

(0.5 mm pitch)

(Pb-Free)

C3250

• Embossed tape 12 mm wide

• Pin 7 to 12 face the perforation side of the tape

• Qty 5 kpcs/reel

• Dry packing specification (MSL 3 Equivalent)

Remark To order evaluation samples, please contact your nearby sales office.

Part number for sample order: μPC3250T7L

CAUTION

Observe precautions when handling because these devices are sensitive to electrostatic discharge.

R09DS0052EJ0100 Rev.1.00

Oct 23, 2012

Page 1 of 18

Free Datasheet http://www.datasheet4u.com/

1 page

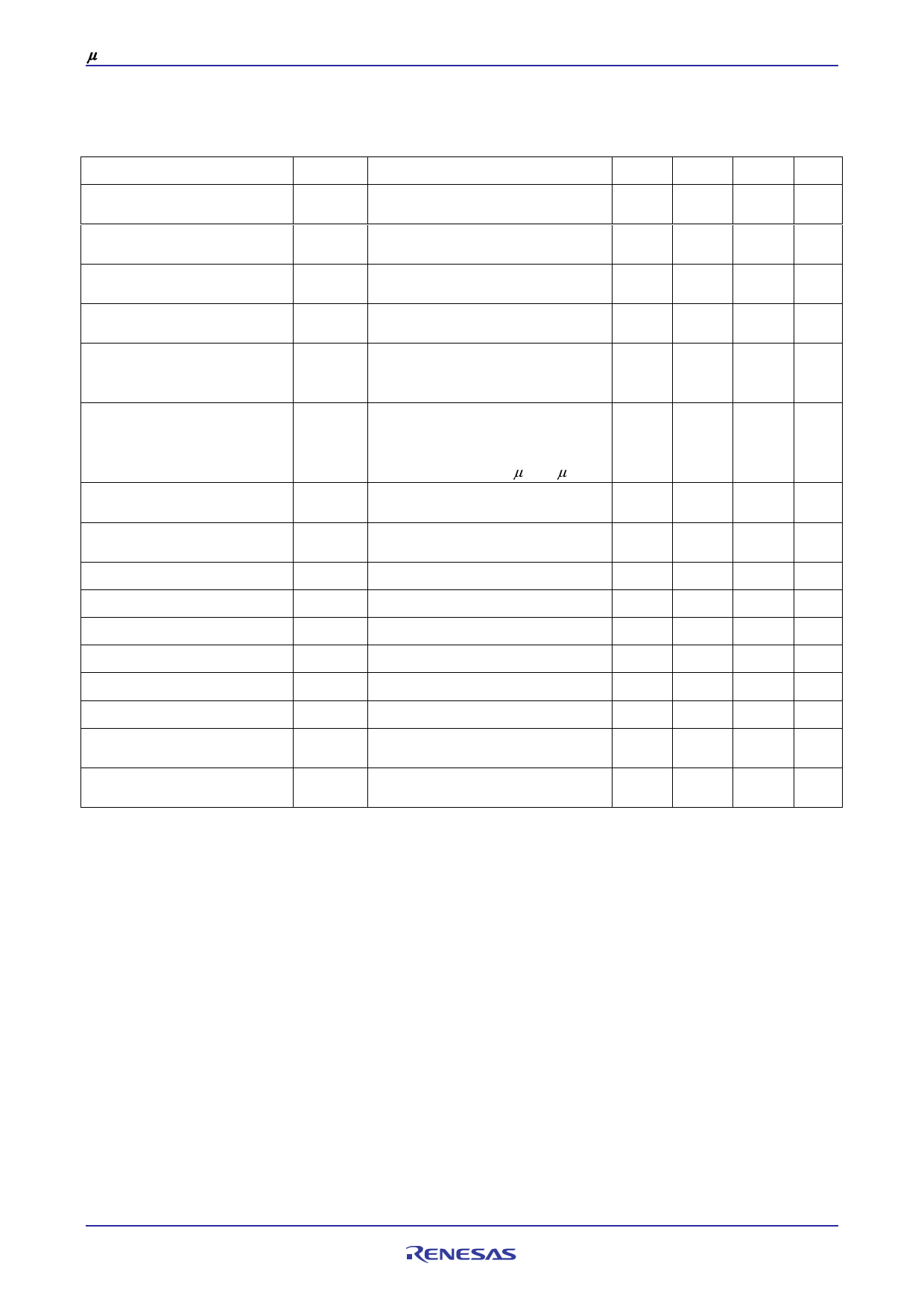

μPC3250T7L

ELECTRICAL CHARACTERISTICS

(TA = +25°C, VCCRF = VCCIF = VDDPLL = +3.3 V, GSW = +3.3 V, ZS = ZL = 50 Ω, fxtal = 25 MHz,

unless otherwise specified)

Parameter

Symbol

Test Conditions

MIN. TYP. MAX. Unit

Conversion Gain 1Note 1

Conversion Gain 2Note 1

Conversion Gain 3Note 1

POLA control Threshold

Voltage 1Note 1

POLA control Threshold

Voltage 2Note 1

(Channel selection )

TONE control signal Threshold

VoltageNote 1

(Channel selection)

Drain Voltage HNote 1, 2

Drain Voltage VNote 1, 2

Drain Voltage 1Note 1, 2

Gconv1

Gconv2

Gconv3

Vth_POLA1

Vth_POLA2

fLO = 9.75 GHz, fIF = 1.5 GHz,

Pin = −50 dBm

fLO = 10.6 GHz, fIF = 1.5 GHz,

Pin = −50 dBm

fLO = 10.75 GHz, fIF = 1.5 GHz,

Pin = −50 dBm

Power Save mode to Normal mode

Dividing resistor : 8.2 kΩ/51 kΩ

Vertical mode to Horizontal mode

Dividing resistor : 8.2 kΩ/51 kΩ

Vth_TONE

VDH

VDV

VD1

Low band to High band

fTONE = 22 kHz, Duty Cycle = 50%,

Pulse wave

Divider capacitor : 0.1 μF/0.1 μF

VPOLA = 18 V, ID = 10 mA,

Rcal = 22 kΩ

VPOLA = 13 V, ID = 10 mA,

Rcal = 22 kΩ

ID = 10 mA, Rcal = 22 kΩ

37 41 45 dB

37 41 45 dB

37 41 45 dB

3.6 − 7.0 V

15.2 15.7 16.2

V

0.1

0.15

0.35 Vp-p

1.8 2.0 2.2 V

1.8 2.0 2.2 V

1.8 2.0 2.2 V

Drain Voltage 2Note 1, 2

VD2 ID = 10 mA, Rcal = 22 kΩ

1.8 2.0 2.2 V

Drain Current HNote 1, 2

IDH VPOLA = 18 V, Rcal = 22 kΩ

8.5 10 11.5 mA

Drain Current VNote 1, 2

IDV VPOLA = 13 V, Rcal = 22 kΩ

8.5 10 11.5 mA

Drain Current 1Note 1, 2

I D1 Rcal = 22 kΩ

8.5 10 11.5 mA

Drain Current 2Note 1, 2

I D2 Rcal = 22 kΩ

8.5 10 11.5 mA

Gate Voltage HNote 1, 2

of FET OFF mode

Gate Voltage VNote 1, 2

of FET OFF mode

VGH

VGV

VPOLA = 13 V

VPOLA = 18 V

−2.0 −2.5 −3.0

−2.0 −2.5 −3.0

V

V

Notes: 1

2

See the evaluation (application) circuit.

The detail connection of pin 20 (TonePol) is shown in the evaluation circuit.

This pin cannot be directly connected to 13 V/18 V polarity control voltage.

The polarity control voltage must be divided to a low voltage by the external resistors.

See the graph of “Rcal vs. IDFET, VDFET.” FET’s drain current can be adjusted by the external resisters (Rcal).

R09DS0052EJ0100 Rev.1.00

Oct 23, 2012

Page 5 of 18

Free Datasheet http://www.datasheet4u.com/

5 Page

μPC3250T7L

EVALUATION CIRCUIT

For example, Polarity control voltage is VPOLA = +13 V and +18 V,

VTP is divided to a low voltage, +1.8 V and +2.5 V, respectively,

by the resistors (8.2 kΩ, 51 kΩ).

Polar

LOsel

VCC (3.3 V)

IFout

24

8.2 kΩ 51 kΩ

Tone

47 Ω

10 μF 0.1 μF

19 VDDPLL (3.3 V)

1

NC

RFin

RFin

NC

For example, Rcal = 22 kΩ,

ID = 10 mA is set.

22 kΩ

Rcal

VDH

VGH

6

GND

(Top View)

CPout

Vref

220 nF 220 Ω

18 390 pF

1 μF

XO1

XO2

CVNeg

GSW

1 nF

13

15 pF

15 pF

AT-41CD2 (fxtal = 25 MHz)

GSW

7 12

Horizontal FET

Vertical FET Common FET1 Common FET2

Remark NC means Non-Connection.

Heat sink (bottom side of the device) is connected to GND.

Board material is RO4003C (Rogers, t = 0.508 mm).

R09DS0052EJ0100 Rev.1.00

Oct 23, 2012

Page 11 of 18

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet UPC3250T7L.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPC3250T7L | SiGe CMOS/BiCMOS Integrated Circuit | Renesas |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |