|

|

PDF AR9331 Data sheet ( Hoja de datos )

| Número de pieza | AR9331 | |

| Descripción | Highly-Integrated and Cost Effective IEEE 802.11n 1x1 2.4 GHz SoC | |

| Fabricantes | Atheros | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AR9331 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Data Sheet

PRELIMINARY

December 2010

AR9331 Highly-Integrated and Cost Effective IEEE 802.11n

1x1 2.4 GHz SoC for AP and Router Platforms

General Description

The Atheros AR9331 is a highly integrated and

cost effective IEEE 802.11n 1x1 2.4 GHz System-

on-a-Chip (SoC) for wireless local area network

(WLAN) AP and router platforms.

In a single chip, the AR9331 includes a MIPS 24K

processor, five-port IEEE 802.3 Fast Ethernet

Switch with MAC/PHY, one USB 2.0 MAC/PHY,

and external memory interface for serial Flash,

SDRAM, DDR1 or DDR2, I2S/SPDIF-Out audio

interface, SLIC VOIP/PCM interface, UART, and

GPIOs that can be used for LED controls or other

general purpose interface configurations.

The AR9331 integrates two Gbit MACs plus a

five-port Fast Ethernet switch with a four-traffic

class Quality of Service (QoS) engine.

The AR9331 integrates an 802.11n 1x1 MAC/BB/

radio with internal PA and LNA. It supports

802.11n operations up to 72 Mbps for 20 MHz

and 150 Mbps for 40 MHz channel respectively,

and IEEE 802.11b/g data rates. Additional

features include on-chip one-time programmable

(OTP) memory.

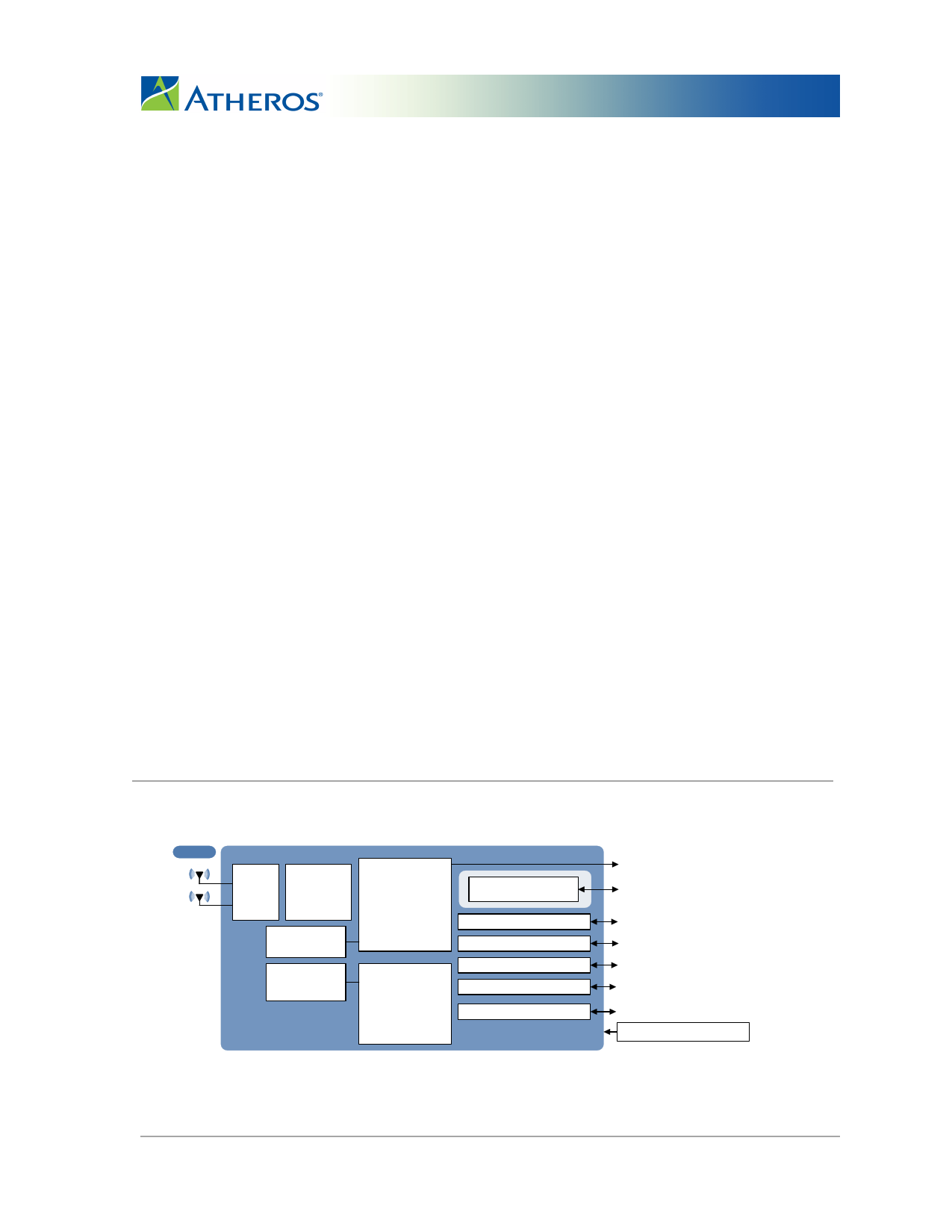

System Block Diagram

Features

■ Complete IEEE 802.11n 1x1 AP or router in a

single chip

■ MIPS 24K processor operating at up to

400 MHz

■ External 16-bit DDR1, DDR2, or SDRAM

memory interface

■ SPI NOR Flash memory support

■ No external EEPROM needed

■ 4 LAN ports and 1 WAN port IEEE 802.3 Fast

Ethernet switch with auto-crossover, auto

polarity, and auto-negotiation in PHYs

■ Four classes of QoS per port

■ Fully integrated RF front-end including PA

and LNA

■ Optional external LNA/PA

■ Switched antenna diversity

■ High-speed UART for console support

■ I2S/SPDIF-out audio interface

■ SLIC for VOIP/PCM

■ USB 2.0 host/device mode support

■ GPIO/LED support

■ JTAG-based processor debugging supported

■ 25 MHz or 40 MHz reference clock input

■ Advanced power management with dynamic

clock switching for ultra-low power modes

■ 148-pin, 12 mm x 12 mm dual-row LPCC

package

2.4 GHz

RF

Front

End

802.11n

1x1 WLAN

MAC/BB/

Radio

Internal

SRAM

I-Cache

D-Cache

AR9331

SDRAM/

DDR1/DDR2

Controller and

NOR Flash

Memory

Interface

MIPS 24K

Processor

5x Fast Ethernet

LAN/WAN Ports

UART

USB MAC/PHY

External Interface

I2S/SPDIF

SLIC

Serial Flash and SDRAM/DDR Interface

5x Fast Ethernet Ports

UART Interface

USB 2.0 Interface

GPIOs/LEDs

Audio Interface

VOIP/PCM

25 or 40 MHz Crystal

© 2010 by Atheros Communications, Inc. All rights reserved. Atheros®, Atheros Driven®, Align®, Atheros XR®, Driving the Wireless Future®, Intellon®, No New Wires®,

Orion® , PLC4Trucks®, Powerpacket®, Spread Spectrum Carrier®, SSC®, ROCm®, Super A/G®, Super G®, Super N®, The Air is Cleaner at 5-GHz®, Total 802.11®, U-

Nav®, Wake on Wireless®, Wireless Future. Unleashed Now.®, and XSPAN®, are registered by Atheros Communications, Inc. Atheros SST™, Signal-Sustain Technology™,

Ethos™, Install N Go™, IQUE™, ROCm™, amp™, Simpli-Fi™, There is Here™, U-Map™, U-Tag™, and 5-UP™ are trademarks of Atheros Communications, Inc. The

Atheros logo is a registered trademark of Atheros Communications, Inc. All other trademarks are the property of their respective holders. Subject to change without notice.

COMPANY CONFIDENTIAL

•1

Free Datasheet http://www.datasheet4u.com/

1 page

PRELIMINARY

6.6.11 USB PHY Reset Control

(USB_PHY_RESET) .................... 82

6.7 GMAC Register ...................................... 83

6.7.1 Ethernet Configuration

(ETH_CFG) .................................. 83

6.8 SLIC Registers ........................................ 84

6.8.1 SLIC Slots Register (SLIC_SLOT) 84

6.8.2 SLIC Clock Control Register

(SLIC_CLOCK_CONTROL) ..... 84

6.8.3 SLIC Control Register

(SLIC_CTRL) ............................... 85

6.8.4 SLIC Tx Slots 1 Register

(SLIC_TX_SLOTS1) .................... 85

6.8.5 SLIC Tx Slots 2 Register

(SLIC_TX_SLOTS2) .................... 85

6.8.6 SLIC Rx Slots 1 Register

(SLIC_RX_SLOTS1) .................... 85

6.8.7 SLIC Rx Slots 2 Register

(SLIC_RX_SLOTS2) .................... 86

6.8.8 SLIC Timing Control Register

(SLIC_TIMING_CTRL) .............. 86

6.8.9 SLIC Interrupt Register

(SLIC_INTR) ................................ 86

6.8.10 SLIC Swap Register (SLIC_SWAP)

87

6.9 MBOX Registers ..................................... 88

6.9.1 Non-Destructive FIFO Status Query

(MBOX_FIFO_STATUS) ............ 88

6.9.2 Non-Destructive SLIC FIFO Status

Query

(SLIC_MBOX_FIFO_STATUS) . 89

6.9.3 Mailbox DMA Engine Policy

Control (MBOX_DMA_POLICY) 89

6.9.4 SLIC Mailbox DMA Engine Policy

Control

(SLIC_MBOX_DMA_POLICY) . 90

6.9.5 Mailbox Rx DMA Descriptors Base

Address

(MBOX_DMA_RX_DESCRIPTOR_

BASE) ............................................ 90

6.9.6 Mailbox Rx DMA Control

(MBOX_DMA_RX_CONTROL) 91

6.9.7 Mailbox Tx DMA Descriptors Base

Address

(MBOX_DMA_TX_DESCRIPTOR_

BASE) ............................................ 91

6.9.8 Mailbox Tx DMA Control

(MBOX_DMA_TX_CONTROL) 92

6.9.9 SLIC Mailbox Rx DMA Descriptors

Base Address

(SLIC_MBOX_DMA_RX_DESCRIP

TOR_BASE) ................................. 92

6.9.10 SLIC Mailbox Rx DMA Control

(SLIC_MBOX_DMA_RX_CONTRO

L) ................................................... 93

6.9.11 SLIC Mailbox Tx DMA Descriptors

Base Address

(SLIC_MBOX_DMA_TX_DESCRIP

TOR_BASE) ................................. 93

6.9.12 SLIC Mailbox Tx DMA Control

(SLIC_MBOX_DMA_TX_CONTRO

L) ................................................... 94

6.9.13 Mailbox FIFO Status

(MBOX_FRAME) ........................ 94

6.9.14 SLIC Mailbox FIFO Status

(SLIC_MBOX_FRAME) ............. 94

6.9.15 FIFO Timeout Period

(FIFO_TIMEOUT) ...................... 95

6.9.16 MBOX Related Interrupt Status

(MBOX_INT_STATUS) .............. 95

6.9.17 SLIC MBOX Related Interrupt

Status

(SLIC_MBOX_INT_STATUS) ... 96

6.9.18 MBOX Related Interrupt Enables

(MBOX_INT_ENABLE) ............. 96

6.9.19 SLIC MBOX Related Interrupt

Enables

(SLIC_MBOX_INT_ENABLE) .. 97

6.9.20 Reset and Clear MBOX FIFOs

(MBOX_FIFO_RESET) ............... 97

6.9.21 SLIC Reset and Clear MBOX FIFOs

(SLIC_MBOX_FIFO_RESET) .... 97

6.10 I2S Registers ........................................... 98

6.10.1 Configure Stereo Block

(STEREO0_CONFIG) ................. 98

6.10.2 Set Stereo Volume

(STEREO0_VOLUME) ............. 100

6.10.3 Tx Sample Counter

(STEREO0_TX_SAMPLE_CNT_LS

B) ................................................. 101

6.10.4 Tx Sample Counter

(STEREO0_TX_SAMPLE_CNT_MS

B) ................................................. 101

6.10.5 Rx Sample Counter

(STEREO0_RX_SAMPLE_CNT_LS

B) ................................................. 101

6.10.6 Stereo Clock Divider

Atheros Communications, Inc.

COMPANY CONFIDENTIAL

AR9331 802.11n 1x1 2.4 GHz SoC for AP and Router Platforms • 3

December 2010 • 3

Free Datasheet http://www.datasheet4u.com/

5 Page

PRELIMINARY

_CONT) ...................................... 187

6.17.90 Tx Timer

(MAC_PCU_TX_TIMER) ........ 188

6.17.91 MAC PCU WoW 6

(MAC_PCU_WOW6) ............... 188

6.17.92 MAC PCU WoW 5

(MAC_PCU_WOW5) ............... 188

6.17.93 Length of Pattern Match for

Pattern 0

(MAC_PCU_WOW_LENGTH1) ..

188

6.17.94 Length of Pattern Match for

Pattern 1

(MAC_PCU_WOW_LENGTH2) ..

189

6.17.95 Enable Control for Pattern Match

Feature of WOW

(WOW_PATTERN_MATCH_LESS

_THAN_256_BYTES) ............... 189

6.17.96 PCU WoW 4

(MAC_PCU_WOW4) ............... 189

6.17.97 Exact Length and Offset

Requirement Flag for WoW

Patterns (WOW2_EXACT) ...... 189

6.17.98 WoW Offset 2 (PCU_WOW6) 190

6.17.99 WoW Offset 3 (PCU_WOW7) 190

6.17.100 Length of Pattern Match for

Pattern 0

(MAC_PCU_WOW_LENGTH3) ..

190

6.17.101 Length of Pattern Match for

Pattern 0

(MAC_PCU_WOW_LENGTH4) ..

190

6.17.102 TID Value Access Category

(MAC_PCU_TID_TO_AC) ...... 191

6.17.103 High Priority Queue Control

(MAC_PCU_HP_QUEUE) ...... 191

6.17.104 MAC PCU BT Coexistence BT

Weights 0

(MAC_PCU_BLUETOOTH_BT_W

EIGHTS0) ................................... 192

6.17.105 MAC PCU BT Coexistence BT

Weights 1

(MAC_PCU_BLUETOOTH_BT_W

EIGHTS1) ................................... 192

6.17.106 MAC PCU BT Coexistence BT

Weights 2

(MAC_PCU_BLUETOOTH_BT_W

EIGHTS2) ................................... 192

6.17.107 MAC PCU BT Coexistence BT

Weights 3

(MAC_PCU_BLUETOOTH_BT_W

EIGHTS3) ................................... 192

6.17.108 Hardware Beacon Processing 1

(MAC_PCU_HW_BCN_PROC1) .

193

6.17.109 Hardware Beacon Processing 2

(MAC_PCU_HW_BCN_PROC2) .

193

6.17.110 Key Cache

(MAC_PCU_KEY_CACHE[0:1023])

..................................................... 194

6.18 Ethernet Registers ............................... 195

6.18.1 MAC Configuration 1 .............. 198

6.18.2 MAC Configuration 2 .............. 199

6.18.3 IPG/IFG ..................................... 200

6.18.4 Half-Duplex ............................... 200

6.18.5 Maximum Frame Length ......... 201

6.18.6 MII Configuration .................... 201

6.18.7 MII Command .......................... 202

6.18.8 MII Address .............................. 202

6.18.9 MII Control ................................ 203

6.18.10 MII Status ................................. 203

6.18.11 MII Indicators .......................... 203

6.18.12 Interface Control ..................... 203

6.18.13 Interface Status ........................ 204

6.18.14 STA Address 1 ......................... 205

6.18.15 STA Address 2 ......................... 206

6.18.16 ETH Configuration 0 .............. 206

6.18.17 ETH Configuration 1 .............. 206

6.18.18 ETH Configuration 2 .............. 207

6.18.19 ETH Configuration 3 .............. 207

6.18.20 ETH Configuration 4 .............. 208

6.18.21 ETH Configuration 5 .............. 209

6.18.22 Tx/Rx 64 Byte Frame Counter

(TR64) ......................................... 209

6.18.23 Tx/Rx 65-127 Byte Frame Counter

(TR127) ....................................... 209

6.18.24 Tx/Rx 128-255 Byte Frame

Counter (TR255) ....................... 209

6.18.25 Tx/Rx 256-511 Byte Frame

Counter (TR511) ....................... 210

6.18.26 Tx/Rx 512-1023 Byte Frame

Counter (TR1K) ......................... 210

Atheros Communications, Inc.

COMPANY CONFIDENTIAL

AR9331 802.11n 1x1 2.4 GHz SoC for AP and Router Platforms • 9

December 2010 • 9

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AR9331.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AR9331 | Highly-Integrated and Cost Effective IEEE 802.11n 1x1 2.4 GHz SoC | Atheros |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |