|

|

PDF LE28DW3212AT-80B Data sheet ( Hoja de datos )

| Número de pieza | LE28DW3212AT-80B | |

| Descripción | 32 Megabit FlashBank Memory | |

| Fabricantes | Sanyo | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LE28DW3212AT-80B (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

32 Megabit FlashBank Memory

LE28DW3212AT-80B

FEATURES:

• Single 3.0-Volt Read and Write Operations

• Separate Memory Banks by Address Space

– Bank1: 16Mbit (1024K x 16 / 2048K x 8) Flash

– Bank2: 16Mbit (1024K x 16 / 2048K x 8) Flash

– Simultaneous Read and Write Capability

• Superior Reliability

– Endurance: 10,000 Cycles

100,000 Cycles (Sector Erase)

– Data Retention: 10 years

• Low Power Consumption

– Active Current, Read:

– Active Current, Read & Write:

– Standby Current:

– Auto Low Power Mode Current:

10 mA (typical)

30 mA (typical)

5µA (typical)

5µA (typical)

• Fast Write Operation

– Chip Erase + Program:

– Block Erase + Program:

– Sector Erase + Program:

30 sec (typical)

500 ms (typical)

45 ms (typical)

• Read Access Time

– 80 ns

• Latched Address and Data

• End of Write Detection

– Toggle Bit / Data # Polling / RY/BY#

• Write Protection by WP# pin

• Flash Bank: Two Small Erase Element Sizes

– 2K Words per Sector or 32K Words per Block

– Erase either element before Word Program

• CMOS I/O Compatibility

• Packages Available

– 48-Pin TSOP (12mm x 20mm)

• Continuous Hardware and Software Data

Protection (SDP)

1

Product Description

The LE28DW3212AT consists of two memory banks, 2 each

contains of 1024K x 16 bits or 2048K x 8 sector mode flash

EEPROM manufactured with SANYO's proprietary, high perfor-

mance FlashTechnology. The LE28DW3212AT writes with a

3.0-volt-only power supply.

The LE28DW3212AT is divided into two separate memory

banks. Each Flash Bank is typically used for program storage

and contains 512 sectors of 2K words or 32blocks of 32K

words.

Any bank may be used for executing code while writing data to

a different bank. Each memory bank is controlled by separate

Bank selection address (A20) lines.

LE28DW3212AT inherently uses less energy during Erase,

and Program than alternative flash technologies. The total

energy consumed is a function of the applied voltage, current,

and time of application. Since for any given voltage range, the

Flash technology uses less current to program and has a

shorter Erase time, the total energy consumed during any

Erase or Program operation is less than alternative flash

technologies. The Auto Low Power mode automatically re-

duces the active read current to approximately the same as

standby; thus, providing an average read current of approxi-

mately 1 mA/MHz of Read cycle time.

Device Operation

The LE28DW3212AT operates as two independent 16Mega-

bit t Word Pogram, Sector Erase flash EEPROMs. Two

memory Banks are spareted by the address space.

The Bank1 is assigned as 000000h to 0FFFFFh, Bank2 is

assigned as 100000h to 1FFFFFh.

All memory banks share common I/O lines, WE#, and OE#.

Memory bank selection is by bank select address(A20). WE# is

used with SDP to control the Erase and Program operation in

each memory bank.

The LE28DW3212AT provides the added functionality of

being able to simultaneously read from one memory bank

while erasing, or programming to one other memory bank.

Once the internally controlled Erase or Program cycle in a

memory bank has commenced, a different memory bank can

be accessed for read. Also, once WE# and CE# are high

during the SDP load sequence, a different bank may be

accessed to read. LE28DW3212AT which selectes banks

(A20) by a address. It can be used as a normal conventinal

flash memory when operats erase or program operation to

only a bank at non-concurrent operation.

The device ID cannot be accessed while any bank is writing,

erasing, or programming.

The Auto Low Power Mode automatically puts the

LE28DW3212AT in a near standby mode after data has been

accessed with a valid Read operation. This reduces the IDD

active read current from typically 10mA to typically 5µA. The

Auto Low Power mode reduces the typical IDD active read

current to the range of 1mA/MHz of Read cycle time. If a

concurrent Read while Write is being performed, the IDD is

reduced to typically 40mA. The device exits the Auto Low

Power mode with any address transition or control signal

transition used to initiate another Read cycle, with no access

time penalty.

SANYO Electric Co.,Ltd. Semiconductor Company 1-1-11Sakata Oizumi Gunma Japan

The Flash Bank product family was jointly developed by SANYO and Sillicon Storage Technology,Inc.(SST),under SST's technology license. This preliminary specification is subject to change without notice.

R.1.20(11/13/2001) No.xxxx-1/19

Free Datasheet http://www.datasheet4u.com/

1 page

32 Megabit FlashBank Memory

LE28DW3212AT-80B

5

Symbol

A20

A19-A0,A-1

A19-A15

A19-A10

Pin Name

Bank Select address

Flash Bank addresses

Flash Bank Block addresses

Flash Bank Sector addresses

DQ15-DQ0 Data Input/Output

CE#

OE#

WE#

BYTE#

RY/BY#

WP#

RESET#

VDD

Chip Enable

Output Enable

Write Enable

Byte selection

Ready / Busy output

Write Protect

Reset

Power Supply

Vss

Ground

NC No Connection

Table1: Pin Description

Function

To activate the Bank1 when low, to activate the Bank2 when high.

To provide Flash Bank address.

To select a Flash Bank Block for erase.

To select a Flash Bank Sector for erase.

To output data during read cycle and receive input data during write

cycle. The outputs are in tristate when OE# is high or CE# is high.

To activate the Flash Bank when CE# is low.

To gate the data output buffers.

To control the write, erase or program operations.

To select a Byte mode when low, to select a Word mode when high.

To output low when write, other case is High-Z.

To execute Hardware write protect when low.

To execute Hardware reset when low.

To provide 3.0 volts supply.(2.7volts to 3.6 volts)

Unconnected Pins

Charge Pump

&

Vref.

Y-Decoder

Address Buffer

&

Data Latchs

X-Decoder

1024Kx16

Flash Bank2

A20-A0

CE#

OE#

WE#

WP#

RY/BY#

RESET#

BYTE#

Control Logic

DQ15-DQ0

1024Kx16

Flash Bank1

I/O Buffers & Data Latches

Figure2-1: Functinaly Block Diagram

SANYO Electric Co.,Ltd. Semiconductor Company 1-1-15Sakata Oizumi Gunma Japan

R.1.20(11/13/2001) No.xxxx-5/19

5 Page

32 Megabit FlashBank Memory

LE28DW3212AT-80B

11

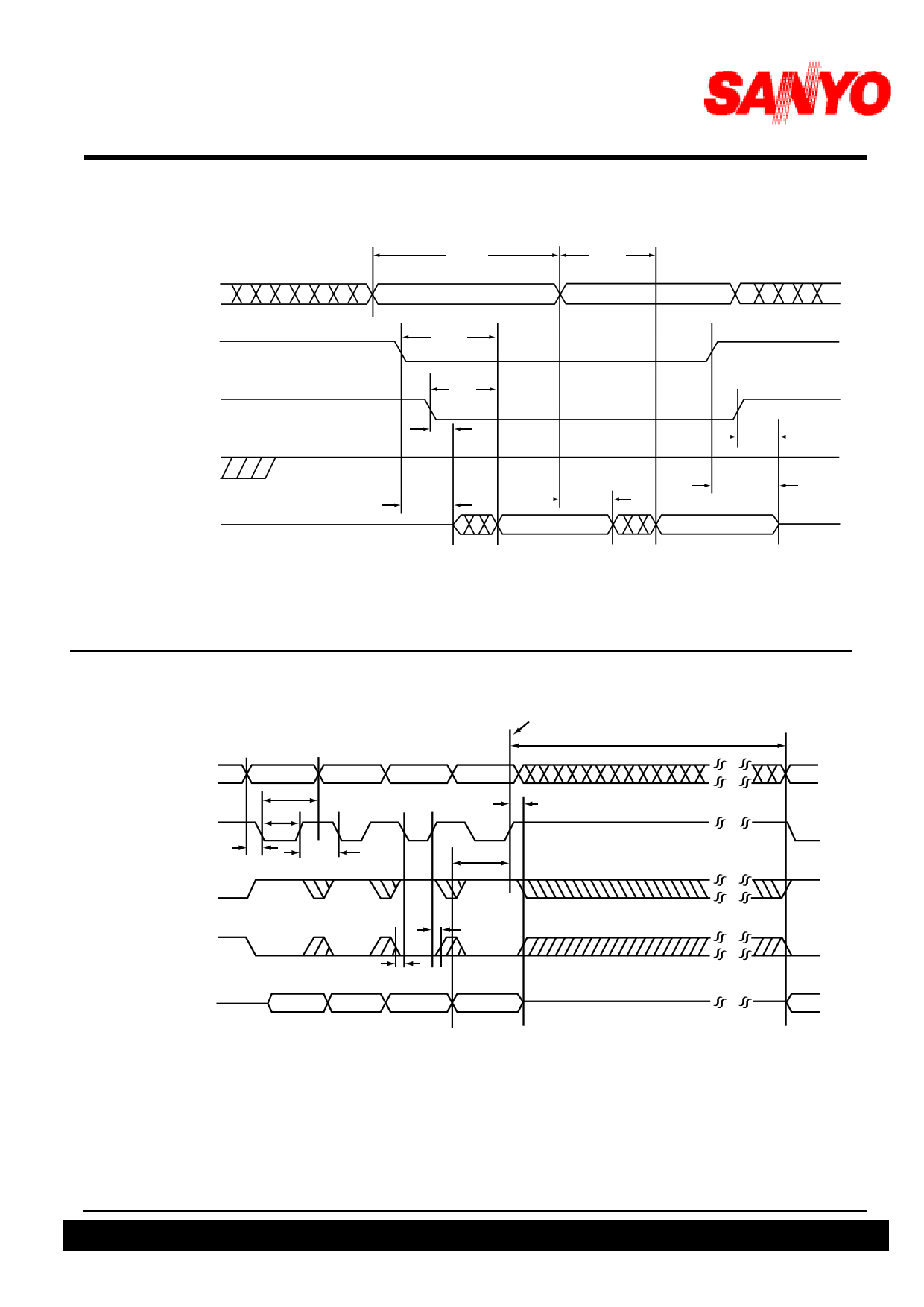

ADDRESS A20- A0

TRC

TAA

TCE

CE#

OE#

TOE

WE#

VIH

TOLZ

DQ15-DQ0

HIGH-Z

TCLZ

TOH

DATA VALID

Exsample for Word Mode, in Byte Mode A-1=Address Input

Figure 3: Read Cycle Timing Diagram

TOHZ

TCHZ

DATA VALID

HIGH-Z

28DW3212\F3_E

ADDRESS A20-A0

WE#

TAS

OE#

5555

TAH

TWP

2AAA

TWPH

5555

ADDR

INTERNAL PROGRAM OPERATION STARTS

TBP

TDH

TDS

CE#

DQ15-DQ0

AA

SW0

TCEH

TCES

55 A0

DATA

SW1

SW2

WORD

(ADDR/DATA)

28DW3212\F4-1_E

Exsample for Word Mode, in Byte Mode A-1=Address Input

Figure 4-1: WE# Controlled Word Program Cycle Timing Diagram

SANYO Electric Co.,Ltd. Semiconductor Company 1-1-11S1akata Oizumi Gunma Japan

R.1.20(11/13/2001) No.xxxx-11/19

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet LE28DW3212AT-80B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LE28DW3212AT-80B | 32 Megabit FlashBank Memory | Sanyo |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |