|

|

PDF PCAL6408A Data sheet ( Hoja de datos )

| Número de pieza | PCAL6408A | |

| Descripción | 8-bit I2C-bus/SMBus I/O expander | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PCAL6408A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

PCAL6408A

Low-voltage translating, 8-bit I2C-bus/SMBus I/O expander

with interrupt output, reset, and configuration registers

Rev. 2 — 6 December 2012

Product data sheet

1. General description

The PCAL6408A is an 8-bit general-purpose I/O expander that provides remote I/O

expansion for most microcontroller families via the I2C-bus interface.

NXP I/O expanders provide a simple solution when additional I/Os are needed while

keeping interconnections to a minimum, for example, in battery-powered mobile

applications for interfacing to sensors, push buttons, keypad, etc. In addition to providing

a flexible set of GPIOs, it simplifies interconnection of a processor running at one voltage

level to I/O devices operating at a different (usually higher) voltage level. The PCAL6408A

has built-in level shifting feature that makes these devices extremely flexible in mixed

signal environments where communication between incompatible I/O voltages is required.

Its wide VDD range of 1.65 V to 5.5 V on the dual power rail allows seamless

communications with next-generation low voltage microprocessors and microcontrollers

on the interface side (SDA/SCL) and peripherals at a higher voltage on the port side.

There are two supply voltages for PCAL6408A: VDD(I2C-bus) and VDD(P). VDD(I2C-bus)

provides the supply voltage for the interface at the master side (for example, a

microcontroller) and the VDD(P) provides the supply for core circuits and Port P. The

bidirectional voltage level translation in the PCAL6408A is provided through VDD(I2C-bus).

http://www.DataSheet4U.net/

VDD(I2C-bus) should be connected to the VDD of the external SCL/SDA lines. This indicates

the VDD level of the I2C-bus to the PCAL6408A, while the voltage level on Port P of the

PCAL6408A is determined by the VDD(P).

The PCAL6408A contains the PCA6408A register set of 8-bit Configuration, Input, Output,

and Polarity Inversion registers and additionally, the PCAL6408A has Agile I/O, which are

additional features specifically designed to enhance the I/O. These additional features

are: programmable output drive strength, latchable inputs, programmable

pull-up/pull-down resistors, maskable interrupt, interrupt status register, programmable

open-drain or push-pull outputs. The PCAL6408A is a pin-to-pin replacement to the

PCA6408A, however, the PCAL6408A powers up with all I/O interrupts masked. This

mask default allows for a board bring-up free of spurious interrupts at power-up.

At power-on, the I/Os are configured as inputs. However, the system master can enable

the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for

each input or output is kept in the corresponding input or output register. The polarity of

the Input Port register can be inverted with the Polarity Inversion register, saving external

logic gates. Programmable pull-up and pull-down resistors eliminate the need for discrete

components.

datasheet pdf - http://www.DataSheet4U.net/

1 page

NXP Semiconductors

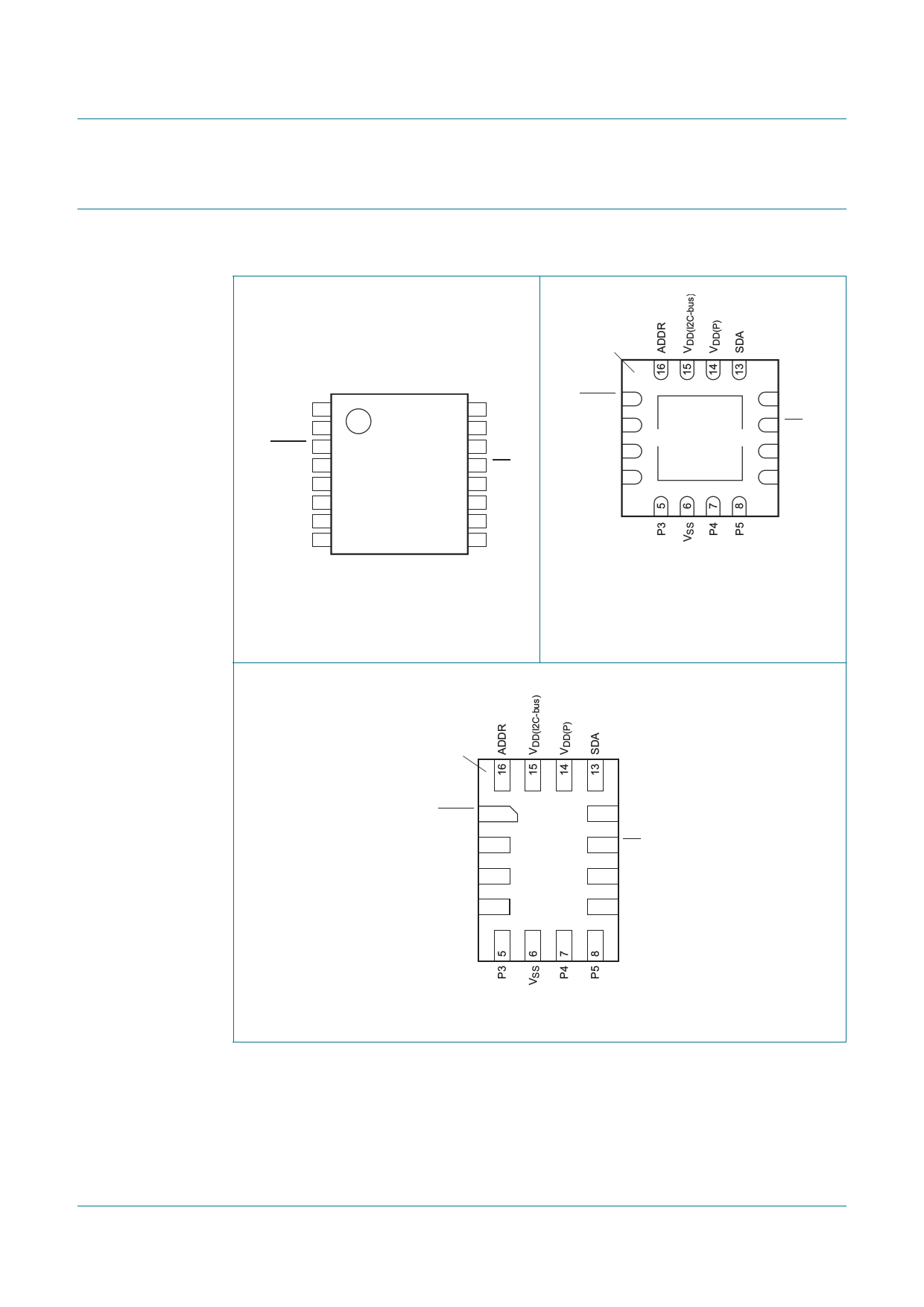

5. Pinning information

5.1 Pinning

PCAL6408A

Low-voltage translating, 8-bit I2C-bus/SMBus I/O expander

terminal 1

index area

VDD(I2C-bus) 1

ADDR 2

RESET 3

P0 4

P1 5

P2 6

P3 7

VSS 8

PCAL6408APW

16 VDD(P)

15 SDA

14 SCL

13 INT

12 P7

11 P6

10 P5

9 P4

002aah086

RESET 1

P0 2

P1 3

P2 4

12 SCL

PCAL6408ABS

11 INT

10 P7

9 P6

Transparent top view

002aah087

Fig 2. Pin configuration for TSSOP16

Fig 3.

The exposed center pad, if used, must be

connected only as a secondary VSS or

must be left electrically open.

Pin configuration for HVQFN16

http://www.DataSheet4U.net/

PCAL6408AHK

terminal 1

index area

RESET 1

P0 2

P1 3

P2 4

12 SCL

11 INT

10 P7

9 P6

Transparent top view

002aah088

Fig 4. Pin configuration for XQFN16

PCAL6408A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 6 December 2012

© NXP B.V. 2012. All rights reserved.

5 of 48

datasheet pdf - http://www.DataSheet4U.net/

5 Page

NXP Semiconductors

PCAL6408A

Low-voltage translating, 8-bit I2C-bus/SMBus I/O expander

Table 13. Input latch register (address 42h)

Bit 7 6 5 4 3 2 1 0

Symbol

L7

L6

L5

L4

L3

L2

L1

L0

Default

0

0

0

0

0

0

0

0

7.4.7 Pull-up/pull-down enable register (43h)

This register allows the user to enable or disable pull-up/pull-down resistors on the I/O

pins. Setting the bit to logic 1 enables the selection of pull-up/pull-down resistors. Setting

the bit to logic 0 disconnects the pull-up/pull-down resistors from the I/O pins. Also, the

resistors will be disconnected when the outputs are configured as open-drain outputs (see

Section 7.4.11). Use the pull-up/pull-down selection registers to select either a pull-up or

pull-down resistor.

Table 14. Pull-up/pull-down enable register (address 43h)

Bit 7 6 5 4 3 2 1 0

Symbol PE7 PE6 PE5 PE4 PE3 PE2 PE1 PE0

Default

0

0

0

0

0

0

0

0

7.4.8 Pull-up/pull-down selection register (44h)

The I/O port can be configured to have pull-up or pull-down resistor by programming the

pull-up/pull-down selection register. Setting a bit to logic 1 selects a 100 k pull-up

resistor for that I/O pin. Setting a bit to logic 0 selects a 100 k pull-down resistor for that

I/O pin. If the pull-up/down feature is disconnected, writing to this register will have no

effect on I/O pin. Typical value is 100h t kt p : with/ / w w minimumw . D a t a S h ofe e 50t 4 U k. n e andt / maximum of 150 k.

Table 15.

Bit

Symbol

Default

Pull-up/pull-down selection register (address 44h)

76543

PUD7 PUD6 PUD5 PUD4 PUD3

11111

2

PUD2

1

1

PUD1

1

0

PUD0

1

7.4.9 Interrupt mask register (45h)

Interrupt mask register is set to logic 1 upon power-on, disabling interrupts during system

start-up. Interrupts may be enabled by setting corresponding mask bits to logic 0. If an

input changes state and the corresponding bit in the Interrupt mask register is set to 1, the

interrupt is masked and the interrupt pin (INT) will not be asserted. If the corresponding bit

in the Interrupt mask register is set to 0, the interrupt pin will be asserted.

When an input changes state and the resulting interrupt is masked (interrupt mask bit

is 1), setting the input mask register bit to 0 will cause the interrupt pin to be asserted.

If the interrupt mask bit of an input that is currently the source of an interrupt is set to 1,

the interrupt pin will be de-asserted.

Table 16. Interrupt mask register (address 45h)

Bit 7 6 5 4 3 2 1 0

Symbol

M7

M6

M5

M4

M3

M2

M1

M0

Default

1

1

1

1

1

1

1

1

PCAL6408A

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 2 — 6 December 2012

© NXP B.V. 2012. All rights reserved.

11 of 48

datashe

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet PCAL6408A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PCAL6408A | 8-bit I2C-bus/SMBus I/O expander | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |