|

|

PDF TC74HC112AFN Data sheet ( Hoja de datos )

| Número de pieza | TC74HC112AFN | |

| Descripción | Dual J-K Flip Flop | |

| Fabricantes | Toshiba Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TC74HC112AFN (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

www.DataSheet.co.kr

TC74HC112AP/AF/AFN

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

TC74HC112AP,TC74HC112AF,TC74HC112AFN

Dual J-K Flip Flop with Preset and Clear

The TC74HC112A is a high speed CMOS DUAL J-K FLIP

FLOP fabricated with silicon gate C2MOS technology.

It achieves the high speed operation similar to equivalent

LSTTL while maintaining the CMOS low power dissipation.

In accordance with the logic levels applied to the J and K

inputs, the outputs change state on the negative going transition

of the clock pulse.

CLR and PR are independent of the clock and are actived

by a low logic level on the corresponding input.

All inputs are equipped with protection circuits against static

discharge or transient excess voltage.

Features

• High speed: fmax = 67 MHz (typ.) at VCC = 5 V

• Low power dissipation: ICC = 2 μA (max) at Ta = 25°C

• High noise immunity: VNIH = VNIL = 28% VCC (min)

• Output drive capability: 10 LSTTL loads

• Symmetrical output impedance: |IOH| = IOL = 4 mA (min)

• Balanced propagation delays: tpLH ∼− tpHL

• Wide operating voltage range: VCC (opr) = 2 to 6 V

• Pin and function compatible with 74LS112

Pin Assignment

Note: xxxFN (JEDEC SOP) is not available in

Japan.

TC74HC112AP

TC74HC112AF

TC74HC112AFN

Weight

DIP16-P-300-2.54A

SOP16-P-300-1.27A

SOL16-P-150-1.27

: 1.00 g (typ.)

: 0.18 g (typ.)

: 0.13 g (typ.)

1 2007-10-01

Datasheet pdf - http://www.DataSheet4U.net/

1 page

www.DataSheet.co.kr

TC74HC112AP/AF/AFN

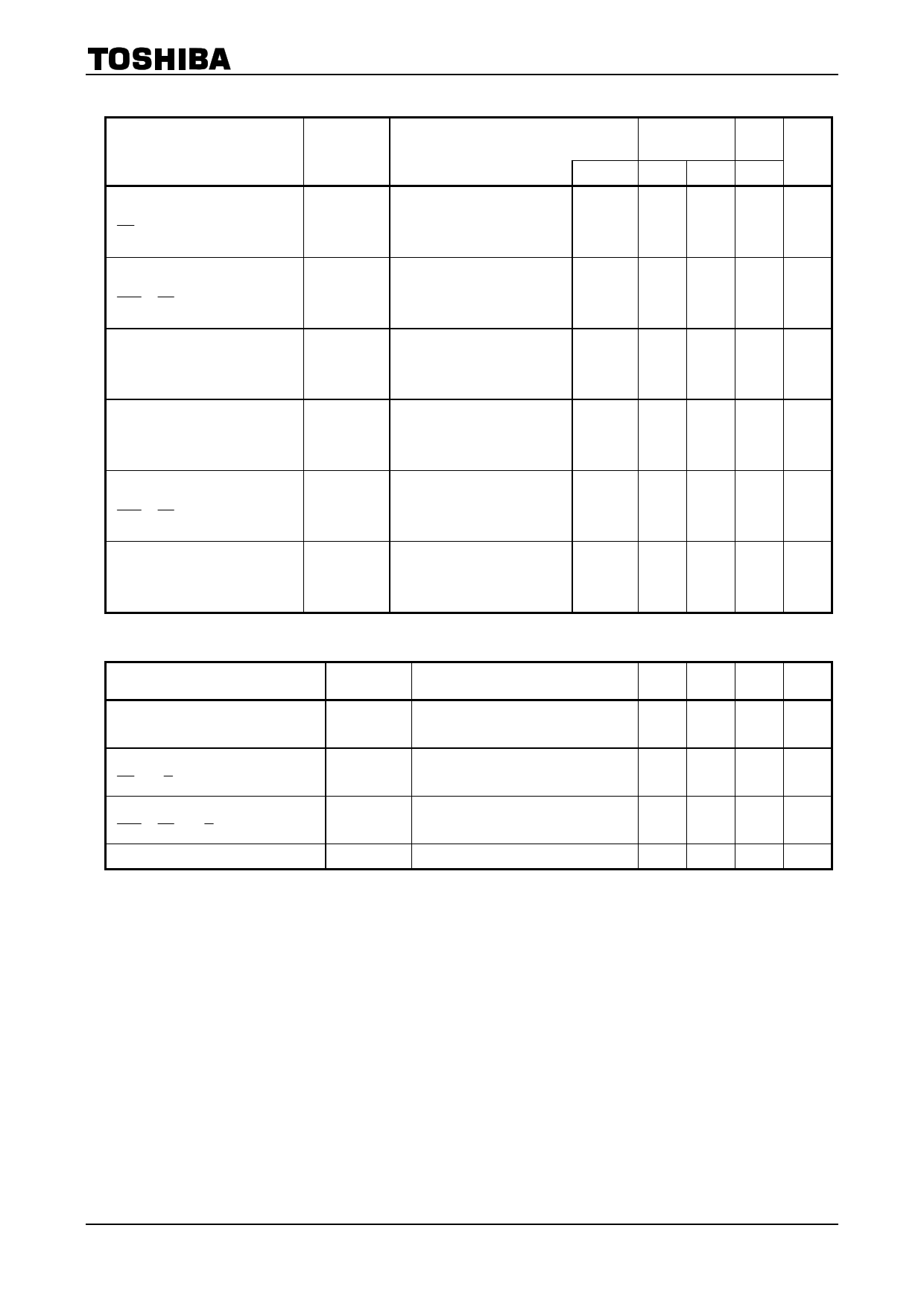

Timing Requirements (input: tr = tf = 6 ns)

Characteristics

Symbol

Minimum pulse width

( CK )

Minimum pulse width

( CLR , PR )

tW (L)

tW (H)

tW (L)

Minimum set-up time

ts

Minimum hold time

Minimum removal time

( CLR , PR )

Clock frequency

th

trem

f

Test Condition

⎯

⎯

⎯

⎯

⎯

⎯

VCC (V)

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

Ta = 25°C

Typ. Limit

⎯ 75

⎯ 15

⎯ 13

⎯ 75

⎯ 15

⎯ 13

⎯ 75

⎯ 15

⎯ 13

⎯0

⎯0

⎯0

⎯ 50

⎯ 10

⎯9

⎯6

⎯ 30

⎯ 34

Ta =

−40 to

85°C

Limit

95

19

16

95

19

16

95

19

16

0

0

0

60

12

11

4

24

28

Unit

ns

ns

ns

ns

ns

MHz

AC Characteristics (CL = 15 pF, VCC = 5 V, Ta = 25°C, input: tr = tf = 6 ns)

Characteristics

Symbol

Test Condition

Min Typ. Max Unit

Output transition time

Propagation delay time

( CK -Q, Q )

Propagation delay time

( CLR , PR -Q, Q )

Maximum clock frequency

tTLH

tTHL

tpLH

tpHL

tpLH

tpHL

fmax

⎯

⎯4

8 ns

⎯ ⎯ 13 21 ns

⎯ ⎯ 15 22 ns

⎯ 32 67 ⎯ MHz

5 2007-10-01

Datasheet pdf - http://www.DataSheet4U.net/

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet TC74HC112AFN.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TC74HC112AF | Dual J-K Flip Flop | Toshiba Semiconductor |

| TC74HC112AFN | Dual J-K Flip Flop | Toshiba Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |