|

|

PDF LC89052TA-E Data sheet ( Hoja de datos )

| Número de pieza | LC89052TA-E | |

| Descripción | Digital Audio Interface Receiver | |

| Fabricantes | Sanyo Semicon Device | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de LC89052TA-E (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet.co.kr

Ordering number : ENN7457A

LC89052TA-E

CMOS IC

Digital Audio Interface Receiver

1. Overview

The LC89052TA-E is an audio LSI that demodulates according to the data format for the data transferred between

digital audio devices via the IEC 60958/61937 and EIAJ CP-1201. It supports sampling frequencies of up to 192kHz

and output data lengths up to 28 bits.

Despite it is compact and made in a low cost, the LC89052TA-E includes a built-in oscillator and serial data input

circuits and allows the system microcontroller to read the sub-code Q data and channel status. It supports low-power

modes that allow low-voltage operation. It also supports a lower power mode, which is suitable for application that

requires long battery life, such as cell phones, PDAs, and portable audio devices.

2. Features

• Incorporates a built-in PLL circuit to synchronize with transferred bi-phase mark signal.

• Can receive input with sampling frequencies of 32kHz to 192kHz.

• Can set the upper limit of sampling frequency of received data.

• Can receive input data of specific sampling frequencies.

• Outputs the following clocks: fs, 64fs, 128fs, 256fs, 384fs, and 512fs.

• Contains a built-in oscillation amplifier that can construct a oscillation circuit. An external clock can be also provided.

• Outputs an externally input clock signal that can be used as the A/D converter clock when the PLL is unlocked.

• Maintains the continuity of the output clock when the clock is switched.

• Equipped with a serial digital audio data input pin that can be configured for a demodulated signal output.

• Can output up to 28 bits of data, and also supports output of I2S and input NRZ data.

• Can output bi-phase mark signal synchronized with the 128fs bit clock.

• Provides an output pin for the channel status bit 1 non-PCM data detection bit.

• Provides an output pin for the channel status emphasis detection bit.

• Supports a lower-power mode.

• Calculates the input signal sampling frequency and outputs it from the microcontroller interface.

• Can output the first 48 bits of the channel status with the microcontroller interface.

• Can output the 80-bit sub-code Q data with CRC flags via microcontroller interface.

• Outputs various state changes as interrupt signals to the microcontroller interface.

Continued on next page.

Any and all SANYO Semiconductor products described or contained herein do not have specifications

that can handle applications that require extremely high levels of reliability, such as life-support systems,

aircraft's control systems, or other applications whose failure can be reasonably expected to result in

serious physical and/or material damage. Consult with your SANYO Semiconductor representative

nearest you before using any SANYO Semiconductor products described or contained herein in such

applications.

SANYO Semiconductor assumes no responsibility for equipment failures that result from using products

at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition

ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor

products described or contained herein.

92706 / 12505 TN IM / 71003 SI IM No.7457-1/42

Datasheet pdf - http://www.DataSheet4U.net/

1 page

www.DataSheet.co.kr

7. Electrical Characteristics

7.1 Absolute Maximum Ratings

LC89052TA-E

Table 7.1 Absolute Maximum Ratings at AGND = DGND = 0V

Parameter

Symbol

Conditions

Ratings

Maximum supply voltage

Maximum supply voltage

Input voltage 1

Input voltage 2

Output voltage

Storage temperature

AVDD max

DVDD max

VIN1

VIN2

VOUT

Tstg

7-1-1

7-1-2

7-1-3

7-1-4

7-1-5

–0.3 to 4.6

–0.3 to 4.6

–0.3 to 3.9

–0.3 to 5.8

–0.3 to 3.9

–55 to 125

Operating temperature

Topg

–30 to 70

Maximum output current

Ii, IOUT

7-1-6

7-1-1 : AVDD pin.

7-1-2 : DVDD pin.

7-1-3 : XIN pin.

_____

7-1-4 : RXIN, SDIN, PD, CE, CL, and__D_I_p_i_ns._____

7-1-5 : XOUT, ERROR, DO, E/INT, AUDIO, UGPI, CKOUT, BCK, LRCK, and DATAO pins.

7-1-6 : Per single input or output pin.

±20

unit

V

V

V

V

V

°C

°C

mA

7.2 Recommended Operating Conditions

Table 7.2 Recommended Operating Conditions

Parameter

Symbol

Conditions

min

Supply voltage 1

Supply voltage 2

Input voltage range 1

Input voltage range 2

Operating temperature

AVDD, DVDD

AVDD, DVDD

VIN1

VIN2

Vopg

7-2-1

7-2-2

7-2-3

7-2-4

2.7

3.0

0

0

–30

7-2-1 :

7-2-2 :

7-2-3 :

7-2-4 :

PLLCK [1:0] = "00" or PLLCK [1:0] = "01"

PLLCK [1:0] = "10" or PLLCK [1:0] = "11"

XIN pin

_____

RXIN, SDIN, PD, CE, CL, and DI pins

typ

3.3

3.3

3.3

3.3

max

3.6

3.6

3.6

5.5

70

unit

V

V

V

V

°C

7.3 Input and Output Pin Capacitances

Table 7.3 Input and Output Pin Capacitances

Parameter

Symbol

Conditions

min

Input pins

CIN 7-3-1

Output pins

COUT

7-3-1

7-3-1 : AVDD = DVDD = VIN1 = VIN2 = 0 V, Ta = 25°C, f = 1MHz

typ

max

10

10

unit

pF

pF

No.7457-5/42

Datasheet pdf - http://www.DataSheet4U.net/

5 Page

www.DataSheet.co.kr

LC89052TA-E

8.3 Clocks

8.3.1 PLL (LPF)

• The LC89052TA-E incorporates a VCO (Voltage Controlled Oscillator) that can synchronize with sampling

frequencies of 30kHz to 195kHz.

• The locking frequency is selected with PLLCK[1:0]. The VCO circuit can be stopped with PLLOPR.

• The range of input data that can be received differs depending on the settings of PLLCK[1:0].

• The (512/2)fs for the PLLCK[1:0] = "11" in the table below is the state where the PLL itself is synchronized with the

512fs clock, but the clock signal output from the CKOUT pin is 1/2 of the PLL locked frequency, which is 256fs.

See the chapter on the of output clock for further information.

• We recommend the 256fs setting with PLLCK[1:0] = "00" for the systems such as portable equipment that need to

restrain the consumption electric power. We also recommend the 512fs setting with PLLCK[1:0] = "10" or the

(512/2)fs with PLLCK[1:0] = "11" for the systems such as AV amplifiers that require improved performance.

PLLCK1

0

0

1

1

Table 8.3 Input Data Reception Ranges and PLL Lock Frequency Settings

PLLCK0

PLL lock frequency

Input data reception range

0 256fs

30k to 195kHz

1 384fs

30k to 108kHz

0 512fs

30k to 108kHz

1 (512/2)fs

30k to 108kHz

• LPF is the PLL loop filter connection pin. Use the correct recommended resistance and capacitance as values listed in

the table below according to the PLLCK[1:0] settings.

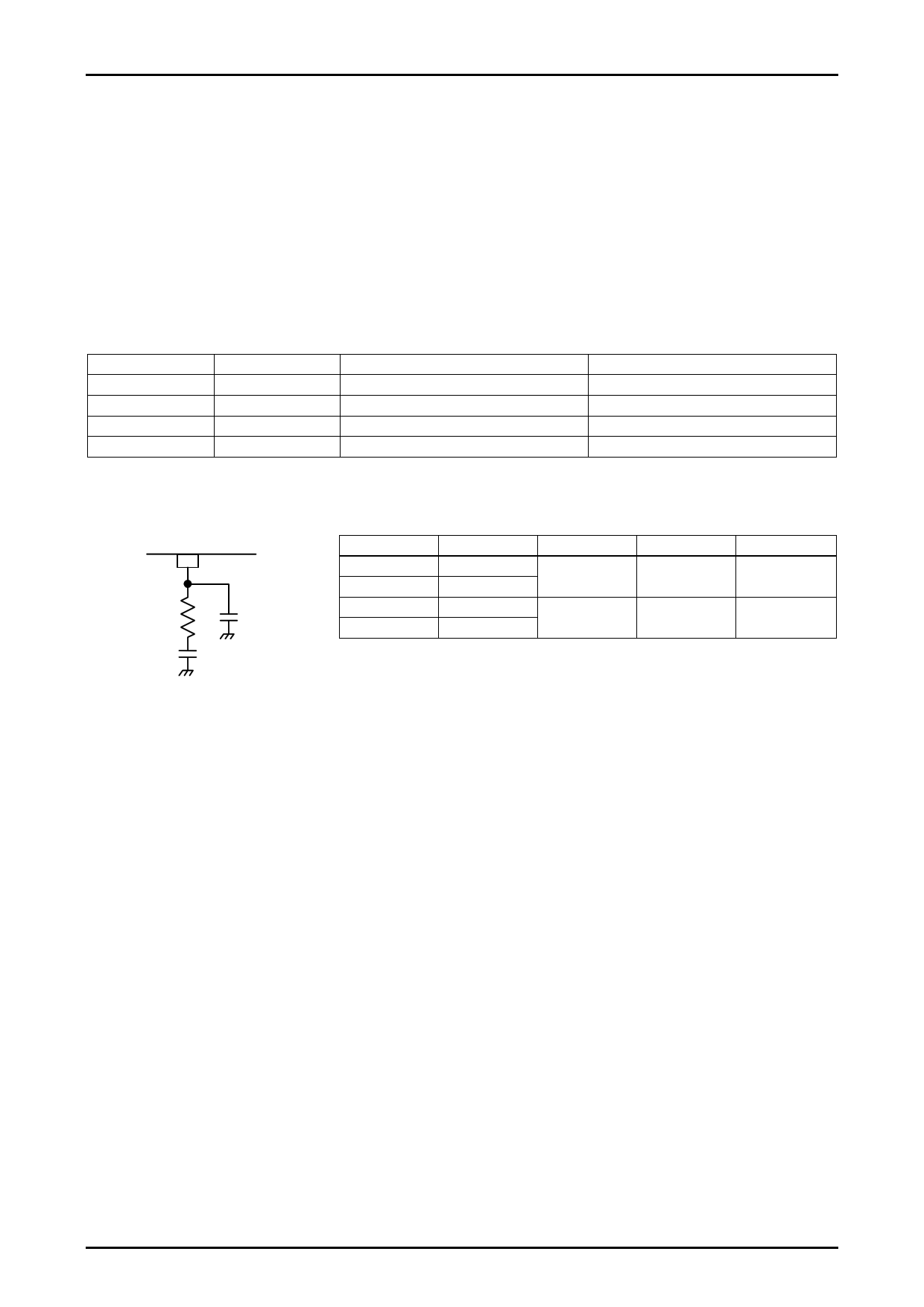

LPF

R0 C1

C0

PLLCK1

0

0

1

1

PLLCK0

0

1

0

1

R0

150Ω

150Ω

Figure 8.2 PLL Loop Filter Configuration

C0

0.047µF

0.068µF

C1

0.0068µF

0.0047µF

No.7457-11/42

Datasheet pdf - http://www.DataSheet4U.net/

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet LC89052TA-E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LC89052TA-E | Digital Audio Interface Receiver | Sanyo Semicon Device |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |