|

|

PDF KK74HC651A Data sheet ( Hoja de datos )

| Número de pieza | KK74HC651A | |

| Descripción | Octal 3-State Bus Transceivers and D Flip-Flops | |

| Fabricantes | KODENSHI KOREA | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de KK74HC651A (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

TECHNICAL DATA

Octal 3-State Bus Transceivers

and D Flip-Flops

High-Performance Silicon-Gate CMOS

KK74HC651A

The KK74HC651A is identical in pinout to the LS/ALS651. The

device inputs are compatible with standard CMOS outputs; with pullup

resistors, they are compatible with LS/ALSTTL outputs.

These devices consist of bus transceiver circuits, D-type flip-flop, and

control circuitry arranged for multiplex transmission of data directly from

the data bus or from the internal storage registers. Direction and Output

Enable are provided to select the read-time or stored data function. Data

on the A or B Data bus, or both, can be stored in the internal D flip-flops

by low-to-high transitions at the appropriate clock pins (A-to-B Clock or

B-to-A Clock) regardless of the select or enable or enable control pins.

When A-to-B Source and B-to-A Source are in the real-time transfer

mode, it is also possible to store data without using the internal D-type

flip-flops by simulta-neously enabling Direction and Output Enable. In

this configuration each output reinforces its input. Thus, when all other

data sources to the two sets of bus lines are at high impedance, each set of

bus lines will remain at its last state.

The KK74HC651A has inverted outputs.

• Outputs Directly Interface to CMOS, NMOS, and TTL

• Operating Voltage Range: 2.0 to 6.0 V

• Low Input Current: 1.0 µA

• High Noise Immunity Characteristic of CMOS Devices

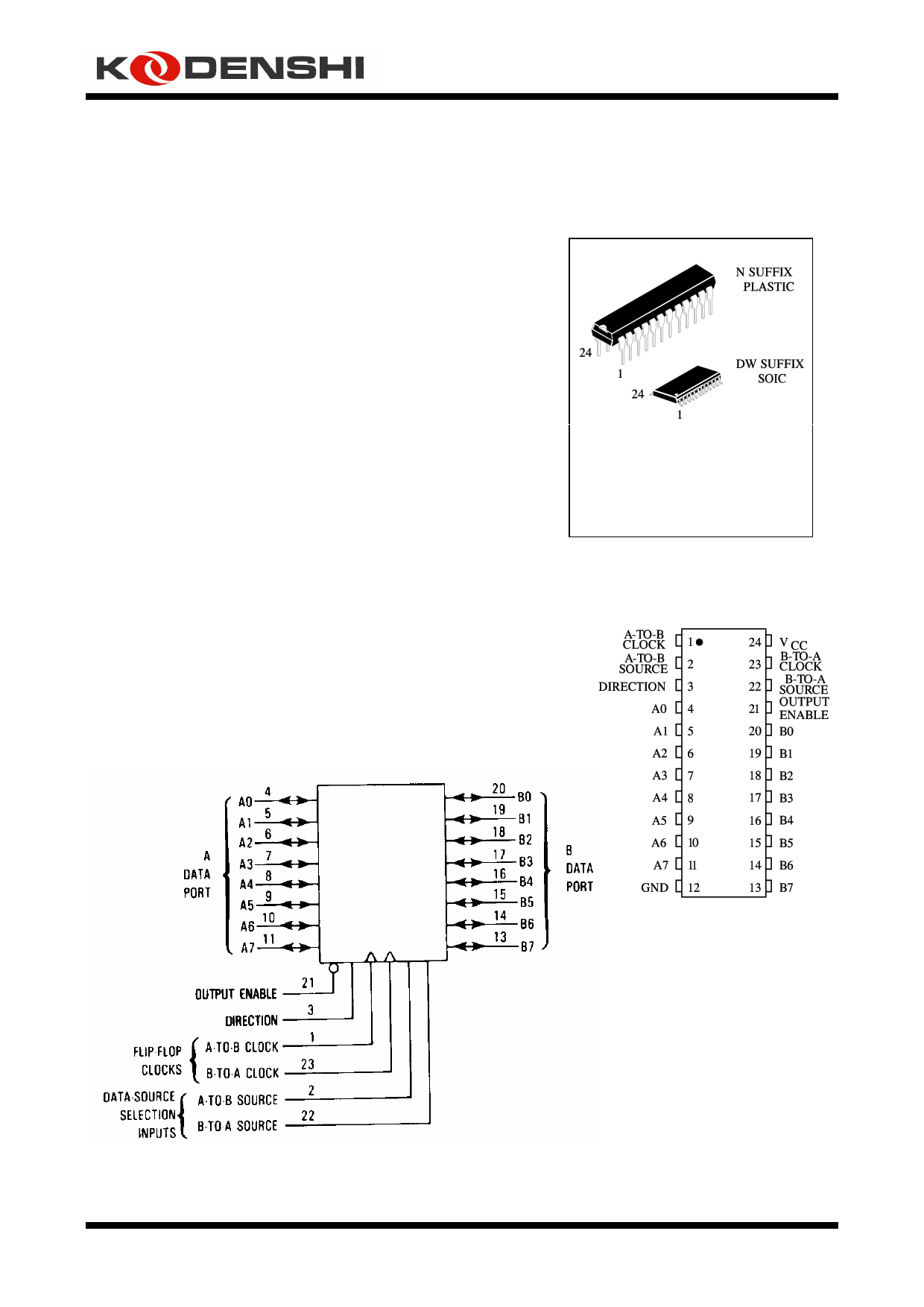

ORDERING INFORMATION

KK74HC651AN Plastic

KK74HC651ADW SOIC

TA = -55° to 125° C for all packages

PIN ASSIGNMENT

LOGIC DIAGRAM

www.DataSheet4U.net

PIN 24=VCC

PIN 12 = GND

1

1 page

KK74HC651A

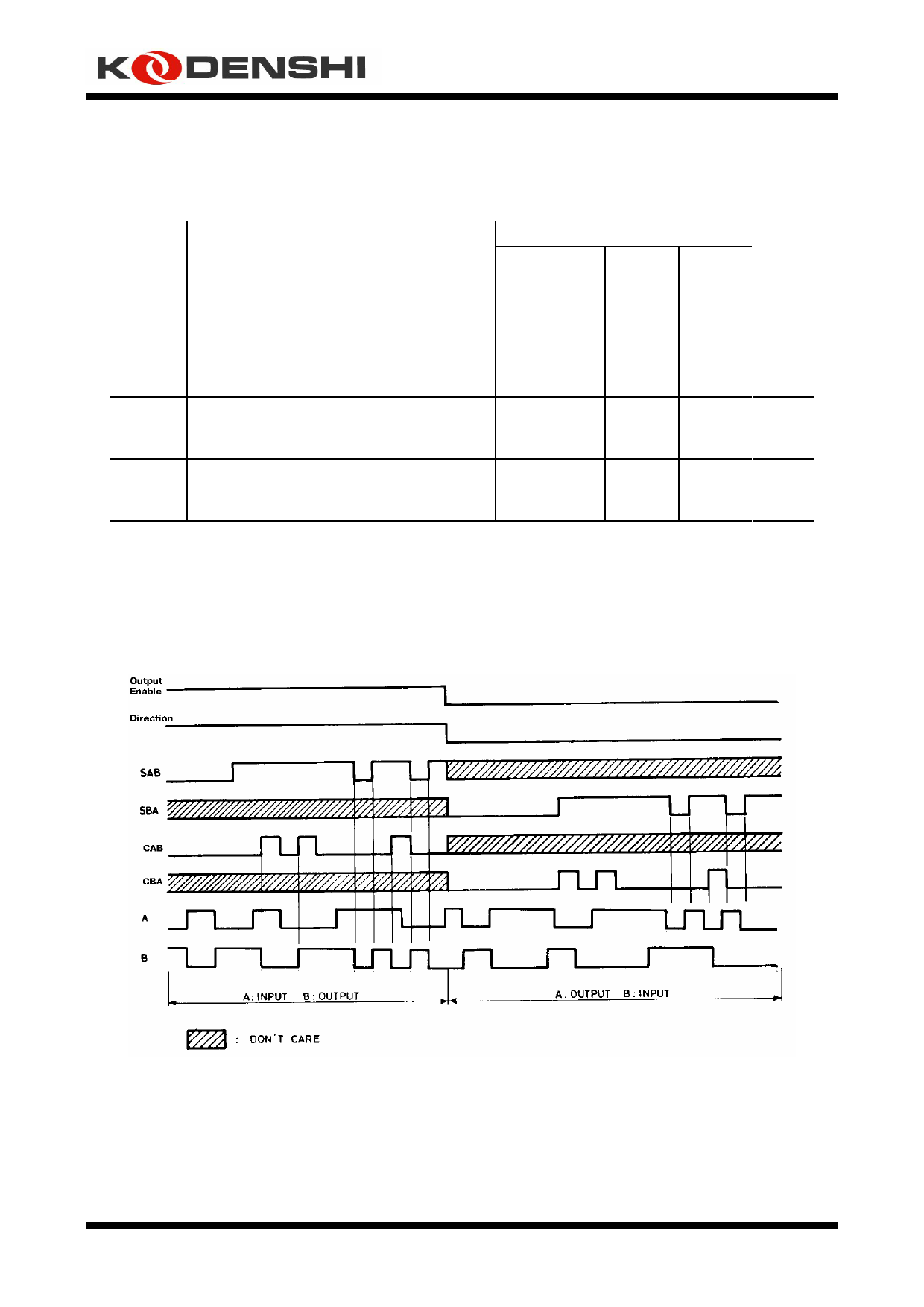

TIMING REQUIREMENTS (Input tr=tf=6.0 ns)

Symbol

tsu

th

tw

tr, tf

Parameter

Minimum Setup Time, Input A to

A-to-B Clock (or Input B to B-to-A

Clock) (Figure 7)

Minimum Hold Time, A-to-B Clock

to Input A (or B-to-A Clock to

Input B) (Figure 7)

Minimum Pulse Width, A-to-B Clock

(or B-to-A Clock)

(Figure 7)

Maximum Input Rise and Fall Times

(Figures 2 and 3)

VCC

V

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

2.0

4.5

6.0

Guaranteed Limit

25 °C to-55°C ≤85°C ≤125°C

50 65 75

10 13 15

9 11 13

25 30 40

5 68

5 57

75 95 110

15 19 22

13 16 19

1000

500

400

1000

500

400

1000

500

400

Unit

ns

ns

ns

ns

TIMING DIAGRAM

5

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet KK74HC651A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KK74HC651A | Octal 3-State Bus Transceivers and D Flip-Flops | KODENSHI KOREA |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |