|

|

PDF KM432D2131 Data sheet ( Hoja de datos )

| Número de pieza | KM432D2131 | |

| Descripción | 512K X 32Bit X 4 Banks Double Data Rate Synchronous Graphic RAM | |

| Fabricantes | Samsung Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de KM432D2131 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.net

KM432D2131

Target

64M DDR SGRAM

64Mbit DDR SGRAM

512K x 32Bit x 4 Banks

Double Data Rate Synchronous Graphic RAM

with Bi-directional Data Strobe

Revision 0.3

May 1999

Samsung Electronics reserves the right to change products or specification without notice.

-1-

Rev. 0.3 (May. 1999)

1 page

KM432D2131

Target

64M DDR SGRAM

INPUT/OUTPUT FUNCTIONAL DESCRIPTION

Symbol

Type

Function

CK, CK*1

Input

The differential system clock Input.

All of the inputs are sampled on the rising edge of the clock except

DQ′s and DM′s that are sampled on both edges of the DQS.

CKE

Input

Activates the CK signal when high and deactivates the CK signal

when low. By deactivating the clock, CKE low indicates the Power

down mode or Self refresh mode.

CS Input

CS enables the command decoder when low and disabled the com-

mand decoder when high. When the command decoder is disabled,

new commands are ignored but previous operations continue.

RAS

Input

Latches row addresses on the positive going edge of the CK with

RAS low. Enables row access & precharge.

CAS

Input

Latches column addresses on the positive going edge of the CK with

CAS low. Enables column access.

WE Input

Enables write operation and row precharge.

Latches data in starting from CAS, WE active.

DQS

Input/Output

Data input and output are synchronized with both edge of DQS.

DM0 ~ DM3

Input

Data In mask. Data In is masked by DM Latency=0 when DM is high

in burst write. DM0 for DQ0 ~ DQ7, DM1 for DQ8 ~ DQ15, DM2 for

DQ16 ~ DQ23, DM3 for DQ24 ~ DQ31.

DQ0 ~ DQ31

Input/Output

Data inputs/Outputs are multiplexed on the same pins.

BA0, BA1

Input

Selects which bank is to be active.

A0 ~ A10

Input

Row/Column addresses are multiplexed on the same pins.

Row addresses : RA0 ~ RA10, Column addresses : CA0 ~ CA7.

Column address CA8 is used for auto precharge.

VDD/VSS

Power Supply

Power and ground for the input buffers and core logic.

VDDQ/VSSQ

Power Supply

Isolated power supply and ground for the output buffers to provide

improved noise immunity.

VREF

Power Supply

Reference voltage for inputs, used for SSTL interface.

DSF, MCL

Define Special Function Enables block write and special mode register set and must be con-

nected low to disable these special functions.

*1 : The timing reference point for the differential clocking is the cross point of CK and CK.

For any applications using the single ended clocking, apply VREF to CK pin.

-5-

Rev. 0.3 (May. 1999)

5 Page

KM432D2131

Target

64M DDR SGRAM

BURST MODE OPERATION

Burst mode operation is used to provide a constant flow of data to memory locations(write cycle), or from memory loca-

tions(read cycle). There are two parameters that define how the burst mode operates. These parameters including burst

sequence and burst length are programmable and determined by address bits A0 ~ A3 during the Mode Register Set com-

mand. The burst type is used to define the sequence in which the burst data will be delivered or stored to the SGRAM.

Two types of burst sequences are supported, sequential and interleaved. See the below table. The burst length controls

the number of bits that will be output after a read command, or the number of bits to be input after a write command. The

burst length can be programmed to have values of 2, 4, 8 or Full page. For the full page operation, the starting address

must be an even number.

BURST LENGTH AND SEQUENCE

Burst Length

2

4

8

Starting Address(A2, A1, A0)

xx0

xx1

x00

x01

x10

x11

000

001

010

011

100

101

110

111

Sequential Mode

0, 1

1, 0

0, 1, 2, 3

1, 2, 3, 0

2, 3, 0, 1

3, 0, 1, 2

0, 1, 2, 3, 4, 5, 6, 7

1, 2, 3, 4, 5, 6, 7, 0

2, 3, 4, 5, 6, 7, 0, 1

3, 4, 5, 6, 7, 0, 1, 2

4, 5, 6, 7, 0, 1, 2, 3

5, 6, 7, 0, 1, 2, 3, 4

6, 7, 0, 1, 2, 3, 4, 5

7, 0, 1, 2, 3, 4, 5, 6

Interleave Mode

0, 1

1, 0

0, 1, 2, 3

1, 0, 3, 2

2, 3, 0, 1

3, 2, 1, 0

0, 1, 2, 3, 4, 5, 6, 7

1, 0, 3, 2, 5, 4, 7, 6

2, 3, 0, 1, 6, 7, 4, 5

3, 2, 1, 0, 7, 6, 5, 4

4, 5, 6, 7, 0, 1, 2, 3

5, 4, 7, 6, 1, 0, 3, 2

6, 7, 4, 5, 2, 3, 0, 1

7, 6, 5, 4, 3, 2, 1, 0

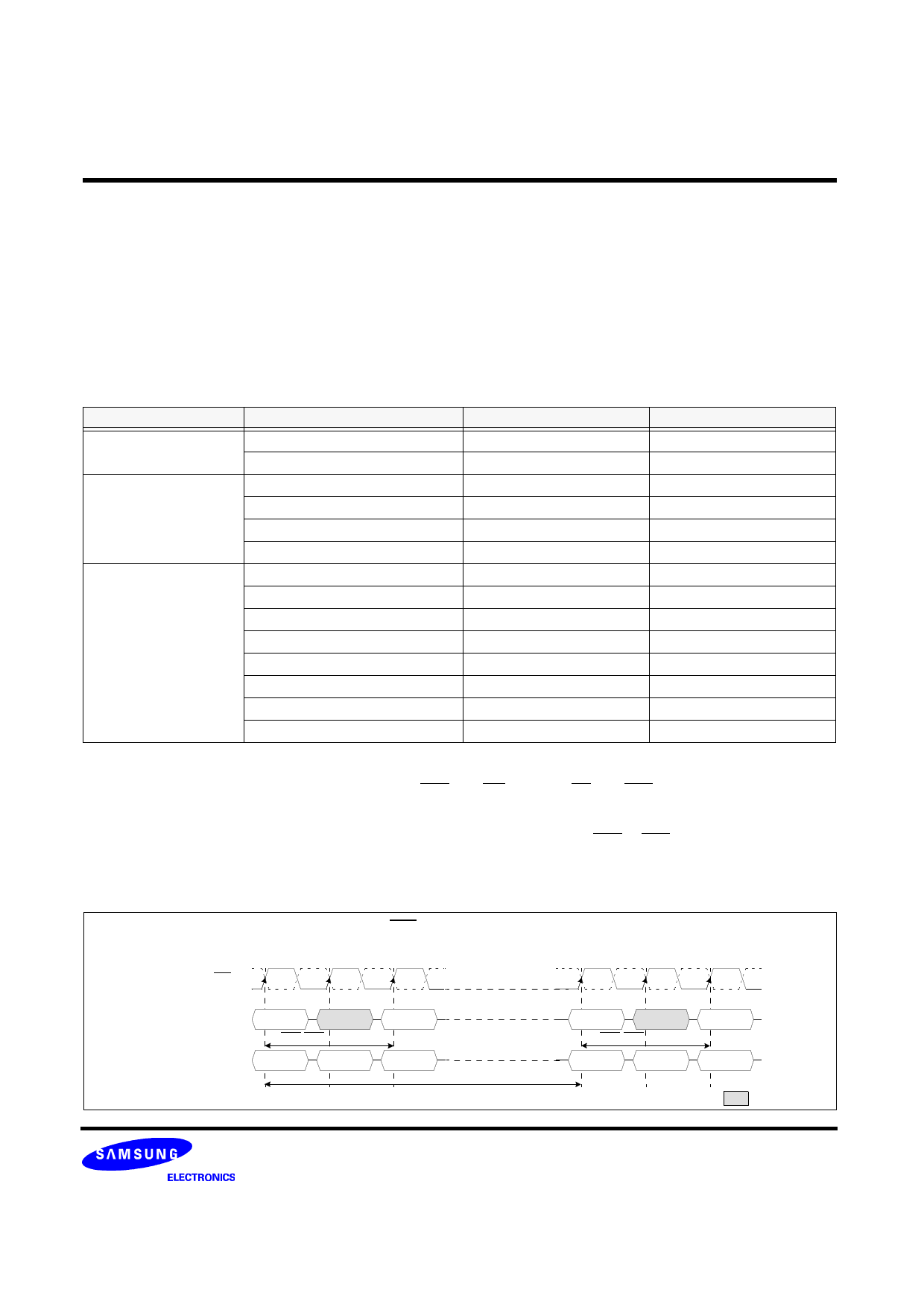

BANK ACTIVATION COMMAND

The Bank Activation command is issued by holding CAS and WE high with CS and RAS low at the rising edge of the

clock. The DDR SGRAM has four independent Banks, so two Bank Select addresses(BA0, BA1) are supported. The Bank

Activation command must be applied before any Read or Write operation is executed. The delay from the Bank Activation

command to the first read or write command must meet or exceed the minimum of RAS to CAS delay time(tRCD min). Once

a bank has been activated, it must be precharged before another Bank Activation command can be applied to the same

bank. The minimum time interval between interleaved Bank Activation commands(Bank A to Bank B and vice versa) is the

Bank to Bank delay time(tRRD min).

Bank Activation Command Cycle (CAS Latency = 2)

012

CK, CK

n n+1 n+2

Address

Command

Bank A

Row Addr.

Bank A

Col. Addr.

RAS-CAS delay(tRCD)

Bank A

Activate

NOP

Write A

with Auto

Precharge

ROW Cycle Time(tRC)

Bank A

Row Addr.

Bank B

Row. Addr.

RAS-RAS delay time(tRRD)

Bank A

Activate

NOP

Bank B

Activate

: Don′t care

- 11 -

Rev. 0.3 (May. 1999)

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet KM432D2131.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KM432D2131 | 512K X 32Bit X 4 Banks Double Data Rate Synchronous Graphic RAM | Samsung Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |