|

|

PDF SC16C850SV Data sheet ( Hoja de datos )

| Número de pieza | SC16C850SV | |

| Descripción | XScale VLIO bus interface | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SC16C850SV (archivo pdf) en la parte inferior de esta página. Total 46 Páginas | ||

|

No Preview Available !

SC16C850SV

1.8 V single UART, 20 Mbit/s (max.) with 128-byte FIFOs,

infrared (IrDA), and XScale VLIO bus interface

Rev. 01 — 8 July 2008

Product data sheet

1. General description

The SC16C850SV is a 1.8 V, low power single channel Universal Asynchronous Receiver

and Transmitter (UART) used for serial data communications. Its principal function is to

convert parallel data into serial data and vice versa. The UART can handle serial data

rates up to 20 Mbit/s (4× sampling rate). SC16C850SV can be programmed to operate in

extended mode where additional advanced UART features are available (see

Section 6.2).The SC16C850SV family UART provides enhanced UART functions with

128-byte FIFOs, modem control interface and IrDA encoder/decoder. On-board status

registers provide the user with error indications and operational status. System interrupts

and modem control features may be tailored by software to meet specific user

requirements. An internal loopback capability allows on-board diagnostics. Independent

programmable baud rate generators are provided to select transmit and receive baud

rates.

The SC16C850SV with Intel XScale processor VLIO interface operates at 1.8 V and is

available in the HVQFN32 package.

2. Features

I Single channel high performance UART

I 1.8 V operation

I Advanced package: HVQFN32

I Up to 20 Mbit/s data rate at 1.8 V

I Programmable sampling rates: 16×, 8×, 4×

I 128-byte transmit FIFO to reduce the bandwidth requirement of the external CPU

I 128-byte receive FIFO with error flags to reduce the bandwidth requirement of the

external CPU

I 128 programmable Receive and Transmit FIFO interrupt trigger levels

I 128 Receive and Transmit FIFO reporting levels (level counters)

I Automatic software (Xon/Xoff) and hardware (RTS/CTS or DTR/DSR) flow control

I Programmable Xon/Xoff characters

I 128 programmable hardware and software trigger levels

I Automatic 9-bit mode (RS-485) address detection

I Automatic RS-485 driver turn-around with programmable delay

I UART software reset

I High resolution clock prescaler, from 0 to 15 with granularity of 1⁄16 to allow

non-standard UART clock to be used

I Industrial temperature range (−40 °C to +85 °C)

www.DataSheet.in

1 page

NXP Semiconductors

SC16C850SV

Single UART with 128-byte FIFOs, IrDA, and XScale VLIO bus interface

Table 2. Pin description …continued

Symbol Pin

Type Description

INT 20

O Interrupt output. The output state is defined by the user through the software setting of

MCR[5]. INT is set to the active mode when MCR[5] is set to a logic 0. INT is set to the

open-source mode when MCR[3] is set to a logic 1. See Table 19.

IOR 14

I Read strobe (active LOW). A HIGH to LOW transition on this signal starts the read cycle.

The SC16C850SV reads a byte from the internal register and puts the byte on the data bus

for the host to retrieve.

IOW

12

I Write strobe (active LOW). A HIGH to LOW transition on this signal starts the write cycle,

and a LOW to HIGH transition transfers the data on the data bus to the internal register.

LLA 19

I Latch Lower Address (active LOW). A logic LOW on this pin puts the VLIO interface in the

address phase of the transaction, where the lower 8 bits of the VLIO (specifying the UART

register and the channel address) are loaded into the address latch of the device through

the AD7 to AD0 bus. A logic HIGH puts the VLIO interface in the data phase where data can

are transferred between the host and the UART.

LOWPWR 9

I Low Power. When asserted (active HIGH), the device immediately goes into low-power

mode. The oscillator is shut-off and some host interface pins are isolated from the host’s bus

to reduce power consumption. The device only returns to normal mode when the LOWPWR

pin is de-asserted. On the negative edge of a de-asserting LOWPWR signal, the device is

automatically reset and all registers return to their default reset states. This pin has an

internal pull-down resistor, therefore, it can be left unconnected.

n.c.

2, 15, 16, -

not connected

17, 18

RESET 23

I Master reset (active LOW). A reset pulse will reset the internal registers and all the

outputs. The SC16C850SV transmitter outputs and receiver inputs will be disabled during

reset time. (See Section 7.24 “SC16C850SV external reset condition and software reset” for

initialization details.)

RI 27 I Ring Indicator (active LOW). A logic 0 on this pin indicates the modem has received a

ringing signal from the telephone line. A logic 1 transition on this input pin will generate an

interrupt is modem status interrupt is enabled. Status can be tested by reading MCR[6].

RTS

21

O Request to Send (active LOW). A logic 0 on the RTS pin indicates the transmitter has data

ready and waiting to send. Writing a logic 1 in the modem control register MCR[1] will set

this pin to a logic 0, indicating data is available. After a reset this pin will be set to a logic 1.

RX 6

I UART receive data. The RX signal will be a logic 1 during reset, idle (no data), or when not

receiving data. During the local Loopback mode, the RX input pin is disabled and TX data is

connected to the UART RX input internally.

TX 7

O UART transmit data. The TX signal will be a logic 1 during reset, idle (no data), or when the

transmitter is disabled. During the local Loopback mode, the TX output pin is disabled and

TX data is internally connected to the UART RX input.

VDD

VSS

XTAL1

28

13[1]

10

I Power supply input.

I Signal and power ground.

I Crystal or external clock input. Functions as a crystal input or as an external clock input.

A crystal can be connected between this pin and XTAL2 to form an internal oscillator circuit.

Alternatively, an external clock can be connected to this pin to provide custom data rates

(see Section 6.9 “Programmable baud rate generator”). See Figure 4.

XTAL2 11

O Output of the crystal oscillator or buffered clock. Crystal oscillator output or buffered

clock output. Should be left open if an external clock is connected to XTAL1.

[1] HVQFN32 package die supply ground is connected to both VSS pin and exposed center pad. VSS pin must be connected to supply

ground for proper device operation. For enhanced thermal, electrical, and board level performance, the exposed pad needs to be

soldered to the board using a corresponding thermal pad on the board and for proper heat conduction through the board, thermal vias

need to be incorporated in the PCB in the thermal pad region.

SC16C850SV_1

Product data sheet

Rev. 01 — 8 July 2008

© NXP B.V. 2008. All rights reserved.

5 of 46

www.DataSheet.in

5 Page

NXP Semiconductors

SC16C850SV

Single UART with 128-byte FIFOs, IrDA, and XScale VLIO bus interface

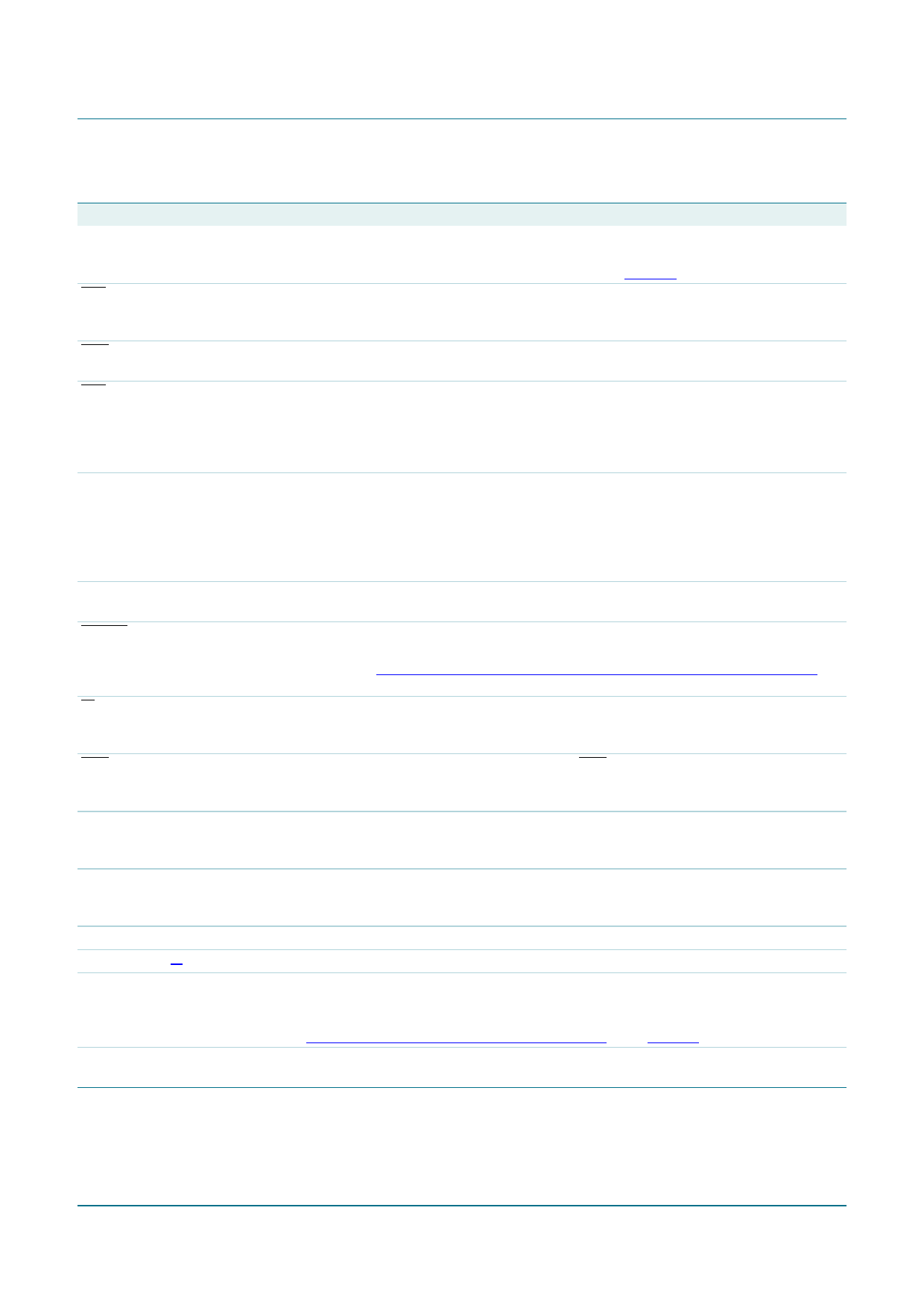

6.9 Programmable baud rate generator

The SC16C850SV UART contains a programmable rational baud rate generator that

takes any clock input and divides it by a divisor in the range between 1 and (216 − 1). The

SC16C850SV offers the capability of dividing the input frequency by rational divisor. The

fractional part of the divisor is controlled by the CLKPRES register in the First Extra

Register Set.

baud rate = -----------------------------------------f---X---T---A---L---1----------------------------------------

MCR[7] × SAMPR × N + S----A----MM-----P----R--

(1)

where:

N is the integer part of the divisor in DLL and DLM registers;

M is the fractional part of the divisor in CLKPRES register;

fXTAL1 is the clock frequency at XTAL1 pin;

SAMPR is the sampling rate in SAMPR register (16×, 8×, 4×); M / SAMPR should

always be less than 1.

Prescaler = 1 when MCR[7] is set to 0.

Prescaler = 4 when MCR[7] is set to 1.

SC16C850SV_1

Product data sheet

XTAL1

XTAL2

OSCILLATOR

DIVIDE-BY-1

MCR[7] = 0

DIVIDE-BY-4

MCR[7] = 1

CLKPRES

[3:0]

BAUD RATE

GENERATOR

(DLL, DLM)

transmitter and

receiver clock

002aac645

Fig 3. Prescalers and baud rate generator block diagram

A single baud rate generator is provided for the transmitter and receiver. The

programmable Baud Rate Generator is capable of operating with a frequency of up to

80 MHz. To obtain maximum data rate, it is necessary to use full rail swing on the clock

input. The SC16C850SV can be configured for internal or external clock operation. For

internal clock operation, an industry standard crystal is connected externally between the

XTAL1 and XTAL2 pins (see Figure 4). Alternatively, an external clock can be connected

to the XTAL1 pin (see Figure 5) to clock the internal baud rate generator for standard or

custom rates (see Table 6).

The generator divides the input 16× clock by any divisor from 1 to (216 − 1). The

SC16C850SV divides the basic external clock by 16. The baud rate is configured via the

CLKPRES, DLL and DLM internal register functions. Customized baud rates can be

achieved by selecting the proper divisor values for the MSB and LSB sections of baud rate

generator. However, the user can also select 8×, 4× sampling rate to operate at four times,

or two times faster than the 16× sampling rate (see Section 7.20 “Sampling rate

(SAMPR)”).

Rev. 01 — 8 July 2008

© NXP B.V. 2008. All rights reserved.

11 of 46

www.DataSheet.in

11 Page | ||

| Páginas | Total 46 Páginas | |

| PDF Descargar | [ Datasheet SC16C850SV.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SC16C850SV | XScale VLIO bus interface | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |