|

|

PDF SC16C850L Data sheet ( Hoja de datos )

| Número de pieza | SC16C850L | |

| Descripción | parallel bus interface | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SC16C850L (archivo pdf) en la parte inferior de esta página. Total 54 Páginas | ||

|

No Preview Available !

SC16C850L

1.8 V single UART, 5 Mbit/s (max.) with 128-byte FIFOs,

infrared (IrDA) and 16 mode or 68 mode parallel bus interface

Rev. 04 — 13 December 2007

Product data sheet

1. General description

The SC16C850L is a 1.8 V, low power, single channel Universal Asynchronous Receiver

and Transmitter (UART) used for serial data communications. Its principal function is to

convert parallel data into serial data and vice versa. The UART can handle serial data

rates up to 5 Mbit/s. The SC16C850L is functionally (software) compatible with the

SC16C650B. SC16C850L can be programmed to operate in extended mode (see

Section 6.2) where additional advanced UART features are available. The SC16C850L

UART provides enhanced UART functions with 128-byte FIFOs, modem control interface,

and IrDA encoder/decoder. On-board status registers provide the user with error

indications and operational status. System interrupts and modem control features may be

tailored by software to meet specific user requirements. An internal loopback capability

allows on-board diagnostics.

The SC16C850LIBS with Intel (16 mode) or Motorola (68 mode) bus host interface

operates at 1.8 V and is available in a very small (Micro-UART) HVQFN32 package.

The SC16C850LIET with Intel (16 mode) bus host interface operates at 1.8 V and is

available in a very small TFBGA36 package.

2. Features

I Single channel high performance UART

I Intel or Motorola bus interface selectable using 16/68 pin

I 1.8 V operation

I Up to 5 Mbit/s data rate

I 128-byte transmit FIFO to reduce the bandwidth requirement of the external CPU

I 128-byte receive FIFO with error flags to reduce the bandwidth requirement of the

external CPU

I 128 programmable Receive and Transmit FIFO interrupt trigger levels

I 128 Receive and Transmit FIFO reporting levels (level counters)

I Automatic software (Xon/Xoff) and hardware (RTS/CTS or DTR/DSR) flow control

I Industrial temperature range (−40 °C to +85 °C)

I 128 hardware and software trigger levels

I Automatic 9-bit mode (RS-485) address detection

I Automatic RS-485 driver turn-around with programmable delay

I UART software reset

I High resolution clock prescaler, from 0 to 15 with granularity of 1⁄16 to allow

non-standard UART clock to be used

I Programmable Xon/Xoff characters

www.DataSheet.in

1 page

NXP Semiconductors

SC16C850L

1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

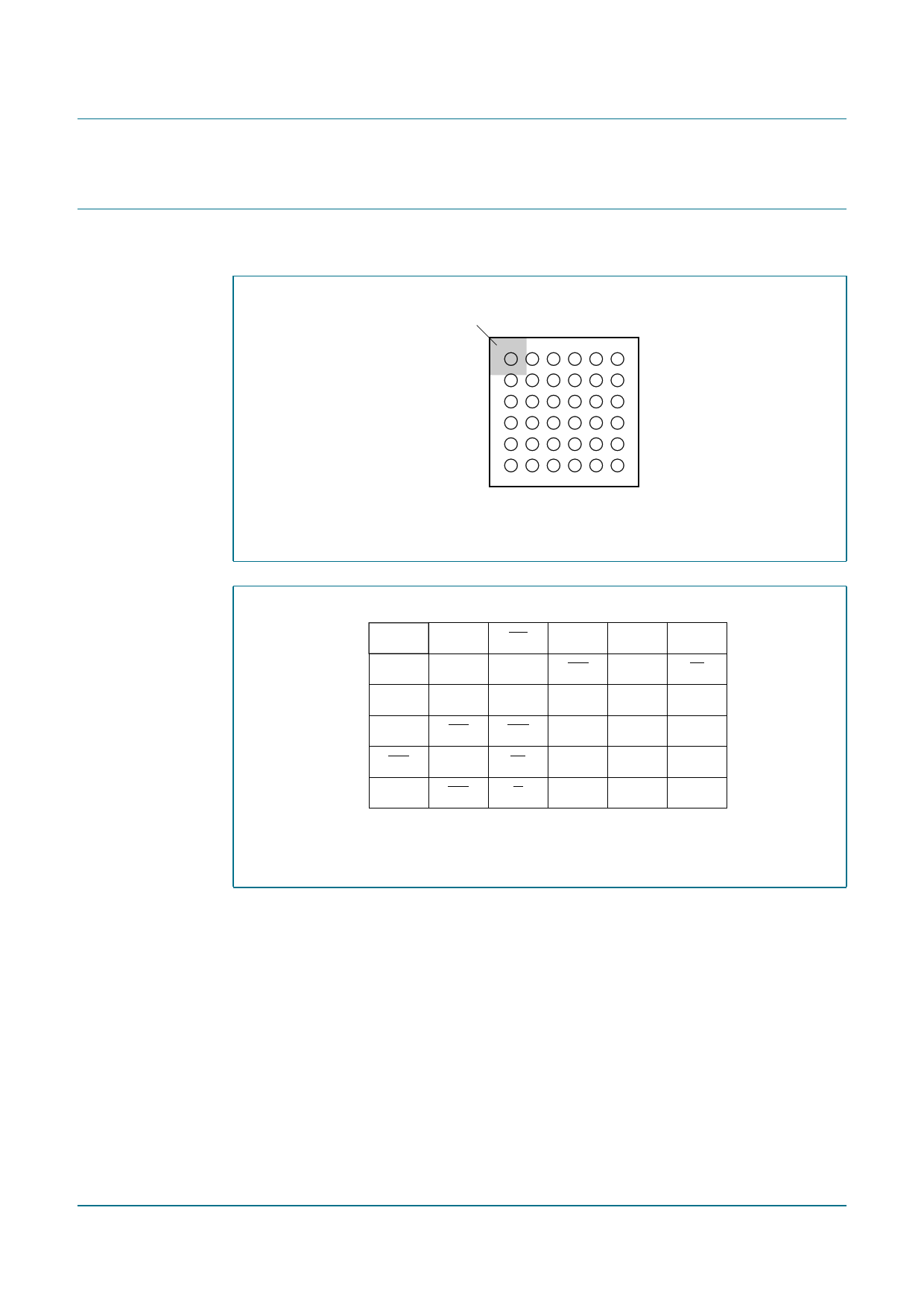

5. Pinning information

5.1 Pinning

ball A1

index area

SC16C850LIET

123456

A

B

C

D

E

F

002aac418

Transparent top view

Fig 3. Pin configuration for TFBGA36

123456

A VDD n.c. IOR n.c. XTAL2 XTAL1

B A2 n.c. n.c. IOW LOWPWR CS

C A0 VSS A1 VSS TX RX

D INT

E DTR

RTS

n.c.

CTS

CD

VDD

D1

D7

D3

D6

D5

F RESET

DSR

RI

D0

D2

D4

002aac421

Transparent top view.

Fig 4. Ball mapping for TFBGA36

SC16C850L_4

Product data sheet

www.DataSheet.in

Rev. 04 — 13 December 2007

© NXP B.V. 2007. All rights reserved.

5 of 54

5 Page

NXP Semiconductors

SC16C850L

1.8 V single UART with 128-byte FIFOs and IrDA encoder/decoder

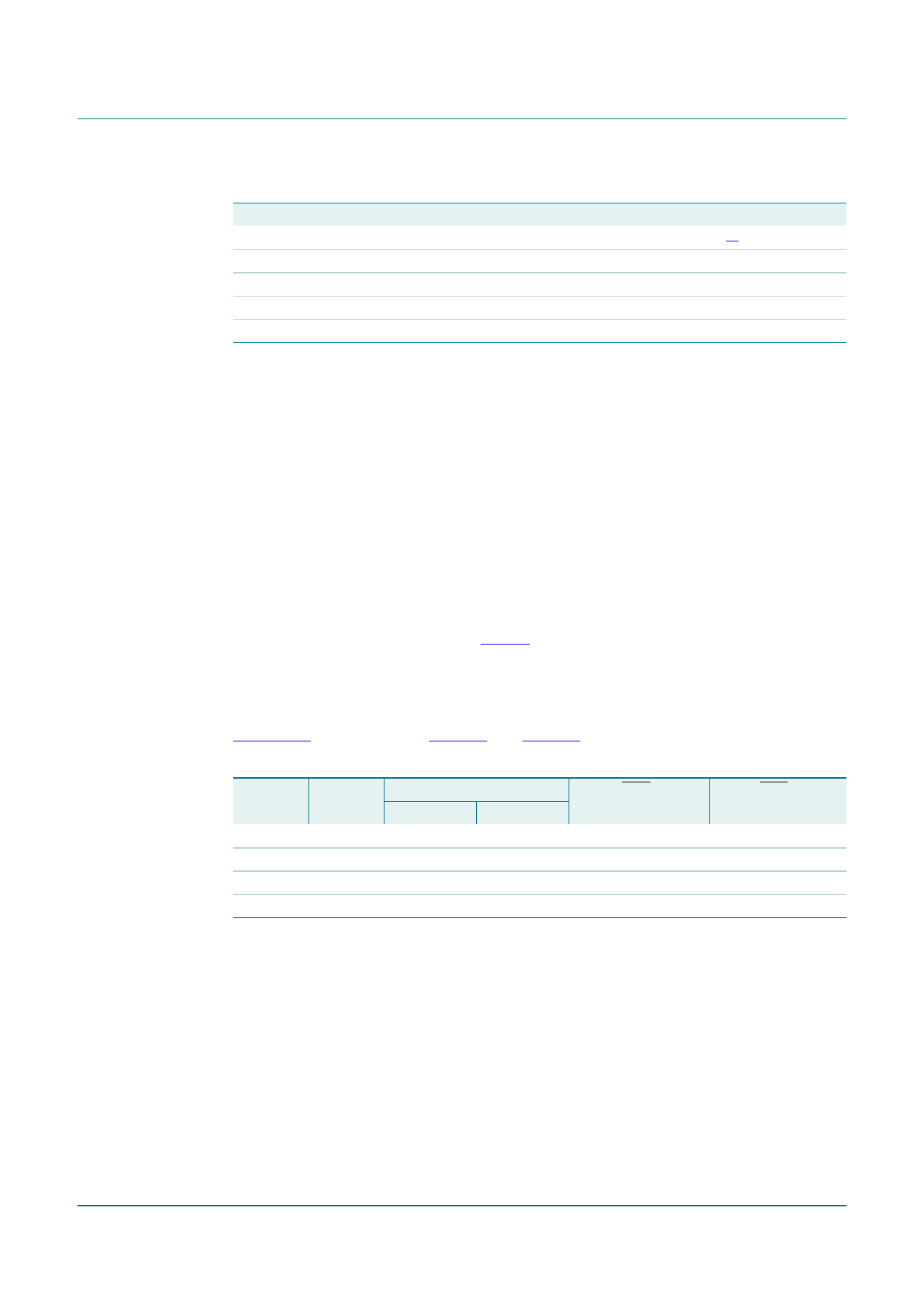

Table 5. Internal registers decoding …continued

A2 A1 A0 Read mode

Write mode

Second extra feature register set (CLKPRES, RS485TIME, AFCR2, AFCR1)[6]

0 1 0 Clock Prescaler

Clock Prescaler

1 0 0 RS-485 turn-around Timer

RS-485 turn-around Timer

1 1 0 Additional Feature Control Register 2 Additional Feature Control Register 2

1 1 1 Additional Feature Control Register 1 Additional Feature Control Register 1

[1] These registers are accessible only when LCR[7] is a logic 0.

[2] These registers are accessible only when LCR[7] is a logic 1.

[3] Second Special registers are accessible only when EFCR[0] = 1.

[4] Enhanced Feature Registers are only accessible when LCR = 0xBF.

[5] First Extra Feature Registers are only accessible when EFCR[2:1] = 01b.

[6] Second Extra Feature Registers are only accessible when EFCR[2:1] = 10b.

6.4 FIFO operation

6.4.1 32-byte FIFO mode

When all four of these registers (TXINTLVL, RXINTLVL, FLWCNTH, FLWCNTL) in the

‘first extra feature register set’ are empty (0x00) the transmit and receive trigger levels are

set by FCR[7:4]. In this mode the transmit and receive trigger levels are backward

compatible to the SC16C650B (see Table 6), and the FIFO sizes are 32 entries. The

transmit and receive data FIFOs are enabled by the FIFO Control Register bit 0 (FCR[0]).

It should be noted that the user can set the transmit trigger levels by writing to the FCR,

but activation will not take place until EFR[4] is set to a logic 1. The receiver FIFO section

includes a time-out function to ensure data is delivered to the external CPU (see

Section 6.8). Please refer to Table 11 and Table 12 for the setting of FCR[7:4].

Table 6. Interrupt trigger level and flow control mechanism

FCR[7:6] FCR[5:4] INT pin activation

RX TX

Negate RTS or

send Xoff

00 00 8

16 8

01 01 16

8

16

10 10 24 24 24

11 11 28 30 28

Assert RTS or

send Xon

0

7

15

23

6.4.2 128-byte FIFO mode

When either TXINTLVL, RXINTLVL, FLWCNTH or FLWCNTL in the ‘first extra feature

register set’ contains any value other than 0x00, the transmit and receive trigger levels are

set by TXINTLVL and RXINTLVL registers. TXINTLVL sets the trigger levels for the

transmit FIFO, and the transmit trigger levels can be set to any value between 1 and 128

with granularity of 1. RXINTLVL sets the trigger levels for the receive FIFO, the receive

trigger levels can be set to any value between 1 and 128 with granularity of 1.

When the effective FIFO size changes (that is, when FCR[0] toggles or when the

combined content of TXINTLVL, RXINTLVL, FLWCNTH and FLWCNTL changes between

equal and unequal to 0x00), both RX FIFO and TX FIFO will be reset (data in the FIFO will

be lost).

SC16C850L_4

Product data sheet

Rev. 04 — 13 December 2007

© NXP B.V. 2007. All rights reserved.

11 of 54

www.DataSheet.in

11 Page | ||

| Páginas | Total 54 Páginas | |

| PDF Descargar | [ Datasheet SC16C850L.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SC16C850 | parallel bus interface | NXP Semiconductors |

| SC16C850L | parallel bus interface | NXP Semiconductors |

| SC16C850SV | XScale VLIO bus interface | NXP Semiconductors |

| SC16C850V | XScale VLIO bus interface | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |