|

|

PDF PAS6311LT Data sheet ( Hoja de datos )

| Número de pieza | PAS6311LT | |

| Descripción | CMOS VGA DIGITAL IMAGE SESNSOR | |

| Fabricantes | Pixart Imaging | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de PAS6311LT (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

PAS6311LT Specification

PAS6311LT CMOS VGA DIGITAL IMAGE SESNSOR

General Description

The PAS6311LT is a highly integrated CMOS active-pixel image sensor that has a VGA resolution of

648H x 488V. It embedded the new FinePixel™ sensor technology to perform the excellent image quality. The

PAS6311LT outputs 10-bit RGB raw data through a parallel data bus. It is available in 24-pin CSP.

The PAS6311LT can be programmed to set the exposure time for different luminance condition via I2CTM

serial control bus. By programming the internal register set, it performs on-chip frame rate adjustment, offset

correction DAC and programmable gain control.

Features

z VGA(640x480) resolution, ~1/6” Lens.

z Bayer RGB color filter array.

z 10-bits parallel RGB raw data output.

z On-Chip 10-bits pipeline A/D converter.

z On-Chip programmable gain amplifier

3-bits front gain amplifier.

7-bits color gain amplifier.

7-bits global gain amplifier.

z Digital gain stage.

z Continuous variable frame time.

z Continuous variable exposure time.

z I2CTM interface.

z Flash light timing

z 1.8V~3.3V I/O voltage

z <15mA power dissipation ( 30fps / 2.5v ).

z 10uA low power-down dissipation.

z Window-of-Interest (WOI).

z Sub-sampling.

z Defect compensation.

z Lens shading compensation.

z Companding

z Automatic background compensation

z Critical register table backward compatible

with PAS6302

z Ball to ball compatible with PAS6302CS

Key Specification

Supply

voltage

Analog

Core

I/O

Resolution

Array Diagonal

Pixel Size

Max. Frame Rate

Max. System Clock

Max. Pixel Clock

Color Filter

Exposure Time

Scan Mode

Sensitivity

S/N Ratio

Dark Current

Chief Ray Angle

Package Type

2.5V

1.8V

1.8V ~ 3.3V

640 ( H ) x 480 ( V )

2.91mm ( ~1/6” Optic )

3.6 m x 3.6 m

~30 fps @ 0.3Mega

Up to 48MHz

Up to 12MHz

RGB Bayer Pattern

~ Frame time to Line time

Progressive

1.3V/(Lux*Sec)

41dB

12mV/sec at 6

22 ~ 25 degree

24-ball CSP

All rights strictly reserved any portion in this paper shall not be reproduced, copied or transformed to any other forms without permission.

1

PixArt Imaging Inc.

E-mail: [email protected]

v1.5 2007/10/02

www.DataSheet.in

1 page

PAS6311LT Specification

Figure 3.2 Companding curves program by Compand_EnH and Compand_Sel

3.4. Power Down Mode

The PAS6311LT can enter power-down mode by setting register “SW_PwrDn” or by enabling CSB pin.

PAS6311LT supports two power-down modes :

z Software Power Down : Setting register “SW_PwrDn” = 0x01 could have power-down effect

upon all the internal block except I2CTM.

z Hardware Power Down : Pulling CSB pin to high could have power-down effect upon the

whole chip. The chip will go into standby state.

3.5. Reset Mode

The PAS6311LT can be reset by setting register “SW_Reset” or by enabling Reset pin. PAS6311LT

supports two reset modes :

z Software Reset : Set register “SW_Reset” = 0x01 to reset all the I2CTM registers. It resets the

register value only and non-whole chip.

z HardwareReset : Pull Reset pin to high to reset the whole chip.

3.6. Automatic Background Compensation (ABC)

By setting register “ABC_en” = 0x01, PAS6311LT can do the black-level calibration automatically. The

purpose of this function supports user to set Dac value by hardware self-calculation to make dark like real

dark.

All rights strictly reserved any portion in this paper shall not be reproduced, copied or transformed to any other forms without permission.

5

PixArt Imaging Inc.

E-mail: [email protected]

v1.5 2007/10/02

www.DataSheet.in

5 Page

PAS6311LT Specification

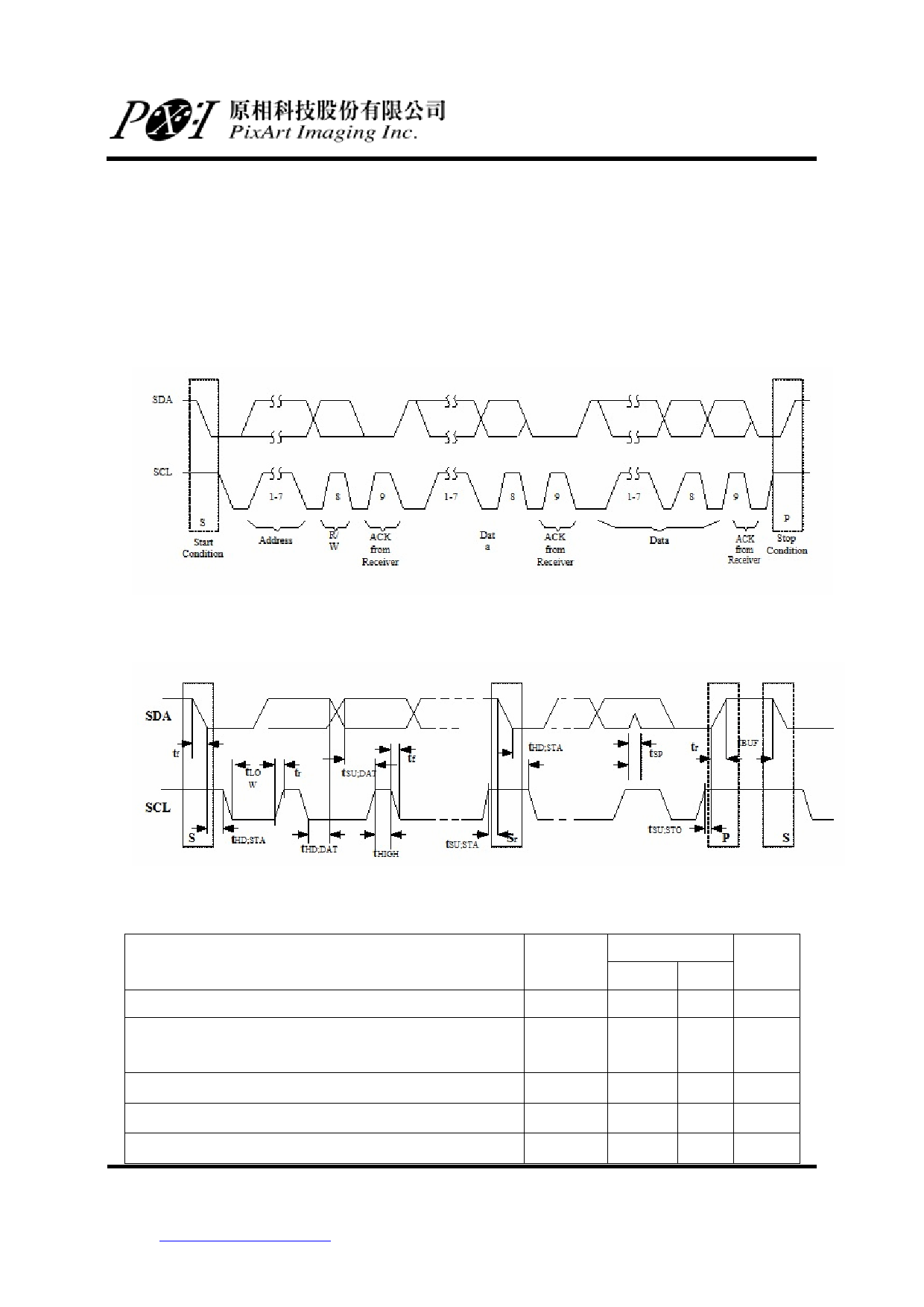

During read cycle, the master generates start condition and then place the 1st byte data that are combined

slave address ( 7 bits ) with a read / write control bit to SDA line. After issue acknowledgment, 8 bits

DATA was also placed on SDA line by PAS6311LT. The 8 bits data was read from PAS6311LT internal

control register that address was assigned by previous write cycle. Follow the master acknowledgment,

the PAS6311LT place the next 8 bits data ( address is increment automatically ) on SDA line and then

transmit to master serially. The DATA and Am cycles is repeat until the last byte read. After last byte

read, Am is no longer generated by master but instead by keep SDA line high. The slave ( PAS6311LT )

must releases SDA line to master to generate STOP condition.

4.3. I2CTM Bus Timing

4.4. I2CTM Bus Timing Specification

Parameter

SCL clock frequency.

Hold time ( repeated ) Start condition.

After this period, the first clock pulse is generated.

Symbol

fscl

tHD:STA

Standard Mode

Min. Max

10 400

4.0 -

Unit

KHz

s

Low period of the SCL clock.

High period of the SCL clock.

Set-up time for a repeated START condition.

tLOW

tHIGH

tSU;STA

4.7

0.75

4.7

-

-

-

s

s

s

All rights strictly reserved any portion in this paper shall not be reproduced, copied or transformed to any other forms without permission.

11

PixArt Imaging Inc.

E-mail: [email protected]

v1.5 2007/10/02

www.DataSheet.in

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet PAS6311LT.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PAS6311LT | CMOS VGA DIGITAL IMAGE SESNSOR | Pixart Imaging |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |