|

|

PDF DS28E10 Data sheet ( Hoja de datos )

| Número de pieza | DS28E10 | |

| Descripción | 1-Wire SHA-1 Authenticator | |

| Fabricantes | Maxim Integrated Products | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de DS28E10 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

ABRIDGED DATA SHEET

219-0009; Rev 2; 4/11

EVAALVUAAILTAIOBNLEKIT

1-Wire SHA-1 Authenticator

General Description

The DS28E10 combines secure challenge-and-response

authentication functionality based on the FIPS 180-3

specified Secure Hash Algorithm (SHA-1) with 224 bits

of one-time programmable user EPROM in a single

chip. Once written, the memory is automatically write

protected. Additionally, each device has its own guaran-

teed unique 64-bit ROM identification number (ROM ID)

that is factory programmed into the chip. Memory writes

are performed 4 bytes at a time. A secure and low-cost

factory programming service is available to preprogram

device data, including the SHA-1 security data compo-

nents. The device communicates over the single-contact

1-Wire® bus. The communication follows the standard

1-Wire protocol with the ROM ID acting as node address

in the case of a multidevice 1-Wire network.

Applications

Reference Design License Management

System Intellectual Property Protection

Sensor/Accessory Authentication and Calibration

Ordering Information

PART

TEMP RANGE

PIN-PACKAGE

DS28E10R+T

-40NC to +85NC

3 SOT23

DS28E10P+

-40NC to +85NC

6 TSOC

DS28E10P+T

-40NC to +85NC

6 TSOC

+Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

Features

S Dedicated Hardware-Accelerated SHA-1 Engine

for Generating SHA-1 MACs

S One Page of 28 Bytes User OTP EPROM

S Irreversible Write Protection

S Unique, Factory-Programmed 64-Bit Identification

Number

S 1-Wire Interface for Standard and Overdrive Speed

S Communicates with Host at Up to 15.4kbps at

Standard Speed or Up to 125kbps in Overdrive Mode

S Operating Range from 2.8V to 3.6V, -40NC to +85NC

S 3-Lead SOT23, 6-Lead TSOC Package

S ±6kV Human Body Model (HBM) ESD Protection

(typ) on 1-Wire and VCC Pin

Typical Operating Circuit

3.3V

VCC

µC

Px.1

RPUP

VCC

1-Wire IO DS28E10

GND GND

1-Wire is a registered trademark of Maxim Integrated Products, Inc.

________________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

1 page

ABRIDGED DATA SHEET

1-Wire SHA-1 Authenticator

IO (1-Wire)

1-Wire FUNCTION

CONTROL

64-BIT

ROM ID

VCC

POWER

DISTRIBUTION

GND

DS28E10

MEMORY AND

SHA-1 FUNCTION

CONTROL UNIT

CRC-16

GENERATOR

224 BITS USER

MEMORY

REGISTERS

512-BIT

SHA-1 ENGINE

CHALLENGE BUFFER

SECURITY DATA

Figure 1. Block Diagram

COMMAND LEVEL:

1-Wire ROM

FUNCTION COMMANDS

AVAILABLE COMMANDS:

READ ROM

MATCH ROM

SEARCH ROM

SKIP ROM

RESUME

OVERDRIVE-SKIP ROM

OVERDRIVE-MATCH ROM

DS28E10

DATA FIELD AFFECTED:

64-BIT ROM ID, RC-FLAG

64-BIT ROM ID, RC-FLAG

64-BIT ROM ID, RC-FLAG

RC-FLAG

RC-FLAG

RC-FLAG, OD-FLAG

64-BIT ROM ID, RC-FLAG, OD-FLAG

DEVICE-SPECIFIC MEMORY

FUNCTION COMMANDS

Refer to the full data sheet.

Figure 2. Hierarchical Structure for 1-Wire Protocol

MSB

8-BIT

CRC CODE

MSB

Figure 3. 64-Bit ROM ID

LSB MSB

48-BIT SERIAL NUMBER

LSB

8-BIT FAMILY CODE

LSB MSB

LSB

5

5 Page

ABRIDGED DATA SHEET

1-Wire SHA-1 Authenticator

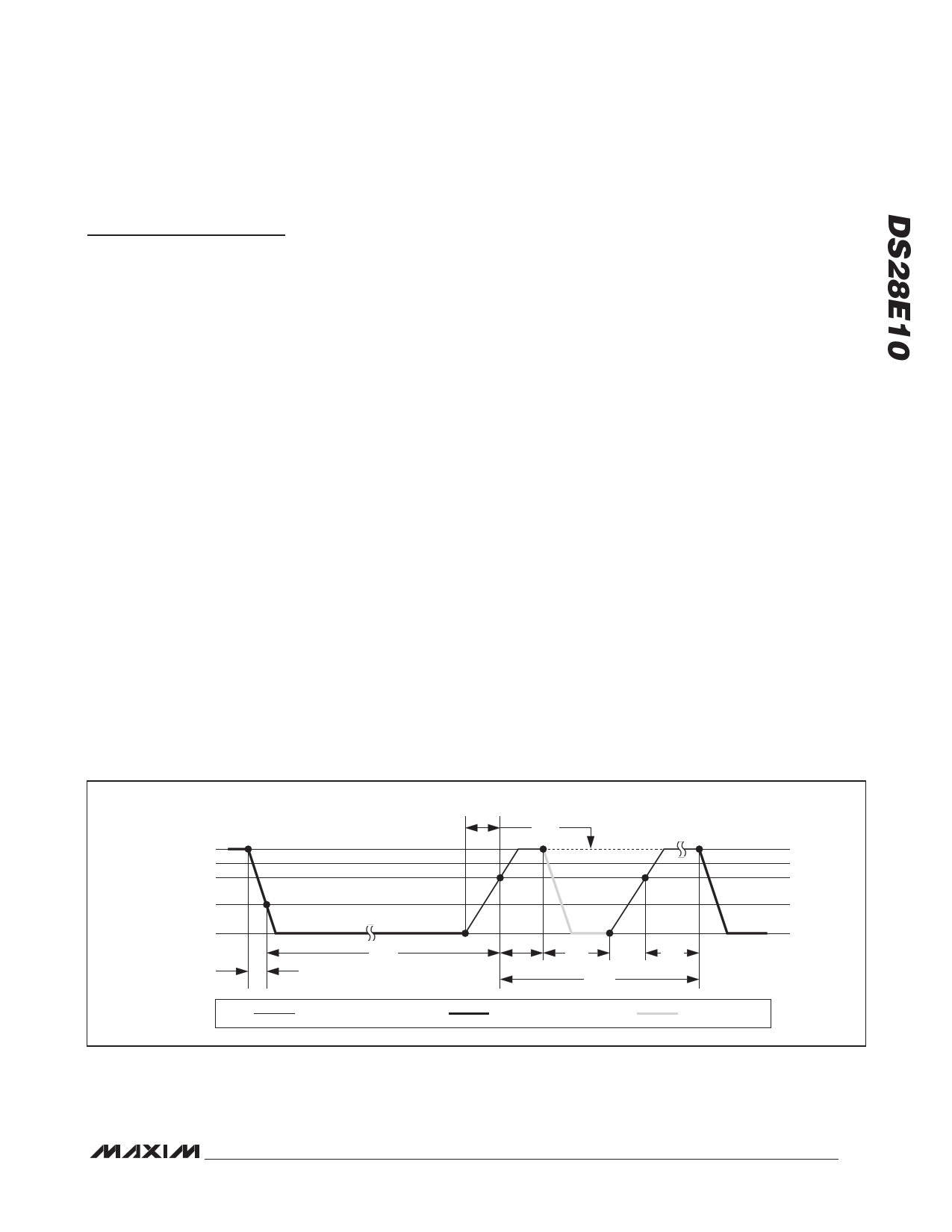

1-Wire Signaling

The DS28E10 requires strict protocols to ensure data

integrity. The protocol consists of four types of signaling

on one line: reset sequence with reset pulse and pres-

ence pulse, write-zero, write-one, and read-data. Except

for the presence pulse, the bus master initiates all falling

edges. The DS28E10 can communicate at two different

speeds: standard speed and overdrive speed. If not

explicitly set into the overdrive mode, the DS28E10 com-

municates at standard speed. While in overdrive mode

the fast timing applies to all waveforms.

To get from idle to active, the voltage on the 1-Wire line

needs to fall from VPUP below the threshold VIL. To get

from active to idle, the voltage needs to rise from 0V

past the threshold VIH. The time it takes for the voltage

to make this rise is seen in Figure 9 as ε, and its dura-

tion depends on the pullup resistor (RPUP) used and the

capacitance of the 1-Wire network attached.

Figure 9 shows the initialization sequence required to

begin any communication with the DS28E10. A reset

pulse followed by a presence pulse indicates that the

DS28E10 is ready to receive data, given the correct

ROM and memory function command. If the bus master

uses slew-rate control on the falling edge, it must pull

down the line for tRSTL + tF to compensate for the edge.

A tRSTL duration of 480Fs or longer exits the overdrive

mode, returning the device to standard speed. If the

DS28E10 is in overdrive mode and tRSTL is no longer

than 80Fs, the device remains in overdrive mode. If the

device is in overdrive mode and tRSTL is between 80Fs

and 480Fs, the device resets, but the communication

speed is undetermined.

After the bus master has released the line it goes into

receive mode. Now the 1-Wire bus is pulled to VPUP

through the pullup resistor, or in case of a DS2482-x00

driver, by active circuitry. When the threshold VIH is

crossed, the DS28E10 waits for tPDH and then transmits

a presence pulse by pulling the line low for tPDL. To

detect a presence pulse, the master must test the logical

state of the 1-Wire line at tMSP.

The tRSTH window must be at least the sum of

tPDHMAX, tPDLMAX, and tRECMIN. Immediately after

tRSTH is expired, the DS28E10 is ready for data com-

munication. In a mixed population network, tRSTH should

be extended to minimum 480Fs at standard speed and

48Fs at overdrive speed to accommodate other 1-Wire

devices.

Read/Write Time Slots

Data communication with the DS28E10 takes place in

time slots, which carry a single bit each. Write time slots

transport data from bus master to slave. Read time slots

transfer data from slave to master. Figure 10 illustrates

the definitions of the write and read time slots.

All communication begins with the master pulling the

data line low. As the voltage on the 1-Wire line falls below

the threshold VIL, the DS28E10 starts its internal timing

generator that determines when the data line is sampled

MASTER Tx "RESET PULSE"

VPUP

VIHMASTER

VIH

VIL

0V

tF

tRSTL

RESISTOR

Figure 9. Initialization Procedure: Reset and Presence Pulse

MASTER Rx "PRESENCE PULSE"

ε tMSP

tPDH

MASTER

tPDL

tRSTH

tREC

DS28E10

17

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet DS28E10.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS28E10 | 1-Wire SHA-1 Authenticator | Maxim Integrated Products |

| DS28E15 | DeepCover Secure Authenticator | Maxim Integrated |

| DS28E17 | 1-Wire-to-I2C Master Bridge | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |