|

|

PDF CBTL06122 Data sheet ( Hoja de datos )

| Número de pieza | CBTL06122 | |

| Descripción | High-performance DisplayPort/PCIe Gen2 hex display multiplexer | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CBTL06122 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

CBTL06122

www.DataSheet4U.com

High-performance DisplayPort/PCIe Gen2 hex display

multiplexer

Rev. 02 — 16 April 2009

Product data sheet

1. General description

The CBTL06122 is a six-channel (‘hex’) multiplexer for DisplayPort and PCI Express Gen2

applications. It provides four differential channels capable of switching or multiplexing

(bidirectional and AC-coupled) PCI Express Gen2 or DisplayPort signals, using

high-bandwidth pass-gate technology. Additionally, it provides for switching/multiplexing of

the Hot Plug Detect signal as well as the AUX or DDC (Direct Display Control) signals, for

a total of six channels.

The CBTL06122 is designed for high-performance PCI Express Gen2 and DisplayPort

applications. The device is available in two different pinouts (A and B, orderable as

separate part numbers) to suit different motherboard layout requirements.

The typical application of CBTL06122 is on motherboards, docking stations or add-in

cards where the graphics and I/O system controller chip utilizes I/O pins that are

configurable for either PCI Express or DisplayPort operation. The hex display MUX can be

used in such applications to route the signal from the controller chip to either a physical

DisplayPort connector or a PCI Express connector using its 1 : 2 multiplexer topology. The

controller chip selects which path to use by setting a select signal (which can be latched)

HIGH or LOW.

Optionally, the hex MUX device can be used in conjunction with an HDMI/DVI level shifter

device (PTN3300A, PTN3300B or PTN3301) to allow for DisplayPort as well as HDMI/DVI

connectivity.

1 page

NXP Semiconductors

5. Functional diagram

CBTL06122

www.DataSheet4U.com

High-performance DP/PCIe Gen2 hex display multiplexer

MULTI-MODE

DISPLAY SOURCE

PCIe PHY

ELECTRICAL

PCIe

output buffer

TX

PCIe

output buffer

TX

PCIe

output buffer

TX

PCIe

output buffer

TX

PCIe

input buffer

RX

PCIe

input buffer

RX

TX

Fig 4. Functional diagram

CBTL06122_2

Product data sheet

SEL

LE_N

MUX

LOGIC

XSD

AC-coupled

differential pair

DATA LANE

IN_0+

IN_0−

AC-coupled

differential pair

DATA LANE

IN_1+

IN_1−

AC-coupled

differential pair

DATA LANE

IN_2+

IN_2−

AC-coupled

differential pair

DATA LANE

IN_3+

IN_3−

X+

X−

AUX DATA

OUT+

OUT−

CBTL06122

D0+

D0−

TX0+

TX0−

D1+

D1−

TX1+

TX1−

D2+

D2−

TX2+

TX2−

D3+

D3−

TX3+

TX3−

HPD

RX1+

X− to RX1− path matches

X+ to RX1+ path

SPARE

RX1−

AUX+

AUX−

RX0+

RX0−

PEG CONNECTOR

OR

DOCKING CONNECTOR

002aad652

Rev. 02 — 16 April 2009

© NXP B.V. 2009. All rights reserved.

5 of 19

5 Page

NXP Semiconductors

CBTL06122

www.DataSheet4U.com

High-performance DP/PCIe Gen2 hex display multiplexer

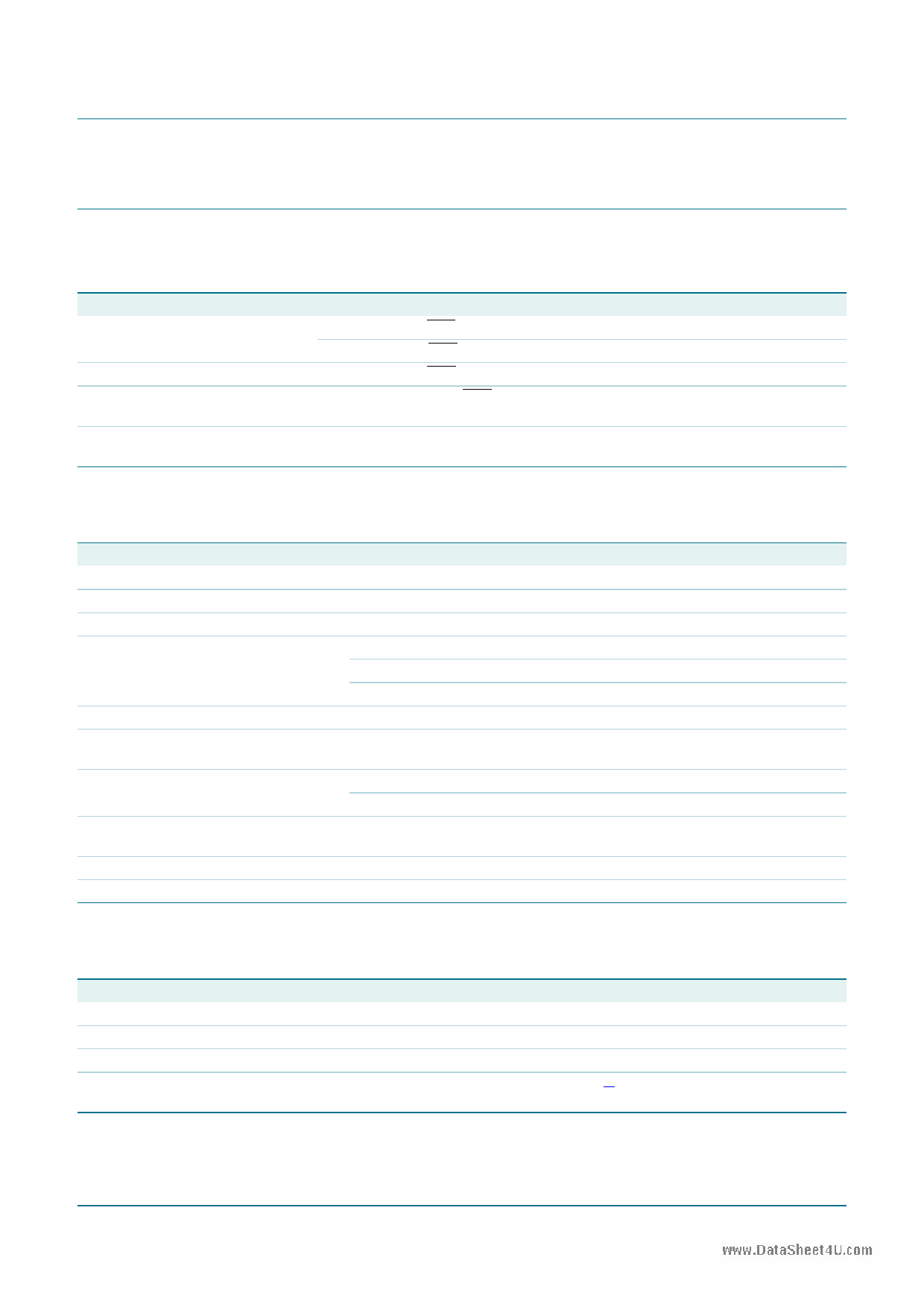

10. Characteristics

10.1 General characteristics

Table 8. General characteristics

Symbol Parameter

Conditions

Min Typ

IDD

Ptot

tstartup

supply current

total power dissipation

start-up time

operating mode (XSD = HIGH); VDD = 3.3 V

shutdown mode (XSD = LOW); VDD = 3.3 V

operating mode (XSD = HIGH); VDD = 3.3 V

supply voltage valid or XSD going HIGH to

channel specified operating characteristics

-

-

-

-

0.2

-

-

-

trcfg reconfiguration time SEL state change to channel specified

operating characteristics

--

10.2 DisplayPort channel characteristics

Table 9. DisplayPort channel characteristics

Symbol Parameter

Conditions

VI

VIC

VID

DDIL

input voltage

common-mode input voltage

differential input voltage

differential insertion loss

channel is on; 0 Hz ≤ f ≤ 1.0 GHz

channel is on; f = 2.5 GHz

channel is off; 0 Hz ≤ f ≤ 3.0 GHz

DDRL differential return loss

channel is on; 0 Hz ≤ f ≤ 1.0 GHz

DDNEXT differential near-end crosstalk adjacent channels are on;

0 Hz ≤ f ≤ 1.0 GHz

B bandwidth

−3.0 dB intercept

−5.0 dB intercept

tPD propagation delay

from left-side port to right-side port

or vice versa

tsk(dif)

tsk

differential skew time

skew time

intra-pair

inter-pair

Min Typ

−0.3 -

0-

−1.2 -

−2.5 −1.6

−4.5 -

--

--

--

- 2.5

- 4.0

- 180

--

--

10.3 AUX and DDC ports

Table 10.

Symbol

VI

VIC

VID

tPD

AUX and DDC port characteristics

Parameter

Conditions

input voltage

DDC or AUX

common-mode input voltage DDC or AUX

differential input voltage

propagation delay

from left-side port to right-side port

or vice versa

Min

−0.3

0

−1.2

[1] -

Typ

-

-

-

180

[1] Time from DDC/AUX input changing state to AUX output changing state. Includes DDC/AUX rise/fall time.

Max

1

10

5

1

1

Max

+2.6

2.0

+1.2

-

-

−20

−10

−30

-

-

-

5

180

Max

+2.6

2.0

+1.2

-

Unit

mA

µA

mW

ms

ms

Unit

V

V

V

dB

dB

dB

dB

dB

GHz

GHz

ps

ps

ps

Unit

V

V

V

ps

CBTL06122_2

Product data sheet

Rev. 02 — 16 April 2009

© NXP B.V. 2009. All rights reserved.

11 of 19

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet CBTL06122.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CBTL06121 | Gen1 hex display multiplexer | NXP Semiconductors |

| CBTL06122 | High-performance DisplayPort/PCIe Gen2 hex display multiplexer | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |