|

|

PDF K1B5616BBM Data sheet ( Hoja de datos )

| Número de pieza | K1B5616BBM | |

| Descripción | 256Mb (16M x 16 bit) UtRAM | |

| Fabricantes | Samsung Electronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de K1B5616BBM (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

K1B5616BA(B)M

Preliminary

UtRAM

www.DataSheet4U.com

256Mb (16M x 16 bit) UtRAM

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND

IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS

OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IN

SAMSUNG PRODUCTS OR TECHNOLOGY.

ALL INFORMATION IN THIS DOCUMENT IS PROVIDED ON AS "AS IS" BASIS WITHOUT GUAR-

ANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar

applications where Product failure could result in loss of life or personal or physical harm, or any military or defense

application, or any governmental procurement to which special terms or provisions may apply.

* Samsung Electronics reserves the right to change products or specification without notice.

- 1 - Revision 0.3

January 2006

1 page

K1B5616BA(B)M

Preliminary

UtRAM

www.DataSheet4U.com

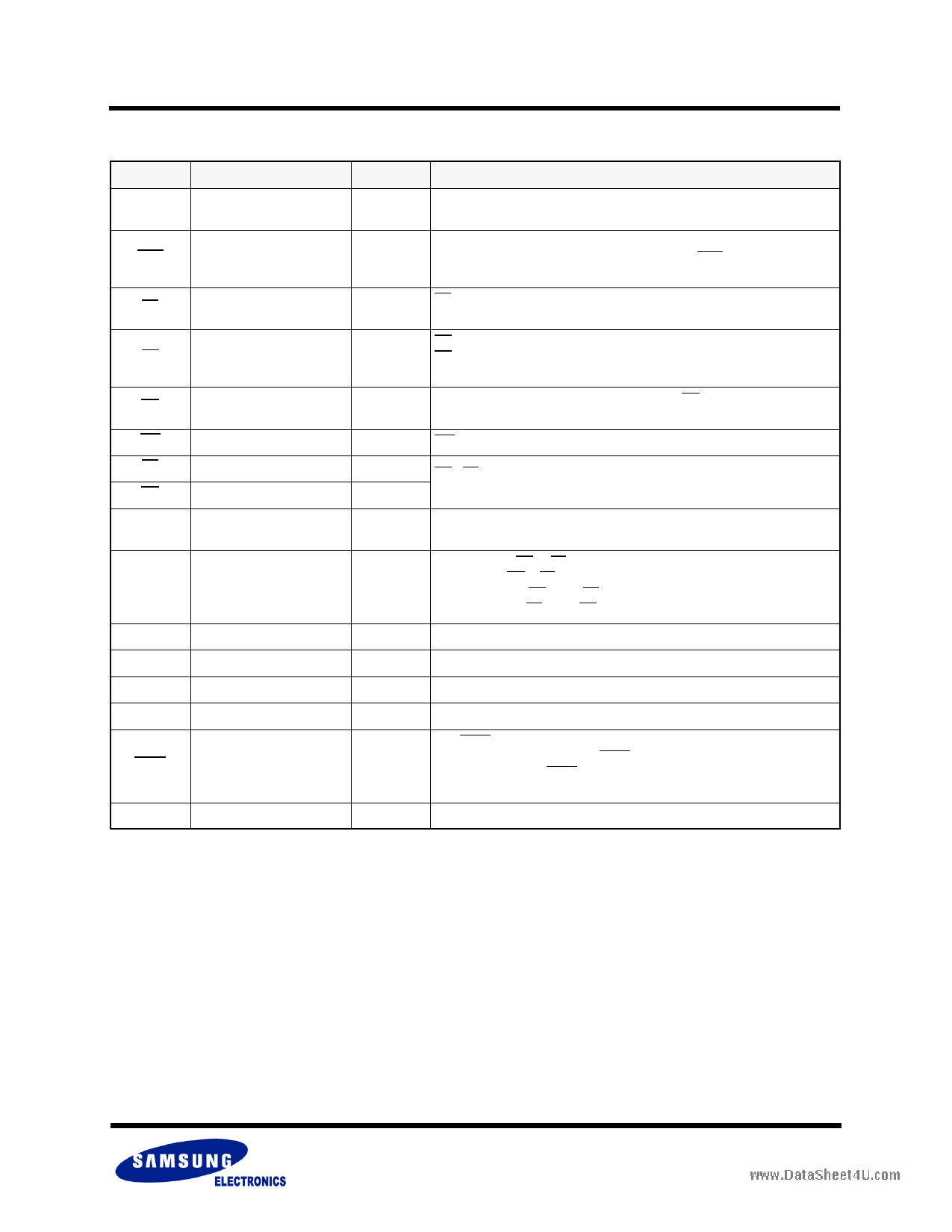

TERMINOLOGY DESCRIPTION

Name

Function

Type

Description

CLK

Clock

Input

Synchronizes the memory to the system operating frequency during syn-

chronous operations. Commands are referenced to CLK.

ADV

Address Valid

Input

Indicates that a valid address is present on the address inputs.

Addresses can be latched on the rising edge of ADV during asynchro-

nous READ and WRITE operations.

PS

Mode Register set

Input

PS low enables Mode Register to be set and enables either PAR or DPD

to be set.

CS low enables the chip to be active

CS

Chip Select

Input CS high disables the chip and puts it into standby mode or deep power

down mode.

OE

Output Enable

Input

Enables the output buffers when LOW. when OE is HIGH, the output buff-

ers are disabled.

WE

Write Enable

Input WE low enables the chip to start writing the data

LB

Lower Byte (I/O0~7)

Input

UB ( LB) low enables upper byte (lower byte) to allow data Input/output

UB

Upper Byte (I/O8~15)

Input

from I/O buffers.

A0~A23

Address 0 ~ Address 23

Input

Inputs for addresses during READ and WRITE operations. Addresses

are internally latched during READ and WRITE cycles.

I/O0~I/O15

Data Inputs / Outputs

Depending on UB or LB status,

Input/Output

word(16-bit, UB & LB low) data,

upper byte(8-bit, UB low & LB high) data or

lower byte(8-bit, LB low & UB high) data is loaded

VCC

Voltage Source

Power Device Power supply. Power supply for device core operation.

VCCQ

I/O Voltage Source

Power I/O Power supply. Power supply for input/output buffers.

VSS

Ground Source

GND Ground for device core operation

VSSQ

I/O Ground Source

GND Ground for input/output buffers

WAIT

Valid Data Indicator

Output

The WAIT signal is output signal indicating the status of the data on the

bus whether or not it is valid. WAIT is asserted when a burst crosses a

word-line boundary. WAIT is asserted and should be ignored during

asynchronous and page mode operations.

DNU

Do Not Use

-

-

- 2 - Revision 0.3

January 2006

5 Page

K1B5616BA(B)M

Preliminary

UtRAM

www.DataSheet4U.com

PAR (Partial Array Refresh) mode [A3~A1]

User can select half array, a fourth array as active memory array. The active memory array is periodically refreshed(data stored),

whereas the disabled array is not going to be refreshed and so the previously stored data will be invalid. When re-enabling addi-

tional portions of the array, the new portions are available immediately upon writing to the MRS.

PAR mode execution;

1) Mode Register Setting into PAR enable(A3=0)

DPD enabled setting(A4=0) has higher priority to PAR enabled setting(A3=0). A4=1 is necessary to use PAR mode.

2) PAR mode Enter; keep PS signal at VIL for longer than 0.5µs during standby mode (Mode Register: A4=1 & A3=0).

3) PAR mode Exit; The device returns to the standby mode when PS signal goes to VIH during PAR mode.

* Mode register values are not changed after the device has been to PAR mode.

DPD (Deep Power Down) mode [A4]

The deep power down mode disables all the refresh related activities. This mode can be used when the system needs to save

power. The data become invalid when DPD mode is executed.

DPD mode execution ;

1) Mode Register Setting into DPD enable(A4=0)

2) DPD mode Enter; keep PS signal at VIL for more than 0.5µs during standby mode (Mode Register: A4=0).

3) DPD mode Exit; The device returns to initial State when PS signal goes to VIH during DPD mode. Wake up sequence is needed

for the device to do normal operation.

* Mode register values are initialized to default value after the device has been to DPD mode.

Default modes are 4 Page Read and Asynchronous Write / DPD disable / PAR disable.

DPD MODE EXECUTION and EXIT

PAR MODE EXECUTION and EXIT

CS

0ns(min)

PS

Normal Operation

0.5µs (min)

200µs(min)

Deep Power Down Wake Up

Normal Operation

CS

0ns(min)

PS

Normal Operation

0.5µs(min)

PAR Mode

Normal Operation

STANDBY MODE CHARACTERISTICS

Power Mode

Address

(Bottom Array)2)

Address

(Top Array)2)

Memory Standby3) Standby3)

Cell Data (ISB1, <40°C) (ISB1, <85°C)

Standby(Full Array)

000000h ~ FFFFFFh

000000h ~ FFFFFFh

Valid1)

TBD

TBD

Partial Refresh(1/2 Block)

000000h ~ 7FFFFFh

800000h ~ FFFFFFh

Valid1)

TBD

TBD

Partial Refresh(1/4 Block)

000000h ~ 3FFFFFh

C00000h ~ FFFFFFh

Valid1)

TBD

TBD

Deep Power Down

000000h ~ FFFFFFh

Invalid

1. Only the data in the selected block are valid

2. PAR Array can be selected through Mode Register Set

3. Standby mode is supposed to be set up after at least one active operation after power up.

ISB1 is measured after 60ms from the time when standby mode is set up.

TBD

TBD

Wait

Time(µs)

0

0

0

200

- 8 - Revision 0.3

January 2006

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet K1B5616BBM.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K1B5616BBM | 256Mb (16M x 16 bit) UtRAM | Samsung Electronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |