|

|

PDF PCK946 Data sheet ( Hoja de datos )

| Número de pieza | PCK946 | |

| Descripción | Low voltage 1 : 10 CMOS clock driver | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PCK946 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

PCK946

Low voltage 1 : 10 CMOS clock driver

Rev. 01 — 13 December 2005

www.DataSheet4U.com

Product data sheet

1. General description

The PCK946 is a low voltage CMOS 1 : 10 clock buffer. The 10 outputs can be configured

into a standard fan-out buffer or into 1× and 1⁄2× combinations. The ten outputs were

designed and optimized to drive 50 Ω series or parallel terminated transmission lines.

With output-to-output skews of 350 ps, the PCK946 is ideal as a clock distribution chip for

synchronous systems which need a tight level of skew from a large number of outputs.

With an output impedance of approximately 7 Ω, in both the HIGH and LOW logic states,

the output buffers of the PCK946 are ideal for driving series terminated transmission lines.

More specifically, each of the 10 PCK946 outputs can drive two series terminated

transmission lines. With this capability, the PCK946 has an effective fan-out of 1 : 20 in

applications using point-to-point distribution schemes.

The PCK946 has the capability of generating 1× and 1⁄2× signals from a 1× source. The

design is fully static; the signals are generated and re-timed inside the chip to ensure

minimal skew between the 1× and 1⁄2× signals. The device features selectability to allow

the user to select the ratio of 1× outputs to 1⁄2× outputs.

Two independent LVCMOS/LVTTL compatible clock inputs are available. Designers can

take advantage of this feature to provide redundant clock sources or the addition of a test

clock into the system design. With the TCLK_SEL input pulled HIGH, the TCLK1 input is

selected.

All of the control inputs are LVCMOS/LVTTL compatible. The DSELn pins choose

between 1× and 1⁄2× outputs. A LOW on the DSELn pins will select the 1× output. The

MR/OE input will reset the internal flip-flops and 3-state the outputs when it is forced

HIGH.

The PCK946 is fully 3.3 V compatible. The 32-lead LQFP package was chosen to

optimize performance, board space, and cost of the device. The 32-lead LQFP package

has a 7 mm × 7 mm body size with a conservative 0.8 mm pin spacing.

2. Features

s 2 selectable LVCMOS/LVTTL clock inputs

s 350 ps output-to-output skew

s Drives up to 20 series terminated independent clock lines

s Maximum input/output frequency of 150 MHz

s 3-stateable outputs

s 32-lead LQFP packaging

s 3.3 V VCC supply voltage

1 page

Philips Semiconductors

PCK946

www.DataSheet4U.com

Low voltage 1 : 10 CMOS clock driver

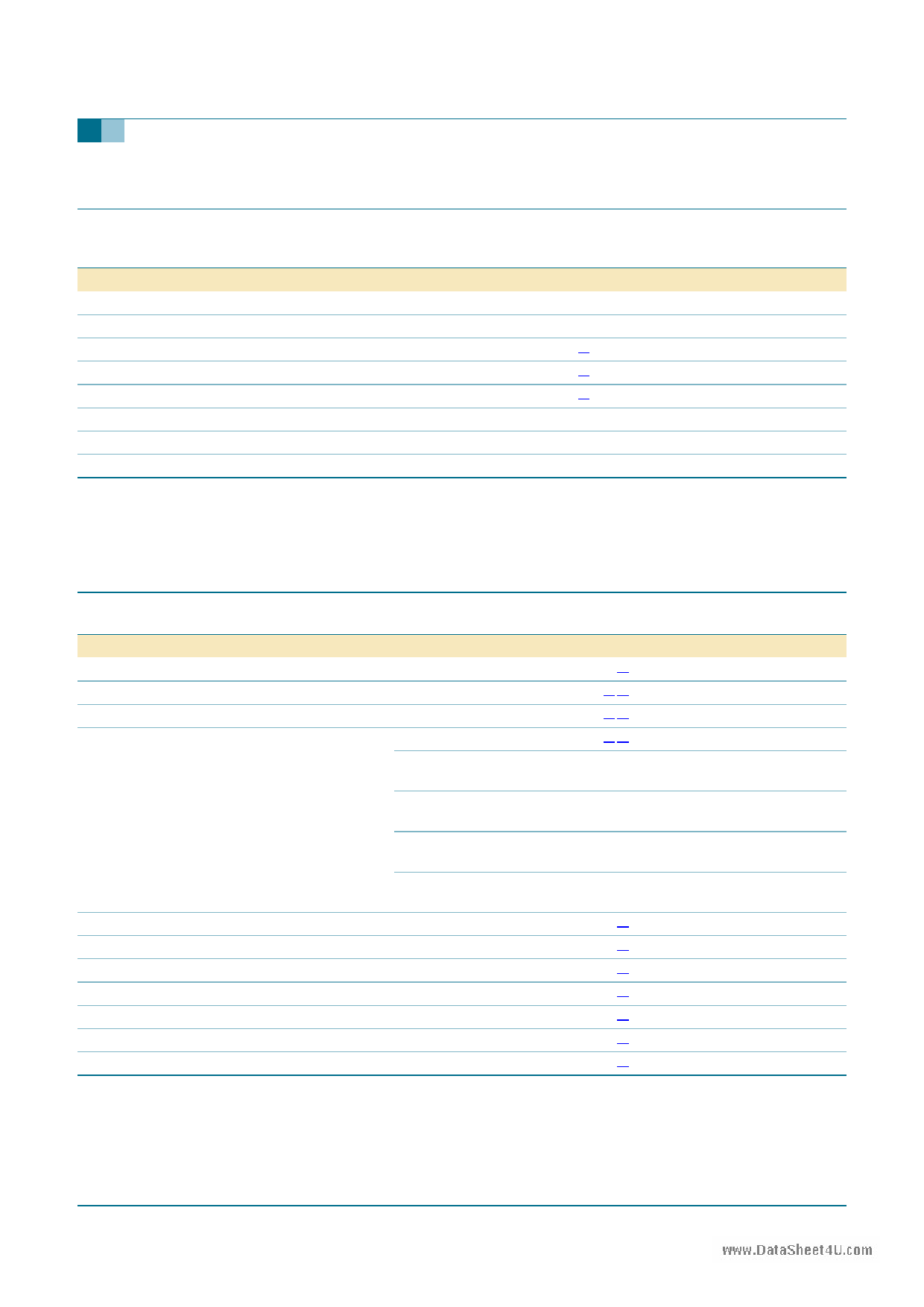

8. Static characteristics

Table 7: Static characteristics

Tamb = 0 °C to +70 °C; VCC = 3.3 V ± 0.3 V

Symbol Parameter

VIH

VIL

VOH

VOL

II

Ci

CPD

Iq(max)

HIGH-state input voltage

LOW-state input voltage

HIGH-state output voltage

LOW-state output voltage

input current

input capacitance

power dissipation capacitance

maximum quiescent supply current

Conditions

IOH = −20 mA

IOL = 20 mA

per output

Min Typ Max Unit

2.0 -

3.6 V

- - 0.8 V

[1] 2.5

-

-

V

[1] - - 0.4 V

[2] -

-

±120

µA

- - 4 pF

- 25 - pF

- 1 2 mA

[1] The PCK946 can drive 50 Ω transmission lines on the incident edge. Each output can drive one 50 Ω parallel terminated transmission

line to the termination voltage of VT = 0.5VCC. Alternately, the device drives up to two 50 Ω series terminated transmission lines.

[2] II current is a result of internal pull-up/pull-down resistors.

9. Dynamic characteristics

Table 8: Dynamic characteristics

Symbol Parameter

Conditions

Min Typ Max Unit

fmax

tPLH

tPHL

tsk(o)

maximum input clock frequency

LOW-to-HIGH propagation delay

HIGH-to-LOW propagation delay

output skew time

TCLK to Qn

TCLK to Qn

output-to-output

fmax < 100 MHz;

same frequency outputs

[1] 150

[1] [2] 4.5

[1] [2] 4.5

[1] [2]

-

-

7.5

7.5

-

- MHz

11.5 ns

11.5 ns

350 ps

fmax < 100 MHz;

different frequency outputs

- - 350 ps

fmax > 100 MHz;

same frequency outputs

- - 350 ps

fmax > 100 MHz;

different frequency outputs

- - 450 ps

tsk(pr)

tPZL

tPZH

tPLZ

tPHZ

tr

tf

process skew time

part-to-part

OFF-state to LOW propagation delay

OFF-state to HIGH propagation delay

LOW to OFF-state propagation delay

HIGH to OFF-state propagation delay

rise time

output; 0.8 V to 2.0 V

fall time

output; 2.0 V to 0.8 V

[3] - 2.0 4.5 ns

[2] -

3 11 ns

[2] -

3 11 ns

[2] -

3 11 ns

[2] -

3 11 ns

[2] 0.1 0.5 1.0 ns

[2] 0.1 0.5 1.0 ns

[1] Driving 50 Ω transmission lines.

[2] Termination is 50 Ω to 0.5VCC.

[3] Part-to-part skew at a given temperature and voltage.

9397 750 12296

Product data sheet

Rev. 01 — 13 December 2005

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

5 of 13

5 Page

Philips Semiconductors

PCK946

www.DataSheet4U.com

Low voltage 1 : 10 CMOS clock driver

[4] These packages are not suitable for wave soldering. On versions with the heatsink on the bottom side, the

solder cannot penetrate between the printed-circuit board and the heatsink. On versions with the heatsink

on the top side, the solder might be deposited on the heatsink surface.

[5] If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave

direction. The package footprint must incorporate solder thieves downstream and at the side corners.

[6] Wave soldering is suitable for LQFP, QFP and TQFP packages with a pitch (e) larger than 0.8 mm; it is

definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65 mm.

[7] Wave soldering is suitable for SSOP, TSSOP, VSO and VSSOP packages with a pitch (e) equal to or larger

than 0.65 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

[8] Image sensor packages in principle should not be soldered. They are mounted in sockets or delivered

pre-mounted on flex foil. However, the image sensor package can be mounted by the client on a flex foil by

using a hot bar soldering process. The appropriate soldering profile can be provided on request.

[9] Hot bar soldering or manual soldering is suitable for PMFP packages.

13. Abbreviations

Table 10: Abbreviations

Acronym

Description

CMOS

Complementary Metal Oxide Silicon

LVCMOS

Low Voltage Complementary Metal Oxide Silicon

LVTTL

Low Voltage Transistor-Transistor Logic

14. Revision history

Table 11: Revision history

Document ID

Release date Data sheet status

PCK946_1

20051213

Product data sheet

Change notice Doc. number Supersedes

- 9397 750 12296 -

9397 750 12296

Product data sheet

Rev. 01 — 13 December 2005

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

11 of 13

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet PCK946.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PCK940L | Low voltage 1 : 18 clock distribution chip | NXP Semiconductors |

| PCK942C | Low voltage 1 : 18 clock distribution chip | NXP Semiconductors |

| PCK9446 | LVCMOS clock fan-out buffer | NXP Semiconductors |

| PCK9447 | LVCMOS clock fan-out buffer | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |