|

|

PDF ICS874005 Data sheet ( Hoja de datos )

| Número de pieza | ICS874005 | |

| Descripción | PCI EXPRESS JITTER ATTENUATOR | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS874005 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

ICS874005www.DataSheet4U.com

PCI EXPRESS™

JITTER ATTENUATOR

GENERAL DESCRIPTION

The ICS874005 is a high performance Diff-

ICS erential-to-LVDS Jitter Attenuator designed for

HiPerClockS™ use in PCI Express systems. In some PCI

Express systems, such as those found in

desktop PCs, the PCI Express clocks are

generated from a low bandwidth, high phase noise PLL

frequency synthesizer. In these systems, a jitter attenuator

may be required to attenuate high frequency random and

deterministic jitter components from the PLL synthesizer

and from the system board. The ICS874005 has 3 PLL

bandwidth modes: 200kHz, 400kHz, and 800kHz. The

200kHz mode will provide maximum jitter attenuation, but

with higher PLL tracking skew and spread spectrum

modulation from the motherboard synthesizer may be

attenuated. The 400kHz provides an intermediate bandwidth

that can easily track triangular spread profiles, while

providing good jitter attenuation. The 800kHz bandwidth

provides the best tracking skew and will pass most spread

profiles, but the jitter attenuation will not be as good as the

lower bandwidth modes. Because some 2.5Gb serdes have

x20 multipliers while others have than x25 multipliers, the

874005 can be set for 1:1 mode or 5/4 multiplication mode

(i.e. 100MHz input/125MHz output) using the F_SEL pins.

FEATURES

• Five differential LVDS output pairs

• One differential clock input

• CLK and nCLK supports the following input types:

LVPECL, LVDS, LVHSTL, SSTL, HCSL

• Output frequency range: 98MHz - 160MHz

• Input frequency range: 98MHz - 128MHz

• VCO range: 490MHz - 640MHz

• Cycle-to-cycle jitter: 30ps (maximum)

• 3.3V operating supply

• 3 bandwidth modes allow the system designer to make

jitter attenuation/tracking skew design trade-offs

• 0°C to 70°C ambient operating temperature

• Available in both standard and lead-free RoHS compliant

packages

PLL BANDWIDTH

The ICS874005 uses ICS 3rd Generation FemtoClockTM

PLL technology to achive the lowest possible phase noise.

The device is packaged in a 24 Lead TSSOP package,

making it ideal for use in space constrained applications

such as PCI Express add-in cards.

BW_SEL

0 = PLL Bandwidth: ~200kHz

Float = PLL Bandwidth: ~400kHz (Default)

1 = PLL Bandwidth: ~800kHz

BLOCK DIAGRAM

OEA Pulldown

F_SELA Pulldown

BW_SEL Float

0 = ~200kHz

Float = ~400kHz

1 = ~800kHz

CLK Pulldown

nCLK Pullup

Phase

Detector

VCO

490 - 640MHz

M = ÷5 (fixed)

F_SELA

0 ÷5 (default)

1 ÷4

F_SELB

0 ÷5 (default)

1 ÷4

QA0

nQA0

QA1

nQA1

QB0

nQB0

QB1

nQB1

QB2

F_SELB Pulldown

MR Pulldown

OEB Pullup

874005AG

nQB2

www.icst.com/products/hiperclocks.html

1

PIN ASSIGNMENT

nQB2

nQA1

QA1

VDDO

QA0

nQA0

MR

BW_SEL

VDDA

F_SELA

VDD

OEA

1

2

3

4

5

6

7

8

9

10

11

12

24 QB2

2 3 VDDO

22 QB1

21 nQB1

20 QB0

19 nQB0

18 F_SELB

17 OEB

16 GND

15 GND

14 nCLK

13 CLK

ICS874005

24-Lead TSSOP

4.40mm x 7.8mm x 0.92mm

package body

G Package

Top View

REV. A JANUARY 25, 2006

1 page

Integrated

Circuit

Systems, Inc.

ICS874005www.DataSheet4U.com

PCI EXPRESS™

JITTER ATTENUATOR

PARAMETER MEASUREMENT INFORMATION

VDD,

VDDO VDDA

VDD

3.3V±5%

POWER SUPPLY

+ Float GND–

LVDS

Qx SCOPE

nQx

nCLK

CLK

V

PP

GND

Cross Points

3.3V LVDS OUTPUT LOAD AC TEST CIRCUIT

DIFFERENTIAL INPUT LEVEL

nQA0, nQA1

nQB0:nQB2

QA0, QA1

QB0:QB2

tcycle n

➤

tcycle n+1

t jit(cc) = tcycle n –tcycle n+1

1000 Cycles

➤

nQx

Qx

nQy

Qy

t sk(o)

V

CMR

CYCLE-TO-CYCLE JITTER

Clock

20%

Outputs

80%

tR

80%

tF

OUTPUT SKEW

VSW I N G

20%

nQA0, nQA1

nQB0:nQB2

QA0, QA1

QB0:QB2

t PW

t

PERIOD

odc = t PW x 100%

t PERIOD

OUTPUT RISE/FALL TIME

VDD

DC Input LVDS

out

➤

100 VOD/Δ VOD

out

OUTPUT DUTY CYCLE/PULSE WIDTH/PERIOD

VDD

out

DC Input LVDS

out

➤

VOS/Δ VOS

DIFFERENTIAL OUTPUT VOLTAGE SETUP

874005AG

OFFSET VOLTAGE SETUP

www.icst.com/products/hiperclocks.html

5

REV. A JANUARY 25, 2006

5 Page

Integrated

Circuit

Systems, Inc.

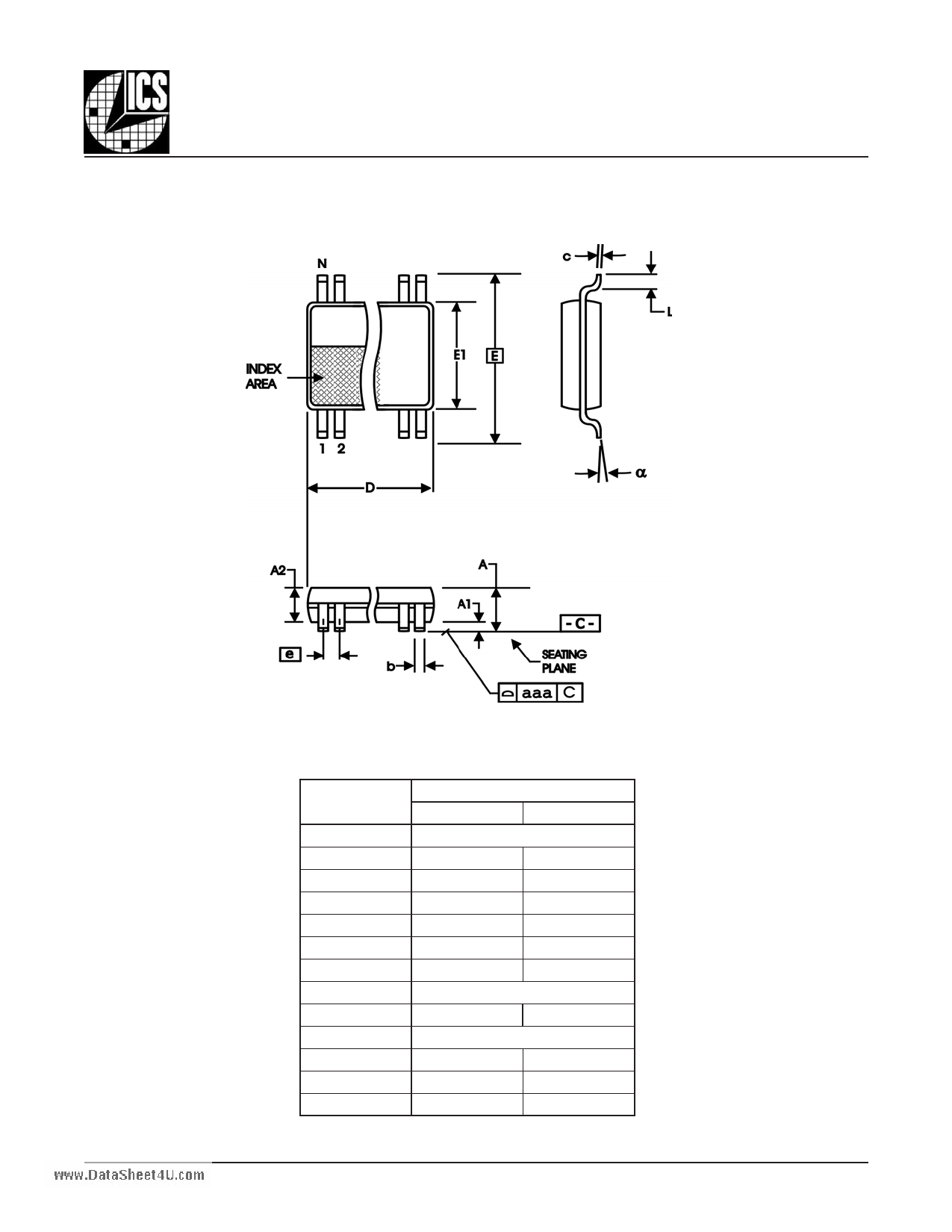

PACKAGE OUTLINE - G SUFFIX FOR 24 LEAD TSSOP

ICS874005www.DataSheet4U.com

PCI EXPRESS™

JITTER ATTENUATOR

874005AG

TABLE 8. PACKAGE DIMENSIONS

SYMBOL

Millimeters

Minimum

Maximum

N 24

A -- 1.20

A1 0.05 0.15

A2 0.80 1.05

b 0.19 0.30

c 0.09 0.20

D 7.70 7.90

E 6.40 BASIC

E1 4.30 4.50

e 0.65 BASIC

L 0.45 0.75

α 0° 8°

aaa -- 0.10

Reference Document: JEDEC Publication 95, MO-153

www.icst.com/products/hiperclocks.html

11

REV. A JANUARY 25, 2006

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet ICS874005.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS874001I-05 | PCI EXPRESS JITTER ATTENUATOR | Integrated Device Technology |

| ICS874002 | PCI EXPRESS JITTER ATTENUATOR | Integrated Circuit Systems |

| ICS874003 | PCI EXPRESS JITTER ATTENUATOR | Integrated Circuit Systems |

| ICS874003-02 | PCI EXPRESS JITTER ATTENUATOR | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |