|

|

PDF XCV800 Data sheet ( Hoja de datos )

| Número de pieza | XCV800 | |

| Descripción | Virtex Field Programmable Gate Array | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XCV800 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

0

Virtex™ 2.5 VR www.DataSheet4U.com

Field Programmable Gate Arrays

DS003-1 (v2.5 ) April 2, 2001

0 0 Product Specification

Features

• Fast, high-density Field-Programmable Gate Arrays

- Densities from 50k to 1M system gates

- System performance up to 200 MHz

- 66-MHz PCI Compliant

- Hot-swappable for Compact PCI

• Multi-standard SelectIO™ interfaces

- 16 high-performance interface standards

- Connects directly to ZBTRAM devices

• Built-in clock-management circuitry

- Four dedicated delay-locked loops (DLLs) for

advanced clock control

- Four primary low-skew global clock distribution

nets, plus 24 secondary local clock nets

• Hierarchical memory system

- LUTs configurable as 16-bit RAM, 32-bit RAM,

16-bit dual-ported RAM, or 16-bit Shift Register

- Configurable synchronous dual-ported 4k-bit

RAMs

- Fast interfaces to external high-performance RAMs

• Flexible architecture that balances speed and density

- Dedicated carry logic for high-speed arithmetic

- Dedicated multiplier support

- Cascade chain for wide-input functions

- Abundant registers/latches with clock enable, and

dual synchronous/asynchronous set and reset

- Internal 3-state bussing

- IEEE 1149.1 boundary-scan logic

- Die-temperature sensor diode

• Supported by FPGA Foundation™ and Alliance

Development Systems

- Complete support for Unified Libraries, Relationally

Placed Macros, and Design Manager

- Wide selection of PC and workstation platforms

• SRAM-based in-system configuration

- Unlimited re-programmability

- Four programming modes

• 0.22 µm 5-layer metal process

• 100% factory tested

Description

The Virtex FPGA family delivers high-performance,

high-capacity programmable logic solutions. Dramatic

increases in silicon efficiency result from optimizing the new

architecture for place-and-route efficiency and exploiting an

aggressive 5-layer-metal 0.22 µm CMOS process. These

advances make Virtex FPGAs powerful and flexible alterna-

tives to mask-programmed gate arrays. The Virtex family

comprises the nine members shown in Table 1.

Building on experience gained from previous generations of

FPGAs, the Virtex family represents a revolutionary step

forward in programmable logic design. Combining a wide

variety of programmable system features, a rich hierarchy of

fast, flexible interconnect resources, and advanced process

technology, the Virtex family delivers a high-speed and

high-capacity programmable logic solution that enhances

design flexibility while reducing time-to-market.

Table 1: Virtex Field-Programmable Gate Array Family Members

Device

Maximum

System Gates CLB Array Logic Cells Available I/O

XCV50

57,906

16x24

1,728

180

XCV100

108,904

20x30

2,700

180

XCV150

164,674

24x36

3,888

260

XCV200

236,666

28x42

5,292

284

XCV300

322,970

32x48

6,912

316

XCV400

468,252

40x60

10,800

404

XCV600

661,111

48x72

15,552

512

XCV800

888,439

56x84

21,168

512

XCV1000

1,124,022

64x96

27,648

512

Block RAM

Bits

32,768

40,960

49,152

57,344

65,536

81,920

98,304

114,688

131,072

Maximum

SelectRAM+™ Bits

24,576

38,400

55,296

75,264

98,304

153,600

221,184

301,056

393,216

© 2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

DS003-1 (v2.5 ) April 2, 2001

Product Specification

www.xilinx.com

1-800-255-7778

Module 1 of 4

1

1 page

0

Virtex™ 2.5 VR www.DataSheet4U.com

Field Programmable Gate Arrays

DS003-2 (v2.8.1) December 9, 2002

0 0 Product Specification

Architectural Description

Virtex Array

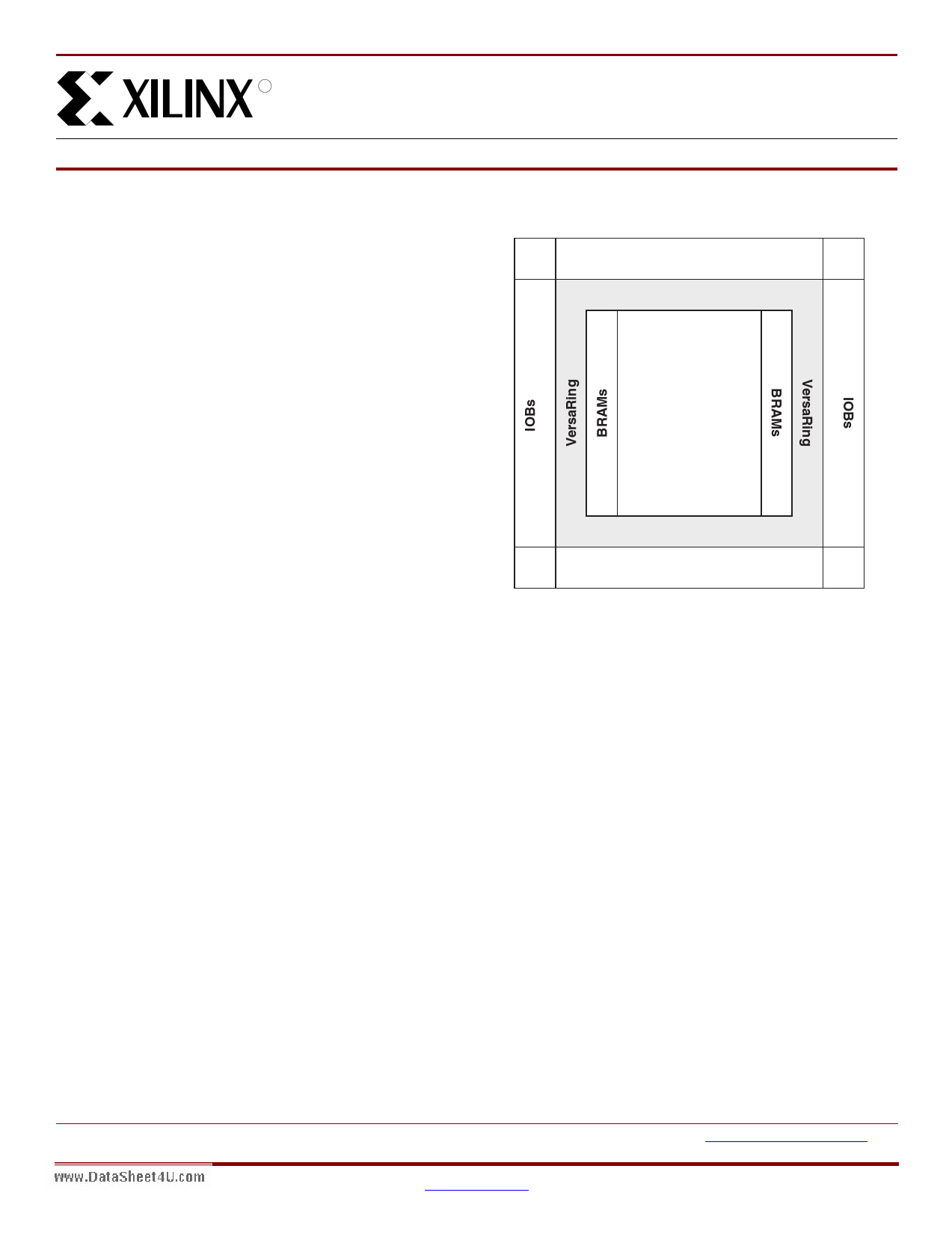

The Virtex user-programmable gate array, shown in

Figure 1, comprises two major configurable elements: con-

figurable logic blocks (CLBs) and input/output blocks

(IOBs).

• CLBs provide the functional elements for constructing

logic

• IOBs provide the interface between the package pins

and the CLBs

CLBs interconnect through a general routing matrix (GRM).

The GRM comprises an array of routing switches located at

the intersections of horizontal and vertical routing channels.

Each CLB nests into a VersaBlock™ that also provides local

routing resources to connect the CLB to the GRM.

The VersaRing™ I/O interface provides additional routing

resources around the periphery of the device. This routing

improves I/O routability and facilitates pin locking.

The Virtex architecture also includes the following circuits

that connect to the GRM.

• Dedicated block memories of 4096 bits each

• Clock DLLs for clock-distribution delay compensation

and clock domain control

• 3-State buffers (BUFTs) associated with each CLB that

drive dedicated segmentable horizontal routing

resources

Values stored in static memory cells control the configurable

logic elements and interconnect resources. These values

load into the memory cells on power-up, and can reload if

necessary to change the function of the device.

Input/Output Block

The Virtex IOB, Figure 2, features SelectIO™ inputs and

outputs that support a wide variety of I/O signalling stan-

dards, see Table 1.

The three IOB storage elements function either as edge-trig-

gered D-type flip-flops or as level sensitive latches. Each

IOB has a clock signal (CLK) shared by the three flip-flops

and independent clock enable signals for each flip-flop.

In addition to the CLK and CE control signals, the three

flip-flops share a Set/Reset (SR). For each flip-flop, this sig-

nal can be independently configured as a synchronous Set,

a synchronous Reset, an asynchronous Preset, or an asyn-

chronous Clear.

The output buffer and all of the IOB control signals have

independent polarity controls.

DLL

IOBs

DLL

VersaRing

CLBs

VersaRing

IOBs

DLL DLL

vao_b.eps

Figure 1: Virtex Architecture Overview

All pads are protected against damage from electrostatic

discharge (ESD) and from over-voltage transients. Two

forms of over-voltage protection are provided, one that per-

mits 5 V compliance, and one that does not. For 5 V compli-

ance, a Zener-like structure connected to ground turns on

when the output rises to approximately 6.5 V. When PCI

3.3 V compliance is required, a conventional clamp diode is

connected to the output supply voltage, VCCO.

Optional pull-up and pull-down resistors and an optional

weak-keeper circuit are attached to each pad. Prior to con-

figuration, all pins not involved in configuration are forced

into their high-impedance state. The pull-down resistors and

the weak-keeper circuits are inactive, but inputs can option-

ally be pulled up.

The activation of pull-up resistors prior to configuration is

controlled on a global basis by the configuration mode pins.

If the pull-up resistors are not activated, all the pins will float.

Consequently, external pull-up or pull-down resistors must

be provided on pins required to be at a well-defined logic

level prior to configuration.

All Virtex IOBs support IEEE 1149.1-compatible boundary

scan testing.

© 1999-2002 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

DS003-2 (v2.8.1) December 9, 2002

Product Specification

www.xilinx.com

1-800-255-7778

Module 2 of 4

1

5 Page

R Virtex™ 2.5 V Field Programmable Gate Arrays

General Purpose Routing

Most Virtex signals are routed on the general purpose rout-

ing, and consequently, the majority of interconnect

resources are associated with this level of the routing hier-

archy. The general routing resources are located in horizon-

tal and vertical routing channels associated with the rows

and columns CLBs. The general-purpose routing resources

are listed below.

• Adjacent to each CLB is a General Routing Matrix

(GRM). The GRM is the switch matrix through which

horizontal and vertical routing resources connect, and

is also the means by which the CLB gains access to

the general purpose routing.

• 24 single-length lines route GRM signals to adjacent

GRMs in each of the four directions.

• 12 buffered Hex lines route GRM signals to another

GRMs six-blocks away in each one of the four

directions. Organized in a staggered pattern, Hex lines

can be driven only at their endpoints. Hex-line signals

can be accessed either at the endpoints or at the

midpoint (three blocks from the source). One third of

the Hex lines are bidirectional, while the remaining

ones are uni-directional.

• 12 Longlines are buffered, bidwirwewct.DioantalShweireet4sUt.hcaotm

distribute signals across the device quickly and

efficiently. Vertical Longlines span the full height of the

device, and horizontal ones span the full width of the

device.

I/O Routing

Virtex devices have additional routing resources around

their periphery that form an interface between the CLB array

and the IOBs. This additional routing, called the VersaRing,

facilitates pin-swapping and pin-locking, such that logic

redesigns can adapt to existing PCB layouts. Time-to-mar-

ket is reduced, since PCBs and other system components

can be manufactured while the logic design is still in

progress.

Dedicated Routing

Some classes of signal require dedicated routing resources

to maximize performance. In the Virtex architecture, dedi-

cated routing resources are provided for two classes of sig-

nal.

• Horizontal routing resources are provided for on-chip

3-state busses. Four partitionable bus lines are

provided per CLB row, permitting multiple busses

within a row, as shown in Figure 8.

• Two dedicated nets per CLB propagate carry signals

vertically to the adjacent CLB.

Tri-State

Lines

CLB

CLB

CLB

CLB

buft_c.eps

Figure 8: BUFT Connections to Dedicated Horizontal Bus Lines

Global Routing

Global Routing resources distribute clocks and other sig-

nals with very high fanout throughout the device. Virtex

devices include two tiers of global routing resources

referred to as primary global and secondary local clock rout-

ing resources.

• The primary global routing resources are four

dedicated global nets with dedicated input pins that are

designed to distribute high-fanout clock signals with

minimal skew. Each global clock net can drive all CLB,

IOB, and block RAM clock pins. The primary global

nets can only be driven by global buffers. There are

four global buffers, one for each global net.

• The secondary local clock routing resources consist of

24 backbone lines, 12 across the top of the chip and 12

across bottom. From these lines, up to 12 unique

signals per column can be distributed via the 12

longlines in the column. These secondary resources

are more flexible than the primary resources since they

are not restricted to routing only to clock pins.

Clock Distribution

Virtex provides high-speed, low-skew clock distribution

through the primary global routing resources described

above. A typical clock distribution net is shown in Figure 9.

Four global buffers are provided, two at the top center of the

device and two at the bottom center. These drive the four

primary global nets that in turn drive any clock pin.

DS003-2 (v2.8.1) December 9, 2002

Product Specification

www.xilinx.com

1-800-255-7778

Module 2 of 4

7

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet XCV800.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XCV800 | Virtex Field Programmable Gate Array | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |