|

|

PDF FM8PS53 Data sheet ( Hoja de datos )

| Número de pieza | FM8PS53 | |

| Descripción | EPROM/ROM-Based 8-Bit Microcontroller Series | |

| Fabricantes | FEELING TECHNOLOGY | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de FM8PS53 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

FEELING

TECHNOLOGY

www.DataSheet4U.com

FM8PS53

EPROM/ROM-Based 8-Bit Microcontroller Series

Devices Included in this Data Sheet:

‧ FM8PS53E : EPROM device

‧ FM8PS53 : Mask ROM device

FEATURES

‧ Only 42 single word instructions

‧ All instructions are single cycle except for program branches which are two-cycle

‧ 13-bit wide instructions

‧ All ROM/EPROM area GOTO instruction

‧ All ROM/EPROM area subroutine CALL instruction

‧ 8-bit wide data path

‧ 5-level deep hardware stack

‧ Operating speed: DC-20 MHz clock input

DC-100 ns instruction cycle

Device

Pins # I/O # EPROM/ROM (Byte) RAM (Byte)

FM8PS53/53E 14 12

1K

49

‧ Direct, indirect addressing modes for data accessing

‧ 8-bit real time clock/counter (Timer0) with 8-bit programmable prescaler

‧ Internal Power-on Reset (POR)

‧ Built-in Low Voltage Detector (LVD) for Brown-out Reset (BOR)

‧ Power-up Reset Timer (PWRT) and Oscillator Start-up Timer(OST)

‧ On chip Watchdog Timer (WDT) with internal oscillator for reliable operation and soft-ware watch-dog

enable/disable control

‧ Two I/O ports IOA and IOB with independent direction control

‧ Soft-ware I/O pull-high/pull-down or open-drain control

‧ One internal interrupt source: Timer0 overflow; Two external interrupt source: INT pin, Port B input change

‧ Wake-up from SLEEP by INT pin or Port B input change

‧ Power saving SLEEP mode

‧ Built-in 8MHz, 4MHz, 1MHz, and 455KHz internal RC oscillator

‧ Programmable Code Protection

‧ Built-in internal RC oscillator

‧ Selectable oscillator options:

- ERC: External Resistor/Capacitor Oscillator

- HF: High Frequency Crystal/Resonator Oscillator

- XT: Crystal/Resonator Oscillator

- LF: Low Frequency Crystal Oscillator

- IRC: Internal Resistor/Capacitor Oscillator

- ERIC: External Resistor/Internal Capacitor Oscillator

‧ Wide-operating voltage range:

- EPROM : 2.3V to 5.5V

- ROM : 2.3V to 5.5V

This datasheet contains new product information. Feeling Technology reserves the rights to modify the product specification without notice.

No liability is assumed as a result of the use of this product. No rights under any patent accompany the sales of the product.

Rev1.00 Mar 28, 2006

P.1/FM8PS53

1 page

FEELING

TECHNOLOGY

www.DataSheet4U.com

FM8PS53

1.2 Data Memory Organization

Data memory is composed of Special Function Registers and General Purpose Registers.

The General Purpose Registers are accessed either directly or indirectly through the FSR register.

The Special Function Registers are registers used by the CPU and peripheral functions to control the

operation of the device.

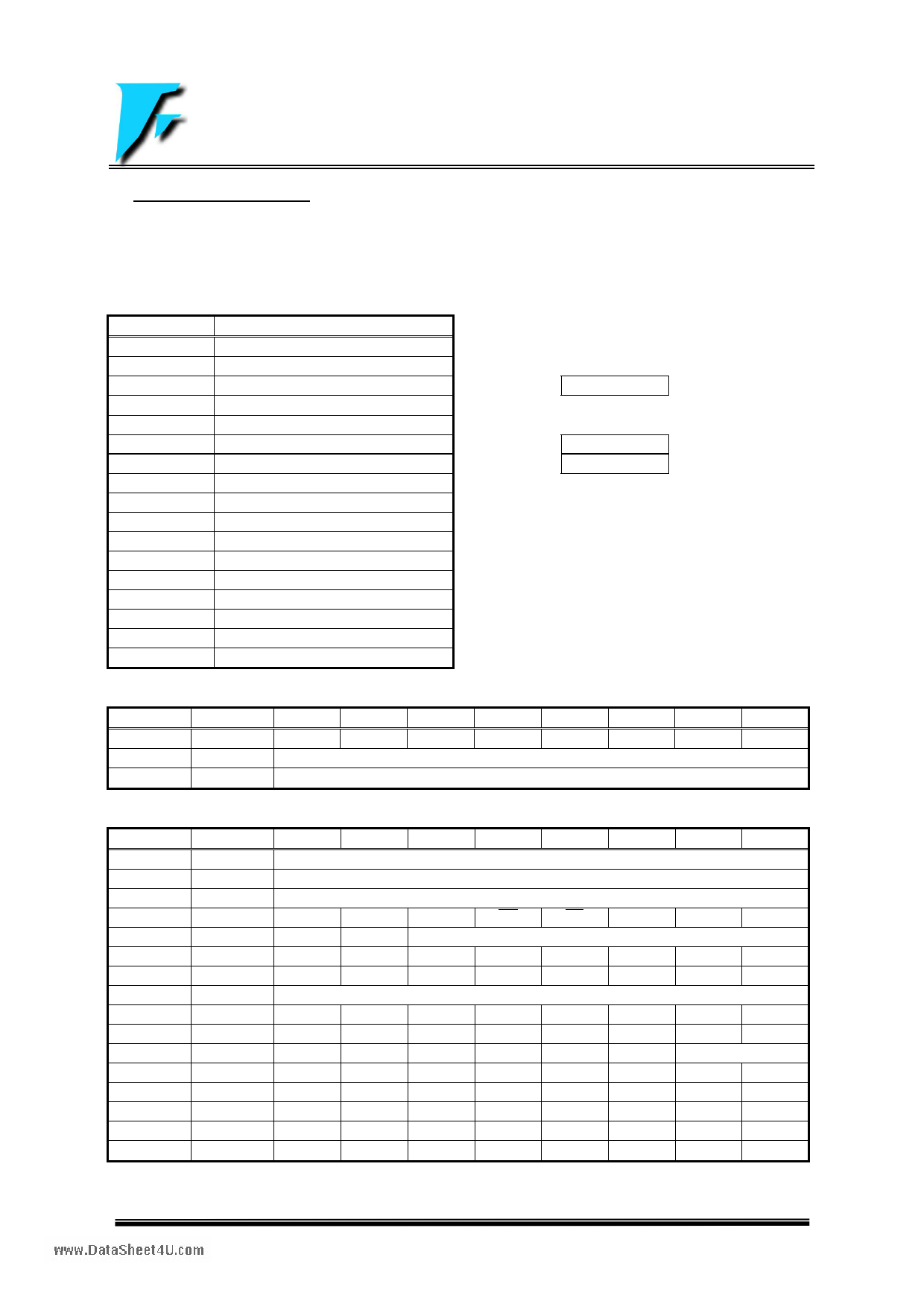

TABLE 1.1: Registers File Map for FM8PS53 Series

Address

Description

00h INDF

01h TMR0

02h PCL

03h STATUS

04h FSR

05h PORTA

06h PORTB

07h General Purpose Register

08h PCON

09h WUCON

0Ah PCHBUF

0Bh PDCON

0Ch ODCON

0Dh PHCON

0Eh INTEN

0Fh INTFLAG

10h ~ 3Fh

General Purpose Registers

N/A OPTION

05h IOSTA

06h IOSTB

TABLE 1.2: The Registers Controlled by OPTION or IOST Instructions

Address

Name

B7

B6

B5

B4

B3

B2

B1

B0

N/A (w) OPTION

* INTEDG T0CS T0SE PSA PS2 PS1 PS0

05h (w)

IOSTA

Port A I/O Control Register

06h (w)

IOSTB

Port B I/O Control Register

TABLE 1.3: Operational Registers Map

Address

Name

B7

B6

B5

B4

B3

B2

B1

B0

00h (r/w)

INDF

Uses contents of FSR to address data memory (not a physical register)

01h (r/w)

TMR0

8-bit real-time clock/counter

02h (r/w)

PCL

Low order 8 bits of PC

03h (r/w) STATUS

RST

GP1

GP0

TO

PD

Z

DC

C

04h (r/w)

FSR

*

*

Indirect data memory address pointer

05h (r/w) PORTA

IOA3

IOA2

IOA1

IOA0

06h (r/w) PORTB

IOB7

IOB6

IOB5

IOB4

IOB3

IOB2

IOB1

IOB0

07h (r/w)

SRAM

General Purpose Register

08h (r/w) PCON WDTE EIS LVDTE

*

*

*

*

*

09h (r/w) WUCON WUB7 WUB6 WUB5 WUB4 WUB3 WUB2 WUB1 WUB0

0Ah (r/w) PCHBUF

-

-

-

-

-

- 2 MSBs Buffer of PC

0Bh (r/w) PDCON

/PDB2 /PDB1 /PDB0 /PDA3 /PDA2 /PDA1 /PDA0

0Ch (r/w) ODCON ODB7 ODB6 ODB5 ODB4

ODB2 ODB1 ODB0

0Dh (r/w) PHCON /PHB7 /PHB6 /PHB5 /PHB4

/PHB2 /PHB1 /PHB0

0Eh (r/w) INTEN

GIE

*

*

*

*

INTIE PBIE

T0IE

0Fh (r/w) INTFLAG

-

-

-

-

-

INTIF PBIF

T0IF

Legend: - = unimplemented, read as ‘0’, * = unimplemented, read as ‘1’,

Rev1.00 Mar 28, 2006

P.5/FM8PS53

5 Page

FEELING

TECHNOLOGY

www.DataSheet4U.com

FM8PS53

WUB2 : = 0, Disable the input change interrupt/wake-up function of IOB2 pin.

= 1, Enable the input change interrupt/wake-up function of IOB2 pin.

WUB3 : = 0, Disable the input change interrupt/wake-up function of IOB3 pin.

= 1, Enable the input change interrupt/wake-up function of IOB3 pin.

WUB4 : = 0, Disable the input change interrupt/wake-up function of IOB4 pin.

= 1, Enable the input change interrupt/wake-up function of IOB4 pin.

WUB5 : = 0, Disable the input change interrupt/wake-up function of IOB5 pin.

= 1, Enable the input change interrupt/wake-up function of IOB5 pin.

WUB6 : = 0, Disable the input change interrupt/wake-up function of IOB6 pin.

= 1, Enable the input change interrupt/wake-up function of IOB6 pin.

WUB7 : = 0, Disable Enable the input change interrupt/wake-up function of IOB7 pin.

= 1, Enable the input change interrupt/wake-up function of IOB7 pin.

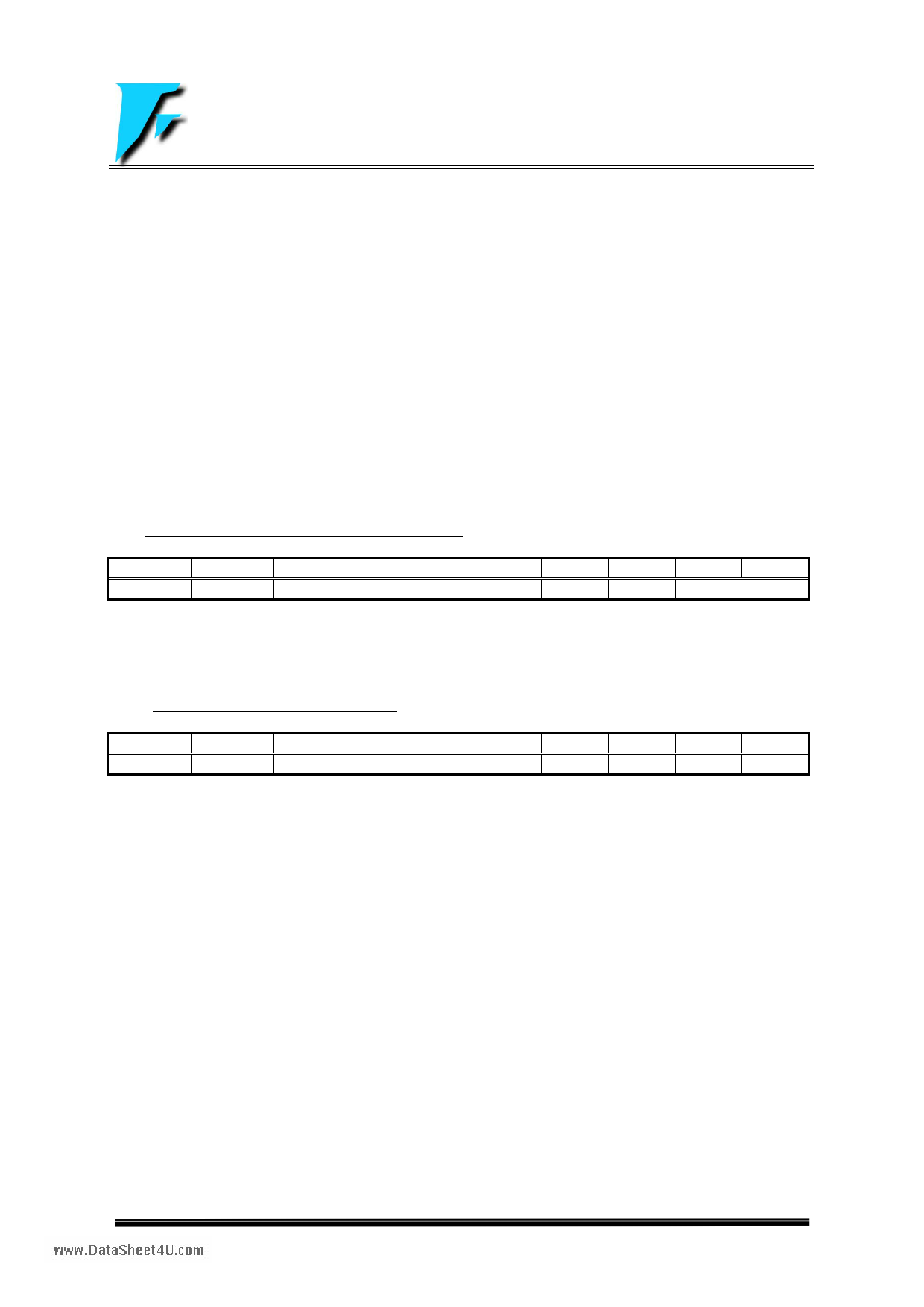

2.1.9 PCHBUF (High Byte Buffer of Program Counter)

Address

Name

B7

B6

B5

B4

B3

B2

B1

B0

0Ah (r/w) PCHBUF

-

-

-

-

-

- 2 MSBs Buffer of PC

Bit1:Bit0 : See 2.1.3 for detail description.

Bit7:Bit2 : Not used. Read as “0”s.

2.1.10 PDCON (Pull-down Control Register)

Address

0Bh (r/w)

Name

PDCON

B7 B6 B5 B4 B3 B2 B1 B0

/PDB2 /PDB1 /PDB0 /PDA3 /PDA2 /PDA1 /PDA0

/PDA0 : = 0, Enable the internal pull-down of IOA0 pin.

= 1, Disable the internal pull-down of IOA0 pin.

/PDA1 : = 0, Enable the internal pull-down of IOA1 pin.

= 1, Disable the internal pull-down of IOA1 pin.

/PDA2 : = 0, Enable the internal pull-down of IOA2 pin.

= 1, Disable the internal pull-down of IOA2 pin.

/PDA3 : = 0, Enable the internal pull-down of IOA3 pin.

= 1, Disable the internal pull-down of IOA3 pin.

/PDB0 : = 0, Enable the internal pull-down of IOB0 pin.

= 1, Disable the internal pull-down of IOB0 pin.

/PDB1 : = 0, Enable the internal pull-down of IOB1 pin.

= 1, Disable the internal pull-down of IOB1 pin.

/PDB2 : = 0, Enable the internal pull-down of IOB2 pin.

= 1, Disable the internal pull-down of IOB2 pin.

Bit7 : General purpose read/write bit.

Rev1.00 Mar 28, 2006

P.11/FM8PS53

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet FM8PS53.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FM8PS53 | EPROM/ROM-Based 8-Bit Microcontroller Series | FEELING TECHNOLOGY |

| FM8PS54 | (FM8PS54 / FM8PS56) EPROM/ROM-Based 8-Bit Microcontroller Series | FEELING TECHNOLOGY |

| FM8PS56 | (FM8PS54 / FM8PS56) EPROM/ROM-Based 8-Bit Microcontroller Series | FEELING TECHNOLOGY |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |