|

|

PDF MAX1219 Data sheet ( Hoja de datos )

| Número de pieza | MAX1219 | |

| Descripción | Broadband Applications | |

| Fabricantes | Maxim Integrated Products | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX1219 (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

19-3761; Rev 0; 8/05

EVAALVUAAILTAIOBNLEKIT

www.DataSheet4U.com

1.8V, Dual, 12-Bit, 210Msps ADC for

Broadband Applications

General Description

The MAX1219 dual, monolithic, 12-bit, 210Msps analog-

to-digital converter (ADC) provides outstanding dynam-

ic performance up to a 250MHz input frequency. The

device operates with conversion rates up to 210Msps

while consuming only 800mW per channel.

At 210Msps and an input frequency of 200MHz, the

MAX1219 achieves a 79dBc spurious-free dynamic

range (SFDR) with excellent 65.5dB signal-to-noise ratio

(SNR) at 200MHz. The SNR remains flat (within 3dB) for

input tones up to 250MHz. This makes the MAX1219

ideal for wideband applications such as communications

receivers, cable head-end receivers, and power-amplifi-

er predistortion in cellular base-station transceivers.

The MAX1219 operates from a single 1.8V power sup-

ply. The analog inputs of each channel are designed

for AC-coupled, differential or single-ended operation.

The ADC also features a selectable on-chip divide-by-2

clock circuit that accepts clock frequencies as high as

420MHz and reduces the phase noise of the input

clock source. A low-voltage differential signal (LVDS)

sampling clock is recommended for best performance.

The converter’s digital outputs are LVDS compatible

and the data format can be selected to be either two’s

complement or offset binary.

The MAX1219 is available in a 100-pin TQFP package

with exposed paddle and is specified over the extend-

ed (-40°C to +85°C) temperature range. Refer to the

MAX1218 (170Msps) and the MAX1217 (125Msps)

data sheets for lower speed, pin-compatible devices.

Applications

Cable Modem Termination Systems (CMTS)

Cable Digital Return Path Transmitters

Cellular Base-Station Power-Amplifier Linearization

IF and Baseband Digitization

ATE and Instrumentation

Radar Systems

Features

o 210Msps Conversion Rate

o Excellent Low-Noise Characteristics

SNR = 66.6dB at fIN = 100MHz

SNR = 65.5dB at fIN = 200MHz

o Excellent Dynamic Range

SFDR = 81dBc at fIN = 100MHz

SFDR = 79dBc at fIN = 200MHz

o Single 1.8V Supply

o 1.6W Power Dissipation at fSAMPLE = 210Msps

and fIN = 10MHz

o On-Chip Track-and-Hold Amplifier

o Internal 1.24V Bandgap Reference

o On-Chip Selectable Divide-by-2 Clock Input

o LVDS Digital Outputs with Data Clock Output

o EV Kit Available (Order MAX1219EVKIT)

Ordering Information

PART

TEMP RANGE

PIN-PACKAGE

PKG

CODE

MAX1219ECQ -40°C to +85°C 100 TQFP-EP* C100E-6

*EP = Exposed paddle.

Pin-Compatible Versions

PART

MAX1219

MAX1218

MAX1217

RESOLUTION

(BITS)

12

12

12

SPEED GRADE

(Msps)

210

170

125

Pin Configuration appears at end of data sheet.

________________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

1 page

www.DataSheet4U.com

1.8V, Dual, 12-Bit, 210Msps ADC for

Broadband Applications

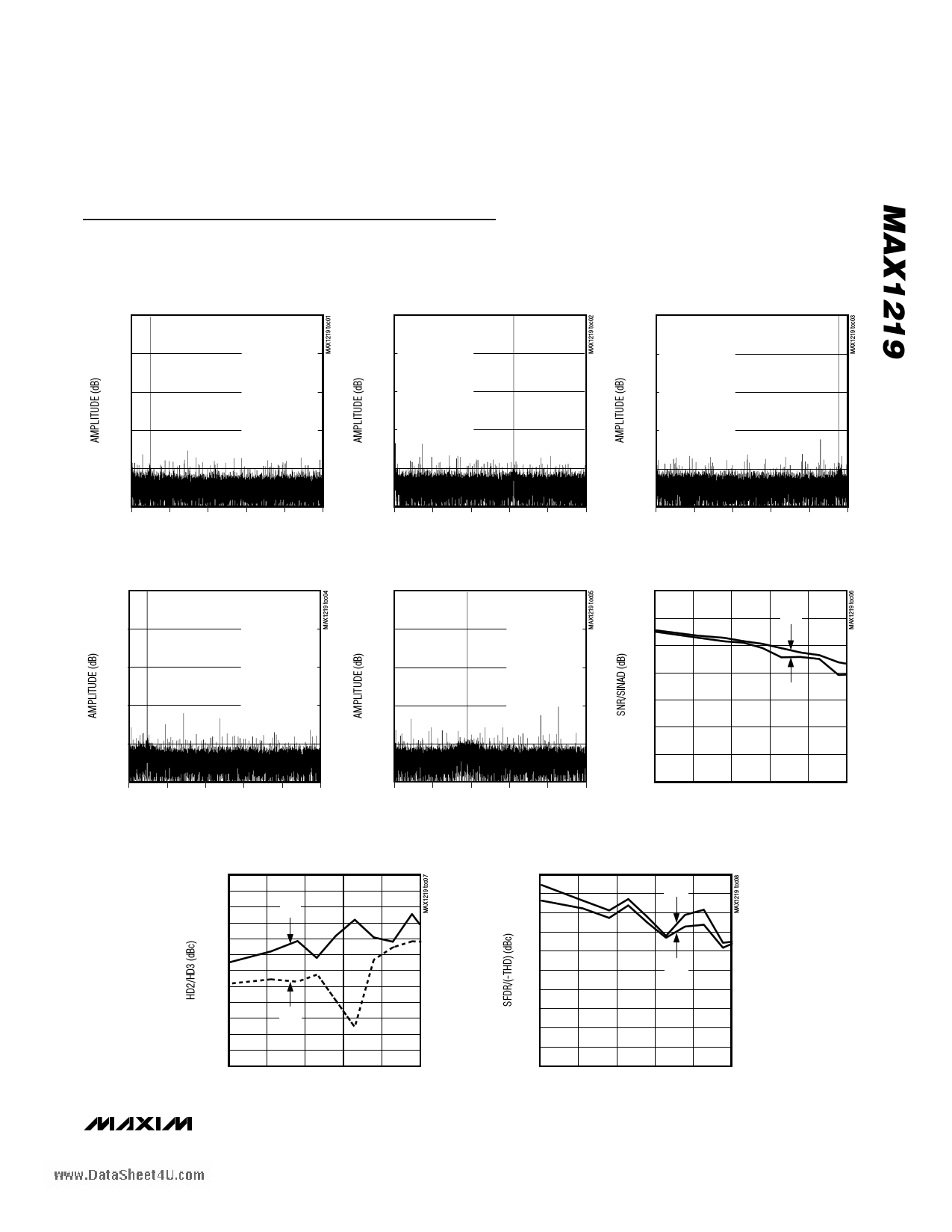

Typical Operating Characteristics

(AVCC = OVCC = 1.8V, fSAMPLE = 210MHz, differential input and differential sine-wave clock signal, 0.1µF capacitors on REFA and

REFB, internal reference, digital output differential RL = 100Ω, TA = +25°C, unless otherwise noted.)

FFT PLOT

FFT PLOT

(16,384 SAMPLES)

(16,384 SAMPLES)

00

fIN = 10.3Hz

fIN = 65Hz

fSAMPLE = 210MHz

fSAMPLE = 210MHz

-25

AIN = -1dBFS

-25 AIN = -1.041dBFS

SINAD = 67.026dB

SINAD = 66.596dB

SNR = 67.129dB

SNR = 66.745dB

-50

THD = -83.324dBc

-50 THD = -81.307dBc

SFDR = 87.469dBc

SFDR = 83.358dBc

HD2 = -94.214dBc

HD2 = -92.863dBc

-75

HD3 = -87.469dBc

-75 HD3 = -84.022dBc

FFT PLOT

(16,384 SAMPLES)

0

fIN = 100Hz

fSAMPLE = 210MHz

-25 AIN = -0.971dBFS

SINAD = 66.323dB

SNR = 66.576dB

-50 THD = -78.811dBc

SFDR = 80.762dBc

HD2 = -93.597dBc

-75 HD3 = -80.764dBc

-100 -100 -100

-125

0

0

-25

-50

-75

21 42 63 84

ANALOG INPUT FREQUENCY (MHz)

105

FFT PLOT

(16,384 SAMPLES)

fIN = 200Hz

fSAMPLE = 210MHz

AIN = -0.949dBFS

SINAD = 65.17dB

SNR = 65.5dB

THD = -76.527dBc

SFDR = 79.593dBc

HD2 = -86.659dBc

HD3 = -79.593dBc

-100

-125

0

21 42 63 84

ANALOG INPUT FREQUENCY (MHz)

105

-125

0

0

-25

-50

-75

21 42 63 84

ANALOG INPUT FREQUENCY (MHz)

105

FFT PLOT

(16,384 SAMPLES)

fIN = 250Hz

fSAMPLE = 210MHz

AIN = -1.039dBFS

SINAD = 63.842dB

SNR = 64.779dB

THD = -70.965dBc

SFDR = 72.255dBc

HD2 = -80.836dBc

HD3 = -72.255dBc

-100

-125

0

21 42 63 84

ANALOG INPUT FREQUENCY (MHz)

105

-125

0

21 42 63 84

ANALOG INPUT FREQUENCY (MHz)

105

SNR/SINAD vs. ANALOG INPUT FREQUENCY

(fSAMPLE = 210MHz, AIN = -1dBFS)

70

68 SNR

66

64

SINAD

62

60

58

56

10

60 110 160 210

ANALOG INPUT FREQUENCY (MHz)

260

HD2/HD3 vs. ANALOG INPUT FREQUENCY

(fSAMPLE = 210MHz, AIN = -1dBFS)

-60

-65

-70 HD3

-75

-80

-85

-90

-95

-100

-105 HD2

-110

-115

-120

10

60 110 160 210 260

ANALOG INPUT FREQUENCY (MHz)

SFDR/(-THD) vs. ANALOG INPUT FREQUENCY

(fSAMPLE = 210MHz, AIN = -1dBFS)

90

85 SFDR

80

75

70

65 -THD

60

55

50

45

40

10

60 110 160 210

ANALOG INPUT FREQUENCY (MHz)

260

_______________________________________________________________________________________ 5

5 Page

www.DataSheet4U.com

1.8V, Dual, 12-Bit, 210Msps ADC for

Broadband Applications

Detailed Description

Theory of Operation

The MAX1219 uses a fully differential pipelined archi-

tecture that allows for high-speed conversion, opti-

mized accuracy, and linearity while minimizing power

consumption.

Both positive inputs (INAP, INBP) and negative/comple-

mentary analog inputs (INAN, INBN) are centered

around a 0.8V common-mode voltage, and each

accept a ±VFS / 4 differential analog input voltage

swing, providing a 1.475VP-P typical differential full-

scale signal swing. Each set of inputs (INAP, INAN and

INBP, INBN) is sampled when the differential sampling

clock signal transitions high. When using the clock-

divide mode, the analog inputs are sampled at every

other high transition of the differential sampling clock.

Each pipeline converter stage converts its input voltage

to a digital output code. At every stage, except the last,

the error between the input voltage and the digital out-

put code is multiplied and passed along to the next

pipeline stage. Digital error correction compensates for

ADC comparator offsets in each pipeline stage and

ensures no missing codes. The result is a 12-bit parallel

digital output word in selectable two’s-complement or

offset binary output formats with LVDS-compatible out-

put levels (Figure 1).

Analog Inputs

The MAX1219 features two sets of fully differential

inputs (INAP, INAN and INBP, INBN) for each input

channel. Differential inputs feature good rejection of

even-order harmonics, which allows for enhanced AC

performance as the signals are progressing through

the analog stages. The MAX1219 analog inputs are

self-biased at a 0.8V common-mode voltage and allow

a 1.475VP-P differential input voltage swing (Figure 2).

Both sets of inputs are self-biased through 1kΩ resis-

tors, resulting in a typical 2kΩ differential input resis-

tance. Drive the analog inputs of the MAX1219 in

AC-coupled configuration to achieve best dynamic per-

formance. See the Transformer-Coupled, Differential

Analog Input Drive section.

On-Chip Reference Circuit

The MAX1219 features an internal 1.24V bandgap ref-

erence circuit (Figure 3), which, in combination with two

internal reference-scaling amplifiers, determines the

FSR of each channel. Bypass REFA and REFB with a

0.1µF capacitor to AGND. Adjust the voltage of the

bandgap reference for each channel independently by

adding an external resistor (e.g., 100kΩ trim poten-

tiometer) between REFADJA/REFADJB and AGND or

REFADJA/REFADJB and REFA/REFB to compensate

for gain errors or increase the FSR of each channel.

See the Applications Information section for a detailed

description of this process.

To disable the internal reference for each channel, con-

nect the reference adjust input (REFADJA, REFADJB)

to AVCC. Apply an external, stable reference to the

channel’s reference input/output (REFA, REFB) to set

the converter’s full scale. To enable the internal refer-

ence for a channel, connect the appropriate reference

adjust input (REFADJA, REFADJB) to AGND.

Clock Inputs (CLKP, CLKN)

Drive the clock inputs of the MAX1219 with an LVDS-

compatible clock to achieve the best dynamic perfor-

mance. The clock signal source must be a high-quality,

low phase noise to avoid any degradation in the noise

performance of the ADC. The clock inputs (CLKP,

CLKN) are internally biased to 1.15V to accept a typical

0.5VP-P differential signal swing (Figure 4). See the

Differential, AC-Coupled PECL-Compatible Clock Input

section for more circuit details on how to drive CLKP and

CLKN appropriately. Although not recommended, the

clock inputs also accept a single-ended input signal.

The MAX1219 also features an internal clock-manage-

ment circuit (duty-cycle equalizer) to ensure that the

clock signal applied to inputs CLKP and CLKN is

processed to provide a 50% duty-cycle clock signal that

desensitizes the performance of the converter to varia-

tions in the duty cycle of the input clock source. The

clock duty-cycle equalizer cannot be turned off exter-

nally and requires a minimum 40MHz clock frequency to

allow the device to meet data sheet specifications.

If the MAX1219 is not clocked, the digital outputs begin

to change state randomly, resulting in a supply current

increase of up to 40mA.

Clock Outputs (DCON, DCOP)

The MAX1219 features a differential clock output, which

can be used to latch the digital output data with an

external latch or receiver. Additionally, the clock output

can be used to synchronize external devices (e.g.,

FPGAs) to the ADC. DCOP and DCON are differential

outputs with LVDS-compatible voltage levels. There is a

3.7ns (typ) delay between the rising (falling) edge of

CLKP (CLKN) and the rising (falling) edge of DCOP

(DCON). See Figure 5 for timing details.

______________________________________________________________________________________ 11

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet MAX1219.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX121 | 308Ksps ADC with DSP Interface and 78dB SINAD | Maxim Integrated |

| MAX1211 | IF Sampling ADC | Maxim Integrated |

| MAX1213 | 170Msps ADC | Maxim Integrated |

| MAX1213 | 250Msps Analog-to-Digital Converter | Maxim Integrated Products |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |