|

|

PDF WV3DG72256V-AD2 Data sheet ( Hoja de datos )

| Número de pieza | WV3DG72256V-AD2 | |

| Descripción | 2GB - 2x128Mx72 SDRAM | |

| Fabricantes | White Electronic Designs | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de WV3DG72256V-AD2 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

White Electronic Designs

WV3DG72256V-AD2

PRELIMINARY

2GB – 2x128Mx72 SDRAM, REGISTERED

FEATURES

Burst Mode Operation

Auto and Self Refresh capability

LVTTL compatible inputs and outputs

Serial Presence Detect with EEPROM

Fully synchronous: All signals are registered on the

positive edge of the system clock

Programmable Burst Lengths: 1, 2, 4, 8 or Full

Page

3.3V ± 0.3V Power Supply

Dual Rank

168 Pin DIMM JEDEC

• PCB - AD2: 28.58mm (1.125”) TYP

DESCRIPTION

The WV3DG72256V is a 2x128Mx72 synchronous DRAM

module which consists of eighteen 256Mx4 stack SDRAM

components (stacked from 128Mx4) in TSOP II package,

two 18 bit Drive ICs for input control signal and one 2Kb

EEPROM in an 8 pin TSSOP package for Serial Presence

Detect which are mounted on a 168 pin DIMM multilayer

FR4 Substrate.

* This product is under development, is not qualified or characterized and is subject to

change without notice.

NOTE: Consult factory for availability of:

• RoHS compliant products

• Vendor source control options

• Industrial temperature option

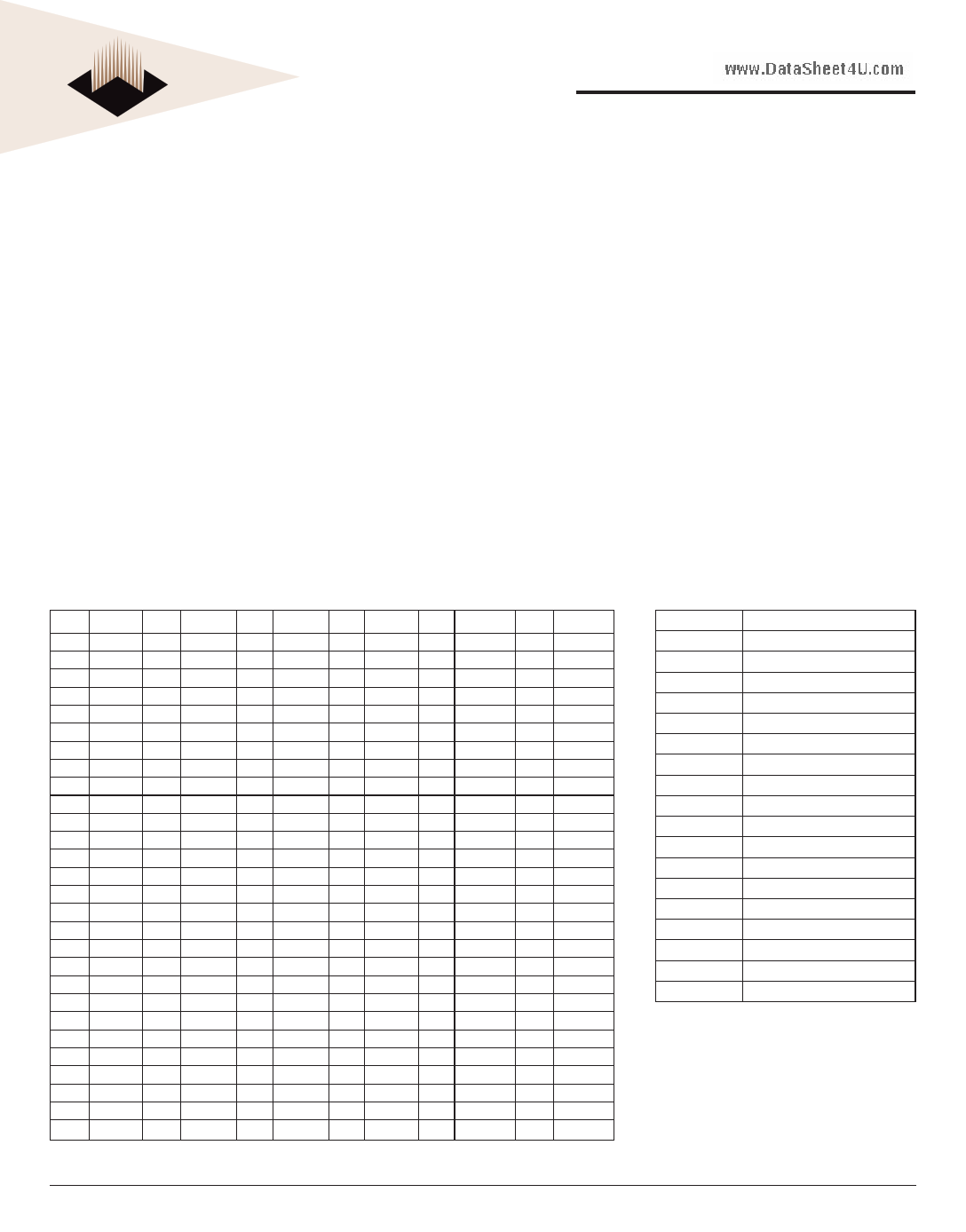

PIN CONFIGURATIONS (FRONT SIDE/BACK SIDE)

PIN FRONT PIN BACK PIN FRONT PIN BACK PIN BACK PIN BACK

1 VSS 29 DQM1 57 DQ18 85 VSS 113 DQM5 141 DQ50

2 DQ0 30 CS0# 58 DQ19 86 DQ32 114 CS1# 142 DQ51

3 DQ1 31 NC 59 VCC 87 DQ33 115 RAS# 143 VCC

4 DQ2 32 VSS 60 DQ20 88 DQ34 116 VSS 144 DQ52

5 DQ3 33 A0 61 NC 89 DQ35 117 A1 145 NC

6 VCC 34 A2 62 *VREF 90 VCC 118 A3 146 *VREF

7 DQ4 35 A4 63 *CKE1 91 DQ36 119 A5 147 REGE

ww8 w.DaDtaQS5 heet346U.comA6 64 VSS 92 DQ37 120 A7 148 VSS

9 DQ6 37 A8 65 DQ21 93 DQ38 121 A9 149 DQ53

10 DQ7 38 A10/AP 66 DQ22 94 DQ39 122 BA0 150 DQ54

11 DQ8 39 BA1 67 DQ23 95 DQ40 123 A11 151 DQ55

12 VSS 40 VCC 68 VSS 96 VSS 124 VCC 152 VSS

13 DQ9 41 VCC 69 DQ24 97 DQ41 125 NC 153 DQ56

14 DQ10 42 CLK0 70 DQ25 98 DQ42 126 A12 154 DQ57

15 DQ11 43 VSS 71 DQ26 99 DQ43 127 VSS 155 DQ58

16 DQ12 44 NC 72 DQ27 100 DQ44 128 CKE0 156 DQ59

17 DQ13 45 CS2# 73 VCC 101 DQ45 129 CS3# 157 VCC

18 VCC 46 DQM2 74 DQ28 102 VCC 130 DQM6 158 DQ60

19 DQ14 47 DQM3 75 DQ29 103 DQ46 131 DQM7 159 DQ61

20 DQ15 48 NC 76 DQ30 104 DQ47 132 NC 160 DQ62

21 CB0 49 VCC 77 DQ31 105 CB4 133 VCC 161 DQ63

22 CB1 50 NC 78 VSS 106 CB5 134 NC 162 VSS

23 VSS 51 NC 79 NC 107 VSS 135 NC 163 NC

24 NC 52 CB2 80 NC 108 NC 136 CB6 164 NC

25 NC 53 CB3 81 WP 109 NC 137 CB7 165 SA0

26 VCC 54 VSS 82 SDA 110 VCC 138 VSS 166 SA1

27 WE# 55 DQ16 83 SCL 111 CAS# 139 DQ48 167 SA2

28 DQM0 56 DQ17 84 VCC 112 DQM4 140 DQ49 168 VCC

PIN NAMES

A0 – A12 Address Input (Multiplexed)

BA0-1

Select Bank

DQ0-63

Data Input/Output

CB0-7

Check Bit (Data-In/Data-Out)

CLK0

Clock Input

CKE0

Clock Enable Input

CS0# - CS3# Chip Select Input

RAS#

Row Address Strobe

CAS#

Column Address Strobe

WE# Write Enable

DQM0-7

DQM

VCC Power Supply (3.3V)

VSS Ground

VREF Power Supply for Reference

REGE

Register Enable

SDA Serial Data I/O

SCL Serial Clock

SA0-2

Address in EEPROM

NC No Connect

* Pins not used in this module.

January 2006

Rev. 0

1 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

1 page

White Electronic Designs

WV3DG72256V-AD2

PRELIMINARY*

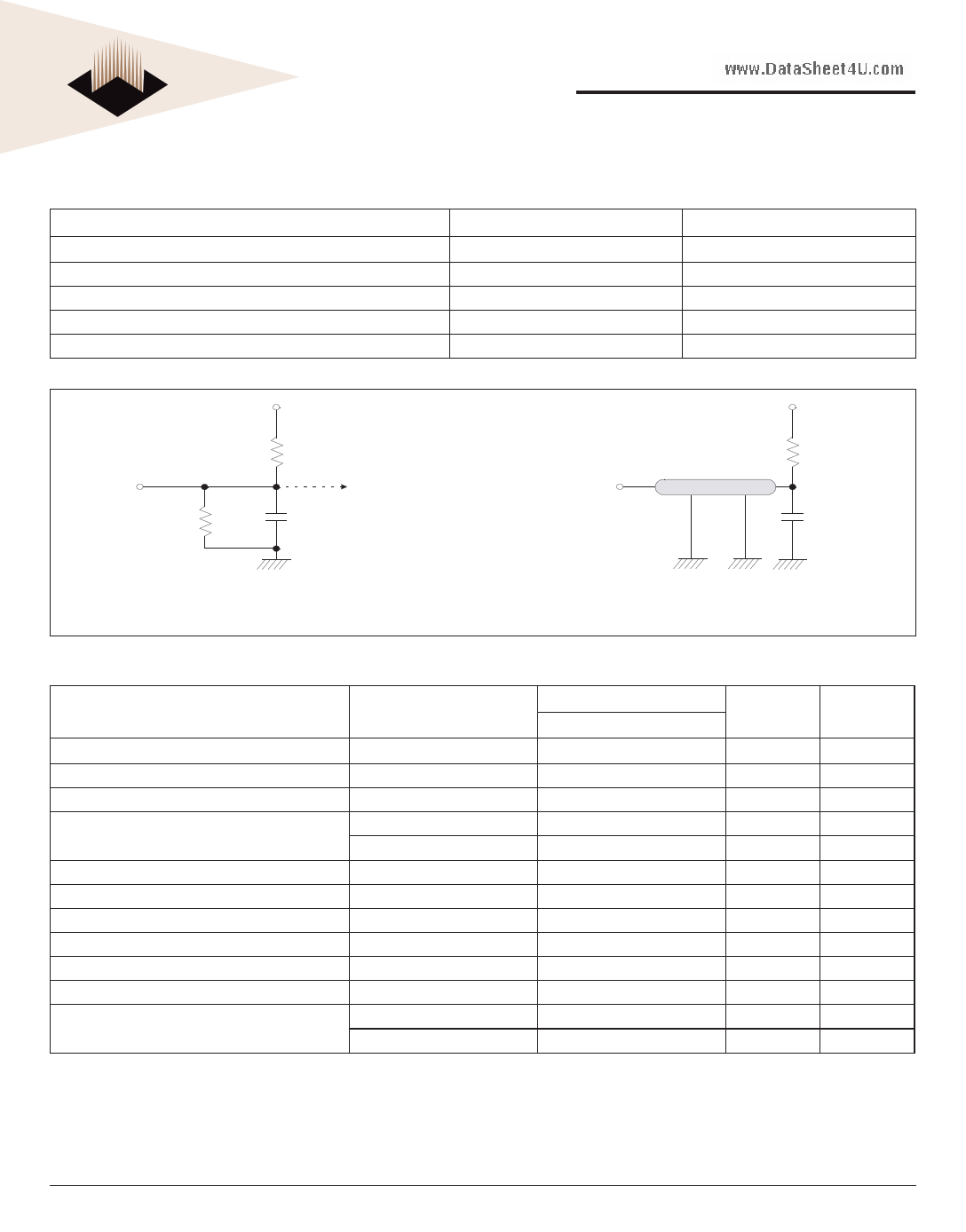

Parameter

AC Input level (VIN/VIL)

Input timing measurement reference level

Input rise and fall time

Output timing measurement reference level

Output load condition

AC OPERATING TEST CONDITIONS

VCC = 3.3V, 0°C ≤ TA ≤ 70°C

Value

2.4/0.4

1.4

tr/tf = 1/1

1.4

See Fig. 2

Output

870

3.3V

1220

50pF

VOH (DC)=2.4V, IOH=-2mA

VOL (DC)=2.4V, IOL=-2mA

Output

Units

V

V

ns

V

Z0 = 50

VTT=1.4V

50

50pF

(Fig. 1) DC output load circuit

(Fig. 2) AC output load circuit

AC OPERATING TEST CONDITIONS

Parameter

Symbol

Value

133/100

Units

Notes

Row active to row active delay

wRwASw#.DtoaCtaASS#hedeelta4yU.com

Row Precharge time

Row active time

Row cycle time

Last data in to row precharge

Last data in to Active delay

tRRD(MIN)

tRCD(MIN)

tRP(MIN)

tRAS(MIN)

tRAS(MAX)

tRC(MIN)

tRDL(MIN)

tDAL(MIN)

15

20

20

45

100

65

2

2 CLK + tRP

ns 1

ns 1

ns 1

ns 1

µs

ns 1

CLK 2

—

Last data in to new col. address delay

Last data in to burst stop

tCDL(MIN)

tBDL(MIN)

1 CLK 1

1 CLK 2

Col. address to col. address delay

Number of valid output data

tCCD(MIN)

CAS Latency = 3

Cas Latency = 2

1 CLK 2

2 CLK 3

1 ea 4

Notes: 1. The minimum number of clock cycles is determined by driving the minimum time required with clock cycle time and then rounding off to the next higher integer.

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

January 2006

Rev. 0

5 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet WV3DG72256V-AD2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| WV3DG72256V-AD2 | 2GB - 2x128Mx72 SDRAM | White Electronic Designs |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |