|

|

PDF ICS5342 Data sheet ( Hoja de datos )

| Número de pieza | ICS5342 | |

| Descripción | 16-Bit Integrated Clock-LUT-DAC | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS5342 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

ICS5342

GENDAC

16-Bit Integrated Clock-LUT-DAC

General Description

Features

The ICS5342 GENDAC is a combination of dual programma- • Triple video DAC, dual clock generator, and 16 bit pixel

ble clock generators, a 256 x 18-bit RAM, and a triple 8-bit

port

video DAC. The GENDAC supports 8-bit pseudo color appli- • Dynamic mode switch allows switching of color depth

cations, as well as 15-bit, 16-bit, and 24-bit True Color bypass

on a pixel by pixel basis

for high speed, direct access to the DACs.

• 24 (packed and sparse), 16, 15, or 8-bit pseudo color

The RAM makes it possible to display 256 colors selected

from a possible 262,144 colors. The dual clock generators use

Phase Locked Loop (PLL) technology to provide program-

mable frequencies for use in the graphics subsystem. The vid-

pixel mode supports True Color, Hi-Color, and VGA

modes

• High speed 256 x 6 x 3 color palette (135 MHz) with

bypass mode and 8-bit DACs

eo clock contains 8 frequencies, all of which are • Eight programmable video (pixel) clock frequencies

programmable by the user. The memory clock has two pro-

(CLK0)

grammable frequency locations.

• DAC power down in blanking mode

The three 8-bit DACs on the ICS5342 are capable of driving

singly or doubly-terminated 75Ω loads to nominal 0 - 0.7

volts at pixel rates up to 135 MHz. Differential and integral

linearity errors are less than 1 LSB over full temperature and

VDD ranges. Monotonicity is guaranteed by design. On-chip

pixel mask register allows displayed colors to be changed in

a single write cycle rather than by modifying the color palette.

• Anti-sparkle circuitry

• On-chip loop filters reduce external components

• Standard CPU interface

• Single external crystal (typically 14.318 MHz)

• Monitor sense

• Internal voltage reference

ICS is the world leader in all aspects of frequency (clock) gen-

eration for graphics, using patented techniques to produce

low jitter video timing.

• 135 MHz (-3), 110 MHz (-2) & 80 MHz (-1) versions

• Very low clock jitter

• Two latched frequency select pins or three non-latched

frequency select pins (programmable)

• Hardware video checksum for manufacturing tests

Block Schematic

PCLK

P0-P15

D0-D7

WR*

RD*

RS0-RS2

STROBE

CS0-CS2

XIN

XOUT

BUFF.

LATCH

MICRO-

PROCESSOR

INTERFACE

8

16

24 BYPS

PIXEL

ADR

AND

MASK

COLOR

PALETTE

256 x 18

BIT

18

MUX

NORM

BLANK*

XTAL

OSC

CTL

16

8 PLL

PARAMETER &

CLK0 PLL

1 PLL

PARAMETER &

CLK1 PLL

2X

COMPARE SENSE*

LATCH

TRIPLE

24 6/8-BIT

DAC

RED

GREEN

BLUE

RSET

VREF

TIMING

GEN.

MUX.

PCLK

MODE

CLK0

CLK1

5342_01.ai

REV. 0.9.0

1 page

www.DataSheet4U.com

Internal Registers

RS2

1

RS1

1

RS0

0

1 01

ICS5342

GENDAC

Register Name

Command

PLL Parameter

Description (all registers can be written to and read from)

This 8-bit register selects color mode, for instance 8-bit Pseudo

Color, Hi-Color, True Color, or XGA, and DAC power down.

The registers are reset to pseudo color mode on power up.

There are 16 PLL parameter registers accessible as indexed by

Read/Write registers. Parameter registers 0F and 0D-00 are two

bytes long and 0E is one byte long. Register 0E is a control reg-

ister. The bits of this register include clock select and enable

functions, the rest contain PLL frequency parameters. After writ-

ing the start index address in the PLL address register, these reg-

isters can be accessed in successive two (or one) bytes. The

address register auto increments after one (0E) or two bytes to

access the entire register

5

5 Page

www.DataSheet4U.com

ICS5342

GENDAC

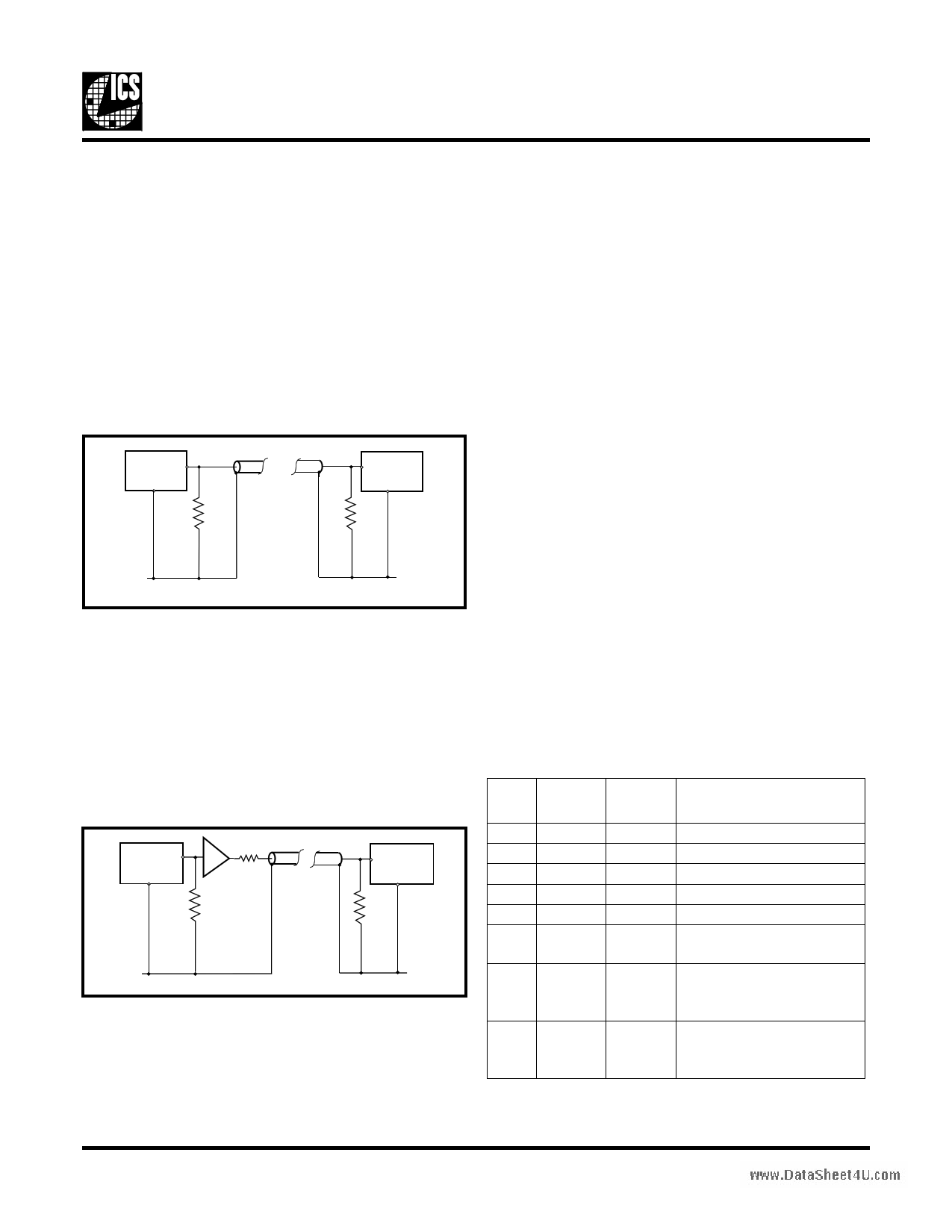

Double Termination (Figure 1)

For this termination scheme, a load resistor is placed at both

the DAC output and the monitor input. The resistor values

should be equal to the characteristic impedance of the line.

Double termination of the DAC output allows both ends of the

transmission line between the DAC outputs and the monitor

inputs to be correctly matched.The result should be an ideal

reflection-free system.

This arrangement is relatively tolerant of variations in trans-

mission line impedance (e.g. a mismatched connector) since

no reflections occur from either end of the line. A doubly ter-

minated DAC output will rise faster than any singly terminat-

ed output because the rise time of the DAC outputs is

dependent on the RC time constant of the load.

ICS5342

MONITOR

RLOAD

RLOAD

Ground

Double Termination

Ground

5342_05

If the GENDAC drives large capacitive loads (for instance

long cable runs), it may be necessary to buffer the DAC out-

puts. The buffer will have a relatively high input impedance.

The connection between the DAC outputs and the buffer in-

puts should also be considered as a transmission line. The

buffer output will have a relatively low impedance. It should

be matched to the transmission line between it and the monitor

with a series terminating resistor. The transmission line

should be terminated at the monitor.

ICS5342

RS

RLOAD

MONITOR

RT

Ground

Buffered Signal

Ground

5342_06

SENSE Output

The GENDAC contains three comparators, one for each of the

DAC output R, G and B lines. The reference voltage to the

comparators is proportional to the VREF (internal or external)

and is typically 0.330 for VREF=1.235 Volts. The SENSE*

pin will be driven low when any analog video output is above

0.385 mV. SENSE* output will be high when all analog out-

puts are below 275 mV. This signal is used to detect the type

of (or lack of) monitor connected to the system.

PLL Clock

The ICS5342 has dual PLL frequency generators for generat-

ing the video clock (CLK0) and memory clock (CLK1) need-

ed for graphics subsystems. Both of these clocks are

generated from a single 14.318 MHz crystal or they can be

driven from an external clock source. The chip includes the

capacitors for the crystal and all of the components needed for

the PLL loop filters, minimizing board component count.

There are eight possible video clock, CLK0, frequencies (f0-

f7) which can be selected by the external pins CS1-CS0. All

clocks are software selectable by setting a bit in the PLL con-

trol register. Frequencies f0-f7 can be programmed for any

frequency by writing appropriate parameter values to the PLL

parameter registers. The default frequencies on power up are

commonly used video frequencies (see table “Video Clock

Default Frequency Registers”). At power up, the frequencies

can be selected by pins CS2-CS0. There are two programma-

ble memory clock frequencies (fA, fB). On power up this fre-

quency defaults to the frequency given in the table:

“MemoryClock Default Frequency Registers.” The memory

clock transition between frequencies is smooth and glitch free

if the N2 PLL parameter is not changed from its previous set-

ting.

Video Clock (CLK0) Default Frequency Register *

fn VCLK M & N Comments

(MHz) Code

f0 25.175 7D 50 VGA0 (VGA Graphics)

f1 28.322 55 49 VGA1 (VGA Text)

f2 31.500 2A 43 VESA 640 x 480 @72 Hz

f3 36.00 77 4A VESA 800 x 600 @56 Hz

f4 40.00 79 49 VESA 800 x 600 @60 Hz

f5 44.889 6F 47 1024 x 768 @43 Hz Inter-

laced

f6 65.00 74 2B 1024 x 768 @ 60 Hz,

640 x 480 Hi-Color @ 72

Hz

f7 75.00 71 29 VESA 1024 x 768 @ 70

Hz,

True Color 640 x 480

* With 14.318 MHz input.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ICS5342.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS5342 | 16-Bit Integrated Clock-LUT-DAC | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |