|

|

PDF XR21V1414 Data sheet ( Hoja de datos )

| Número de pieza | XR21V1414 | |

| Descripción | 4-Ch Full-Speed USB UART | |

| Fabricantes | Exar Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XR21V1414 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

XR21V1414

4-CH FULL-SPEED USB UART

DECEMBER 2013

REV. 1.3.0

GENERAL DESCRIPTION

The XR21V1414 (V1414) is an enhanced 4-channel

USB Universal Asynchronous Receiver and

Transmitter (UART). The USB interface is fully

compliant to Full Speed USB 2.0 specification that

supports 12 Mbps USB data transfer rate. The USB

interface also supports USB suspend, resume and

remote wakeup operations.

The V1414 operates from an internal 48MHz clock

therefore no external crystal/oscillator is required like

previous generation UARTs. With the fractional baud

rate generator, any baud rate can accurately be

generated using the internal 48MHz clock.

The large 128-byte TX FIFO and 384-byte RX FIFO

of the V1414 helps to optimize the overall data

throughput for various applications. If required, the

multidrop mode and automatic RS-485 half-duplex

direction control feature further simplifies typical

multidrop RS-485 applications.

The V1414 operates from a single 2.97 to 3.63 volt

power supply and has 5V tolerant inputs. The V1414

is available in a 48-pin TQFP package.

WHQL certified software drivers for Windows 2000,

XP, Vista, 7, 8, and CE, as well as Linux and Mac are

supported for the XR21V1414.

APPLICATIONS

• Portable Appliances

• External Converters (dongles)

• Battery-Operated Devices

• Cellular Data Devices

• Factory Automation and Process Controls

• Industrial applications

FEATURES

• USB 2.0 Compliant, Full-speed (12 Mbps)

■ Supports USB suspend, resume and remote

wakeup operations

• ± 5 kV HBM ESD protection on USB data pins

• ± 2 kV HBM ESD protection on all other pins

• Enhanced Features of each UART

■ UART data rates up to 12 Mbps

■ Fractional Baud Rate Generator

■ 128 byte TX FIFO

■ 384 byte RX FIFO

■ 7, 8 or 9 data bits

■ 1 or 2 stop bits

■ Odd, even, mark, space, or no parity

■ Automatic Hardware (RTS/CTS or DTR/DSR)

Flow Control

■ Automatic Software (Xon/Xoff) Flow Control

■ Multidrop mode

■ Auto RS-485 Half-Duplex Control

■ Half-Duplex mode

■ Selectable GPIO or Modem I/O

• Internal 48 MHz clock

• Single 3.3V power supply

• 5V tolerant inputs

• 48-pin TQFP package

• Virtual COM Port WHQL certified drivers

■ Windows 2000, XP Vista, Win7 and Win8

■ Windows CE 4.2, 5.0, 6.0, 7.0

■ Linux

■ Mac

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

REV. 1.3.0

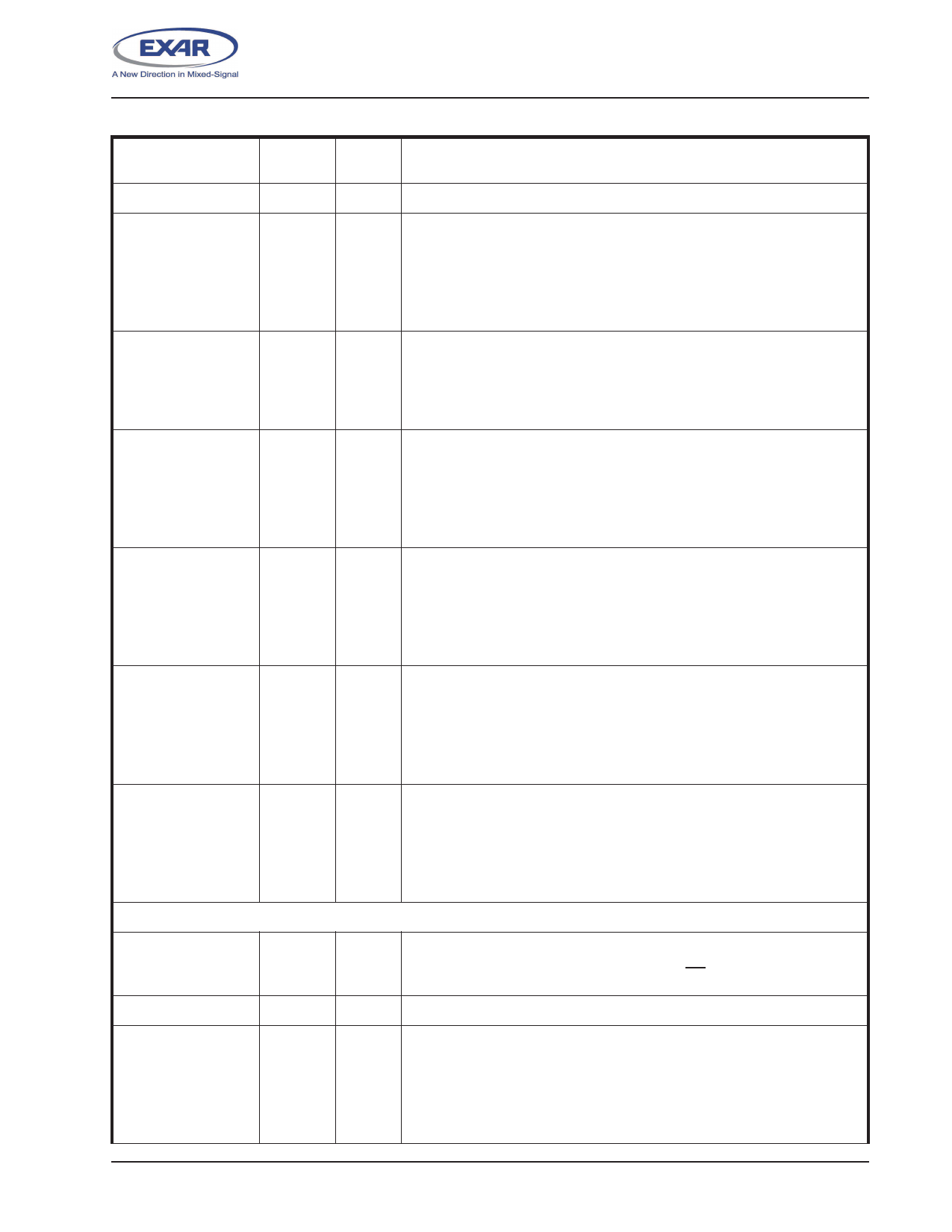

Pin Description

NAME

TXB

GPIOB0/RIB#/

RWKB#

48-QFN

PIN #

8

15

GPIOB1/CDB#

14

GPIOB2/DSRB#

13

GPIOB3/DTRB#

12

GPIOB4/CTSB#

11

GPIOB5/RTSB#/

RS485B

10

UART Channel C Signals

RXC

23

TXC

GPIOC0/RIC#/

RWKC#

22

29

XR21V1414

4-CH FULL-SPEED USB UART

TYPE

DESCRIPTION

O UART Channel B Transmit Data or IR Transmit Data.

I/O UART Channel B general purpose I/O or UART Ring-Indicator input

(active low) or Remote Wakeup Input (See ”Section 1.5.12, USB Sus-

pend” on page 14.). This pin has an internal pull-up resistor which is

disabled during suspend mode. If using this GPIO as an input, an external

pull-up resistor is required to minimize the power consumption in the sus-

pend mode.

I/O UART Channel B general purpose I/O or UART Carrier-Detect input

(active low). This pin has an internal pull-up resistor which is disabled dur-

ing suspend mode. If using this GPIO as an input, an external pull-up

resistor is required to minimize the power consumption in the suspend

mode.

I/O UART Channel B general purpose I/O or UART Data-Set-Ready input

(active low). See ”Section 1.5.6, Automatic DTR/DSR Hardware

Flow Control” on page 13. This pin has an internal pull-up resistor

which is disabled during suspend mode. If using this GPIO as an input, an

external pull-up resistor is required to minimize the power consumption in

the suspend mode.

I/O UART Channel B general purpose I/O or UART Data-Terminal-Ready out-

put (active low). See ”Section 1.5.6, Automatic DTR/DSR Hard-

ware Flow Control” on page 13. This pin has an internal pull-up

resistor which is disabled during suspend mode. If using this GPIO as an

input, an external pull-up resistor is required to minimize the power con-

sumption in the suspend mode.

I/O UART Channel B general purpose I/O or UART Clear-to-Send input

(active low). See ”Section 1.5.5, Automatic RTS/CTS Hardware

Flow Control” on page 13. This pin has an internal pull-up resistor

which is disabled during suspend mode. If using this GPIO as an input, an

external pull-up resistor is required to minimize the power consumption in

the suspend mode.

I/O UART Channel B general purpose I/O or UART Request-to-Send output

(active low) or auto RS-485 half-duplex control. See ”Section 1.5.5,

Automatic RTS/CTS Hardware Flow Control” on page 13. This

pin has an internal pull-up resistor which is disabled during suspend mode.

If using this GPIO as an input, an external pull-up resistor is required to

minimize the power consumption in the suspend mode.

I UART Channel C Receive Data or IR Receive Data. This pin has an inter-

nal pull-up resistor. Internal pull-up resistor is not disabled during suspend

mode.

O UART Channel C Transmit Data or IR Transmit Data.

I/O UART Channel C general purpose I/O or UART Ring-Indicator input

(active low) or Remote Wakeup Input (See ”Section 1.5.12, USB Sus-

pend” on page 14.). This pin has an internal pull-up resistor which is

disabled during suspend mode. If using this GPIO as an input, an external

pull-up resistor is required to minimize the power consumption in the sus-

pend mode.

5

5 Page

XR21V1414

REV. 1.3.0

4-CH FULL-SPEED USB UART

1.3.1.3 Device Attributes

The Device Attributes value replaces the bmAttributes field in the USB Standard Configuration Descriptor. The

default setting in the V1414 device is 0xA0. The bit field definitions are:

• Bit 7 is reserved - set to ’1’

• Bit 6 is Self-powered mode - set to ’0’ for bus-powered, set to ’1’ for self-powered

• Bit 5 is Remote Wakeup support - set to ’0’ for no support, set to ’1’ for remote wakeup support

• Bit 4:0 are reserved - set to ’0’

1.3.1.4 Device Maximum Power

The Device Maximum Power value replaces the bMaxPower field in the USB Standard Configuration

Descriptor. The value specified is in units of 2 mA. For example, the value 0x2F is decimal 47 or 94 mA. Note

that the default bMaxPower of the V1414 device is 94 mA.

1.4 UART Manager

The UART Manager enables/disables each UART including the TX and RX FIFOs for each UART. The UART

Manager is located in a separate register block from the 4 UART channels.

1.5 UART

There are 4 enhanced UART channels in the V1414. Each UART channel is independent, therefore, they will

need to be initialized and configured independently. Each UART can be configured via USB control transfers

from the USB host. At power-up, the V1414 will default to 9600 bps, 8 data bits, no parity bit, 1 stop bit, and no

flow control. If a standard CDC driver accesses the V1414, defaults will change. See ”Section 1.2, USB

Device Driver” on page 9.

1.5.1 Transmitter

The transmitter consists of a 128-byte TX FIFO and a Transmit Shift Register (TSR). Once a bulk-out packet

has been received and the CRC has been validated, the data bytes in that packet are written into the TX FIFO

of the specified UART channel. Data from the TX FIFO is transferred to the TSR when the TSR is idle or has

completed sending the previous data byte. The TSR shifts the data out onto the TX output pin at the data rate

defined by the CLOCK_DIVISOR and TX_CLOCK_MASK registers. The transmitter sends the start bit

followed by the data bits (starting with the LSB), inserts the proper parity-bit if enabled, and adds the stop-

bit(s). The transmitter can be configured for 7 or 8 data bits with or without parity or 9 data bits without parity.

If 9 bit data is selected without wide mode, the 9th bit will always be ’0’.

1.5.1.1 Wide Mode Transmit

When both 9 bit data and wide mode are enabled, two bytes of data must be written. The first byte that is

loaded into the TX FIFO are the first 8 bits (data bits 7-0) of the 9-bit data. Bit-0 of the second byte that is

loaded into the TX FIFO is bit-8 of the 9-bit data. The data that is transmitted on the TX pin is as follows: start

bit, 9-bit data, stop bit. Use the WIDE_MODE register to enable wide mode.

1.5.2 Receiver

The receiver consists of a 384-byte RX FIFO and a Receive Shift Register (RSR). Data that is received in the

RSR via the RX pin is transferred into the RX FIFO. Data from the RX FIFO is transferred to the USB host in

response to a Bulk-In request. Depending on the mode, error / status information for that data character may

or may not be stored in the RX FIFO with the data.

1.5.2.1 Normal receive operation with 7 or 8-bit data

Data that is received is stored in the RX FIFO. Any parity, framing or overrun error or break status information

related to the data is discarded. Receive data format is shown in Figure 3.

1.5.2.2 Normal receive operation with 9-bit data

The first 8 bits of data received is stored in the RX FIFO. The 9th bit as well as any parity, framing or overrun

error or break status information related to the data is discarded.

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet XR21V1414.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XR21V1410 | 1-Ch Full-Speed USB UART | Exar Corporation |

| XR21V1412 | 2-Ch Full-Speed USB UART | Exar Corporation |

| XR21V1414 | 4-Ch Full-Speed USB UART | Exar Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |