|

|

PDF KK16C554PL Data sheet ( Hoja de datos )

| Número de pieza | KK16C554PL | |

| Descripción | QUAD-UART ASYNCHRONOUS COMMUNICATIONS ELEMENT | |

| Fabricantes | KODENSHI KOREA | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de KK16C554PL (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

KK16C554PL/KK16C554TQ

QUAD-UART

ASYNCHRONOUS COMMUNICATIONS ELEMENT

1. General Description

KK16C554 is an enhanced quadruple version of the 16C550 UART (Universal Asynchronous Receiver Transmitter).

Each channel can be put into FIFO mode to relieve the CPU of excessive software overhead. In this mode, internal

FIFOs are activated and 16 bytes plus 3 bit of error data per byte can be stored in both receive and transmit modes.

Each channel performs serial-to-parallel conversion on data characters received from a peripheral device or a

MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the complete

status of the UART at any time during the functional operation. The Status information includes the type and condition

of the transfer operations being performed by the UART, as well as any error conditions such as parity, overrun, framing,

and break interrupt.

KK16C554 includes a programmable baud rate generator which is capable of dividing the timing reference clock input

by divisors of 1 to 216-1, and producing a 16x clock for driving the internal transmitter logic. Provisions are also

included to use this clock to drive the receiver logic.

KK16C554 has complete MODEM-control capability and an interrupt system that can be programmed to the user’s

requirements, minimizing the computing required to handle the communication links.

2. Features

z In the FIFO mode, Each channel’s transmitter and receiver is buffered with 16-byte FIFO to reduce the

number of interrupts to CPU.

z Adds or deletes standard asynchronous communication bits (start, stop, parity) to or from the serial data.

z Holding Register and Shift Register eliminate need for precise synchronization between the CPU and serial

data.

z Independently controlled transmit, receive, line status and data interrupts.

z Programmable Baud Rate Generators which allow division of any input reference clock by 1 to 216-1 and

generate an internal 16X clock.

z Independent receiver clock input

z Modem control functions (CTS#, RTS#, DSR#, DTR#, RI#, and DCD#).

z Fully programmable serial interface characteristics.

- 5-, 6-, 7-, or 8-bit characters

- Even-, Odd-, or No-Parity bit

- 1-, 1.5-, 2-Stop bit generation. ( Like other general UARTs, KK16C554 checks only one stop bit, no matter

how many they are)

z False start bit detection

z Generates or Detects Line Break

z Internal diagnostic capabilities : Loop-back controls for communications link fault isolation.

z Full prioritized interrupt system controls

1

5

1 page

www.DataSheet4U.com

KK16C554PL/KK16C554TQ

QUAD-UART

ASYNCHRONOUS COMMUNICATIONS ELEMENT

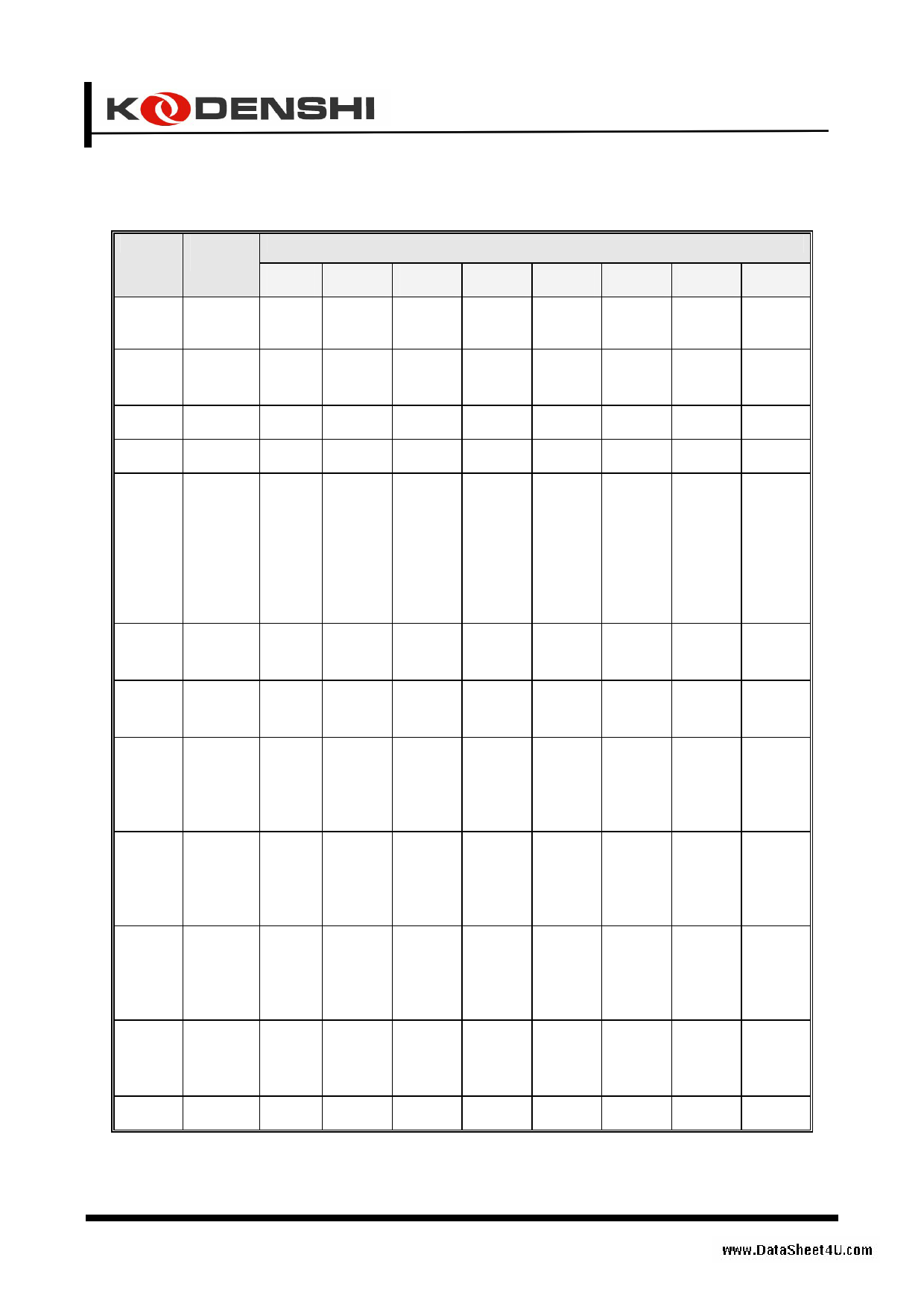

5. Register Description

ADDRESS

REGISTER

MNEMONIC

REGISTER ADDRESS

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

RBR

Data bit Data bit 6 Data bit 5 Data bit 4 Data bit 3 Data bit 2 Data bit 1 Data bit 0

(read only) 7 (MSB)

(LSB)

0

THR

Data bit Data bit 6 Data bit 5 Data bit 4 Data bit 3 Data bit 2 Data bit 1 Data bit 0

(write only) 7

0†

DLL

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1†

DLM

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

(EDSSI) (ERLSI) (ETBEI) (ERBI)

1

IER 0 0

0

0

Enable

Enable

Enable

Enable

modem

receiver Transmitte received

status

line status r

data

interrupt interrupt Holding available

register

interrupt

empty

interrupt

Receiver Receiver Reserved Reserved DMA

Transmit Receiver FIFO

2 FCR Trigger Trigger

mode

FIFO reset FIFO reset enable

(write only) (MSB) (LSB)

select

FIFOs‡ FIFOs‡

0

0

Interrupt‡ Interrupt Interrupt 0

if

2 IIR Enabled Enabled

ID Bit (3) ID Bit (2) ID Bit (1) interrupt

(read only)

pending

(DLAB) Set break Stick

(EPS)

(PEN)

(STB)

(WLSB1) (WLSB0)

3 LCR Divisor

Parity

Even

Parity

Number of Word

Word

latch

parity

Enable

Stop bits length

length

access

select

select bit 1 select bit 0

bit

Loop

OUT2

Reserved (RTS)

(DTR)

4

MCR

0

0

0

Enable

Request to Data

external

Send

terminal

interrupt

ready

(INT)

Error in (TEMT) (THRE) (BI)

(FE) (PE) (OE) (DR)

5

LSR

receiver Transmitte Transmitte Break

Framing Parity

Overrun Data ready

FIFO

r registers r holding interrupt Error

Error

error

empty

register

empty

(DCD) (RI)

(DSR)

(CTS)

(∆DCD) (TERI)

(∆DSR) (∆CTS)

6

MSR

Data Ring

Data set Clear to Delta data Trailing Delta data Delta clear

carrier indicator Ready

Send

carrier

Edge ring set ready to send

detect

detect

indicator

7

SCR

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

† DLAB = 1

‡ This bit is always in a low state when FIFO is disabled.

5

5

5 Page

www.DataSheet4U.com

KK16C554PL/KK16C554TQ

QUAD-UART

ASYNCHRONOUS COMMUNICATIONS ELEMENT

5.5. Interrupt Enable Register

The IER independently enables the four serial channel interrupt sources that activate the interrupt( INT0, INT1, INT2, INT3) output. All interrupts

are disabled by clearing IER0-IER3 of the IER. Interrupts are enabled by setting the appropriate bits of the IER. Disabling the interrupt system

inhibits the IIR and the active high interrupt output. All other system functions operate in their normal manner, including the setting of the LSR and

MSR. The contents of the IER are described in the following bulleted list.

z Bit 0 : When IER0 is set, IER0 enables the received data available interrupt and the timeout interrupts in the FIFO mode.

z Bit 1 : When IER1 is set, the transmitter holding register empty interrupt is enabled.

z Bit 2 : When IER2 is set, the receiver line status interrupt is enabled.

z Bit 3 : When IER3 is set, the modem status interrupt is enabled.

z Bit 4~7 : These bits are cleared.

5.6. Modem Control Register

The MCR controls the interface with the modem or data set as described in Figure 2. MCR can be written and read. The RTS# and DTR# outputs are

directly controlled by their control bits in this register. A high input asserts a low signal at the output terminals. MCR bits 0-4 are shown as follows.

z Bit 0 : When MCR0 is set, the DTR# output is forced low. When MCR0 is cleared, the DTR# output is forced high. The DTR# output of

the serial channel may be input into an inverting line driver in order to obtain the proper polarity input at the modem or data set.

z Bit 1 : When MCR1 is set, the RTS# output is forced to 0. When MCR1 is cleared, the RTS# output is forced high. The DTR# output of

the serial channel may be input into an inverting line driver in order to obtain the proper polarity input at the modem or data set.

z Bit 2 : MCR2 has no affect on operation.

z Bit 3 : When MCR3 is set, the external serial channel interrupt is enabled.

z Bit 4 : MCR4 provides a local loopback feature for diagnostic testing of the channel. When MCR4 is set, serial output TXDx is set to the

high state and SIN is disconnected. The output of the TSR is looped back into the RSR input. The four modem control inputs (CTS#,

DSR#, DCD#, RI#) are disconnected. The modem control outputs (DTR#, RTS#) are internally connected to the four modem control

inputs. The modem control output terminals are forced to their inactive state on the KK16C554. In the diagnostic mode, data transmitted is

immediately received. This allows the processor to verify the transmit and receive data path of the selected serial channel. Interrupt

control is fully operational; however, interrupts are generated by controlling the lower four MCR bits internally. Interrupts are not

generated by activity on the external terminals represented by those four bits.

z Bit 5~7 : These bits are permanently cleared.

11

5

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet KK16C554PL.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KK16C554PL | QUAD-UART ASYNCHRONOUS COMMUNICATIONS ELEMENT | KODENSHI KOREA |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |