|

|

PDF S2204 Data sheet ( Hoja de datos )

| Número de pieza | S2204 | |

| Descripción | Quad Gigabit Ethernet Device | |

| Fabricantes | AMCC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de S2204 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DEVICE

SQPUECAIFDICGAITGIOANBIT ETHERNET DEVICE

QUAD GIGABIT ETHERNET DEVICE

FEATURES

• 1250 MHz (Gigabit Ethernet) operating rate

www.datash-ee1t4/u2.cRomate Operation

• Quad Transmitter with phase-locked loop (PLL)

clock synthesis from low speed reference

• Quad Receiver PLL provides clock and data

recovery

• Internally series terminated TTL outputs

• Low-jitter serial PECL interface

• Individual local loopback control

• JTAG 1149.1 Boundary scan on low speed I/O

signals

• Interfaces with coax, twinax, or fiber optics

• Single +3.3V supply, 2.5 W power dissipation

• Compact 23mm x 23mm 208 TBGA package

APPLICATIONS

• Ethernet Backbones

• Workstation

• Frame buffer

• Switched networks

• Data broadcast environments

• Proprietary extended backplanes

®

S2204

S2204

GENERAL DESCRIPTION

The S2204 facilitates high-speed serial transmission

of data in a variety of applications including Gigabit

Ethernet, serial backplanes, and proprietary point to

point links. The chip provides four separate trans-

ceivers which can be operated individually for a data

capacity of >4 Gbps.

Each bi-directional channel provides parallel to serial

and serial to parallel conversion, clock generation/

recovery, and framing. The on-chip transmit PLL

synthesizes the high-speed clock from a low-speed

reference. The on-chip quad receive PLL is used for

clock recovery and data re-timing on the four inde-

pendent data inputs. The transmitter and receiver

each support differential PECL-compatible I/O for

copper or fiber optic component interfaces with ex-

cellent signal integrity. Local loopback mode allows

for system diagnostics. The chip requires a 3.3V

power supply and dissipates 2.5 watts.

Figure 1 shows the S2204 and S2004 in a Gigabit

Ethernet application. Figure 2 combines the

S2204 with a crosspoint switch to demonstrate a

serial backplane application. Figure 3 is the input/

output diagram. Figures 4 and 5 show the transmit

and receive block diagrams, respectively.

Figure 1. Typical Quad Gigabit Ethernet Application

GE INTERFACE

SERIAL BP DRIVER

MAC

(ASIC)

QUAD

GIGABIT

ETHERNET

INTERFACE

S2204

MAC

(ASIC)

MAC

(ASIC)

MAC

(ASIC)

TO SERIAL BACKPLANE

S2004

July 16, 1999 / Revision C

1

1 page

QUAD GIGABIT ETHERNET DEVICE

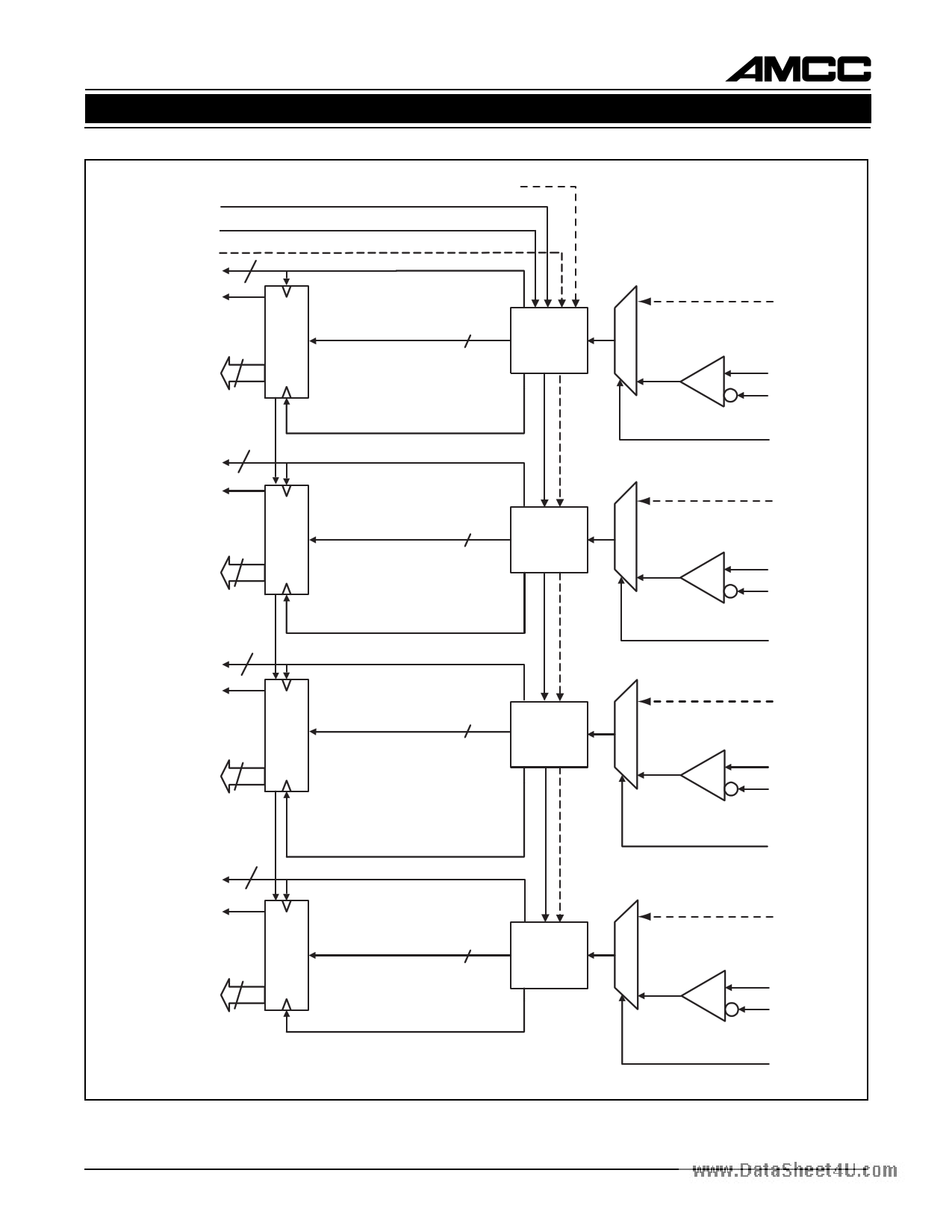

Figure 5. Receiver Block Diagram

CMODE

www.datasheet4u.comRATE

REFCLK

RBC1/0A

2

COM_DETA

10

DOUTA[0:9]

FIFO

(output)

Q

TMODE

10 DOUT CRU

Serial-

Parallel

RBC1/0B

COM_DETB

2

10

DOUTB[0:9]

FIFO

(output)

10 DOUT CRU

Serial-

Parallel

RBC1/0C

COM_DETC

2

10

DOUTC[0:9]

FIFO

(output)

10 DOUT CRU

Serial-

Parallel

2

RBC1/0D

COM_DETD

10

DOUTD[0:9]

FIFO

(output)

10 DOUT CRU

Serial-

Parallel

July 16, 1999 / Revision C

S2204

TXABP

RXAP

RXAN

LPENA

TXBBP

RXBP

RXBN

LPENB

TXCBP

RXCP

RXCN

LPENC

TXDBP

RXDP

RXDN

LPEND

5

5 Page

QUAD GIGABIT ETHERNET DEVICE

JTAG TESTING

The JTAG implementation for the S2204 is compli-

ant with the IEEE1149.1 requirements. JTAG is used

to test the connectivity of the pins on the chip. The

www.daTtaAsPhe,e(tT4ue.scot mAccess Port), provides access to the test

logic of the chip. When TRST is asserted the TAP is

initialized. TAP is a state machine that is controlled

by TMS. The test instruction and data are loaded

through TDI on the rising edge of TCK. When TMS is

high the test instruction is loaded into the instruction

register. When TMS is low the test data is loaded

into the data register. TDO changes on the falling

edge of TCK. All input pins, including clocks, that

have boundary scan are observe only. They can be

sampled in either normal operational or test mode.

All output pins that have boundary scan, are observe

and control. They can be sampled as they are driven

out of the chip in normal operational mode, and they

can be driven out of the chip in test mode using the

Extest instruction. Since JTAG testing operates only

on digital signals there are some pins with analog

signals that JTAG does not cover. The JTAG imple-

mentation has the three required instruction, Bypass,

Extest, and Sample/Preload.

Instruction

BYPASS

EXTEST

SAMPLE/PRELOAD

ID CODE

Code

11

00

01

10

S2204

JTAG Instruction Description:

The BYPASS register contains a single shift-register

stage and is used to provide a minimum-length serial

path between the TDI and TDO pins of a component

when no test operation of that component is re-

quired. This allows more rapid movement of test

data to and from other components on a board that

are required to perform test operations.

The EXTEST instruction allows testing of off-chip cir-

cuitry and board level interconnections. Data would

typically be loaded onto the latched parallel outputs

of boundary-scan shift-register stages using the

SAMPLE/PRELOAD instruction prior to selection of

the EXTEST instruction.

The SAMPLE/PRELOAD instruction allows a snap-

shot of the normal operation of the component to be

taken and examined. It also allows data values to be

loaded onto the latched parallel outputs of the

boundary-scan shift register prior to selection of the

other boundary-scan test instructions.

The following table provides a list of the pins that are

JTAG tested. Each port has a boundary scan regis-

ter (BSR), unless otherwise noted. The following fea-

tures are described: the JTAG mode of each

register (input, output2, or internal (refers to an inter-

nal package pin)), the direction of the port if it has a

boundary scan register (in or out), and the position

of this register on the scan chain.

July 16, 1999 / Revision C

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S2204.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S2202 | Dual Gigabit Ethernet Device | AMCC |

| S2204 | Quad Gigabit Ethernet Device | AMCC |

| S2206 | N-channel SiC power MOSFET bare die | ROHM Semiconductor |

| S220R | Single & Dual Output DC/DC Converters | Minmax Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |