|

|

PDF IDT82V3001A Data sheet ( Hoja de datos )

| Número de pieza | IDT82V3001A | |

| Descripción | WAN PLL WITH SINGLE REFERENCE INPUT | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT82V3001A (archivo pdf) en la parte inferior de esta página. Total 27 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

WAN PLL WITH SINGLE

REFERENCE INPUT

IDT82V3001A

FEATURES

• Supports AT&T TR62411 and Telcordia GR-1244-CORE Stra-

tum 4 Enhanced and Stratum 4 timing for DS1 interfaces

• Supports ETSI ETS 300 011, TBR 4, TBR 12 and TBR 13 tim-

ing for E1 interface

• Selectable input reference signal: 8 kHz, 1.544 MHz or 2.048

MHz

• Provides eight types of clock signals: C1.5o, C3o, C2o, C4o,

C6o, C8o, C16o and C32o

• Provides six types of 8 kHz framing pulses: F0o, F8o, F16o,

F32o, RSP and TSP

• Holdover frequency accuracy of 0.025 ppm

• Phase slope of 5 ns/125 µs

• Attenuates wander from 2.1 Hz

• Fast Lock mode

• Provides Time Interval Error (TIE) correction

• MTIE of 600 ns

• JTAG boundary scan

• Holdover status indication

• Freerun status indication

• Normal status indication

• Lock status indication

• 3.3 V operation with 5 V tolerant I/O

• Package available: 56-pin SSOP

DESCRIPTION

The IDT82V3001A is a WAN PLL with single reference input. It

contains a Digital Phase-Locked Loop (DPLL), which generates ST-BUS

clocks and framing signals that are phase locked to a 2.048 MHz, 1.544

MHz or 8 kHz input reference.

The IDT82V3001A provides eight types of clock signals (C1.5o, C3o,

C6o, C2o, C4o, C8o, C16o, C32o) and six types of framing signals (F0o,

F8o, F16o, F32o, RSP, TSP) for the multitrunk T1 and E1 primary rate

transmission links.

The IDT82V3001A is compliant with AT&T TR62411, Telcordia GR-

1244-CORE Stratum 4 Enhanced and Stratum 4, ETSI ETS 300 011. It

meets the jitter/wander tolerance, jitter/wander transfer, intrinsic jitter/

wander, frequency accuracy, capture range, phase change slope,

holdover frequency accuracy and MTIE (Maximum Time Interval Error)

requirements for these specifications.

The IDT82V3001A can be used in synchronization and timing control

for T1 and E1 systems, or used as ST-BUS clock and frame pulse

sources. It can also be used in access switch, access routers, ATM edge

switches, wireless base station controllers, or IADs (Integrated Access

Devices), PBXs and line cards.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

2003 Integrated Device Technology, Inc.

1

OCTOBER 22, 2003

DSC-6242/2

1 page

IDT82V3001A WAN PLL WITH SINGLE REFERENCE INPUT

INDUSTRIAL TEMPERATURE RANGE

LIST OF TABLES

Table - 1 Pin Description .................................................................................................................................................. 7

Tabwleww- .2DataSOhepeetr4aUt.icnogmModes and Status........................................................................................................................... 10

Table - 3 Input Reference Frequency Selection ............................................................................................................. 12

Table - 4 Absolute Maximum Ratings**.......................................................................................................................... 18

Table - 5 Recommended DC Operating Conditions** .................................................................................................... 18

Table - 6 DC Electrical Characteristics** ........................................................................................................................ 18

Table - 7 Performance.................................................................................................................................................... 19

Table - 8 Intrinsic Jitter Unfiltered................................................................................................................................... 19

Table - 9 C1.5o (1.544 MHz) Intrinsic Jitter Filtered....................................................................................................... 20

Table - 10 C2o (2.048 MHz) Intrinsic Jitter Filtered.......................................................................................................... 20

Table - 11 8 kHz Input to 8 kHz Output Jitter Transfer ..................................................................................................... 20

Table - 12 1.544 MHz Input to 1.544 MHz Output Jitter Transfer..................................................................................... 20

Table - 13 2.048 MHz Input to 2.048 MHz Output Jitter Transfer..................................................................................... 21

Table - 14 8 kHz Input Jitter Tolerance ............................................................................................................................ 21

Table - 15 1.544 MHz Input Jitter Tolerance .................................................................................................................... 21

Table - 16 2.048 MHz Input Jitter Tolerance .................................................................................................................... 22

Table - 17 Timing Parameter Measurement Voltage Levels ............................................................................................ 23

Table - 18 Input / Output Timing....................................................................................................................................... 23

5

5 Page

IDT82V3001A WAN PLL WITH SINGLE REFERENCE INPUT

www.DataSheet4U.com

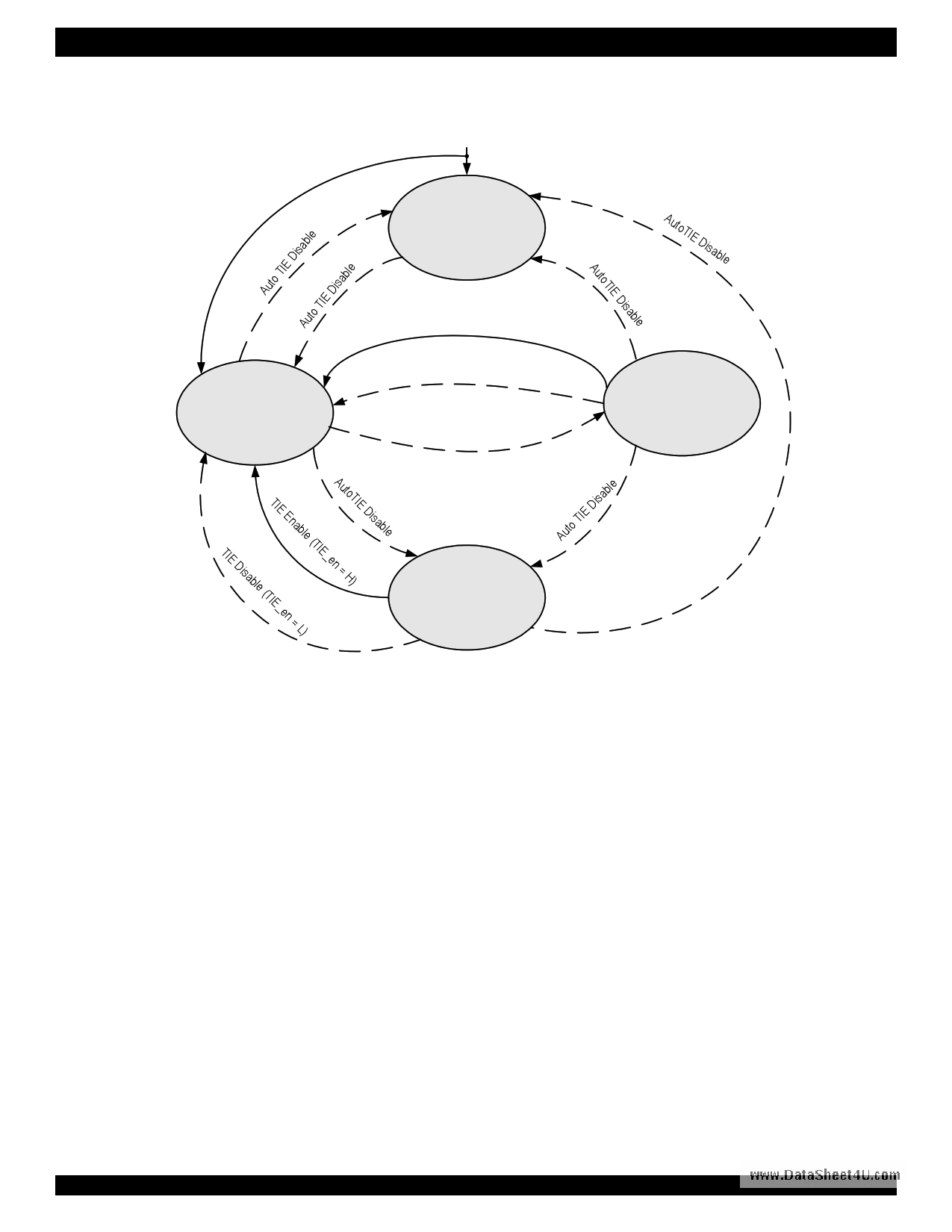

S1

Normal

Mode_sel1=0

Mode_sel0=0

Reset *

S0

Freerun

Mode_sel1=1

Mode_sel0=0

(Valid Input Reference Signal)

TIE Enable (TIE_en = H)

(Valid Input Reference Signal)

TIE Disable (TIE_en = L)

(Invalid Input Reference Signal)

Auto TIE Disable

INDUSTRIAL TEMPERATURE RANGE

AutoTIE Disable

S2

Auto - Holdover

Mode_sel1=0

Mode_sel0=0

S3

Holdover

Mode_sel1=0

Mode_sel0=1

* Note: After reset, Mode_sel1 and Mode_sel0 should be initially set to '10' or '00'.

Figure - 4 State Control Diagram

3.1.1 NORMAL MODE

Normal Mode is typically used when a slave clock source

synchronized to the network is required.

In this mode, the IDT82V3001A provides timing (C1.5o, C3o, C2o,

C4o, C6o, C8o, C16o and C32o) and synchronization (F0o, F8o, F16o,

F32o, TSP, RSP) signals, which are synchronous to the input reference.

The input reference signal has a nominal frequency of 8 kHz, 2.048 MHz

or 1.544 MHz.

From a reset condition, the IDT82V3001A will take 30 seconds at

most to make the output signals synchronous (phase locked) to the input

reference.

Whenever the IDT82V3001A enters Normal Mode, it will give an

indication by setting the NORMAL pin to high.

3.1.2 FAST LOCK MODE

Fast Lock Mode is a submode of Normal Mode. It is used to allow the

IDT82V3001A to lock to a reference more quickly than Normal Mode will

do. Typically, the DPLL will lock to the input reference within 500 ms if

the FLOCK pin is high.

3.1.3 HOLDOVER MODE

Holdover Mode is typically used for short duration (e.g., 2 seconds)

while network synchronization is temporarily disrupted.

In Holdover Mode, the IDT82V3001A provides timing and

synchronization signals, which are not locked to the external reference

signal but based on storage techniques. The storage value is

determined while the device is in Normal Mode and locked to the

external reference signal.

In Normal Mode, when the output signal is locked to the input

reference signal, a numerical value corresponding to the output

frequency is stored alternately in two memory locations every 30 ms.

When the device is switched into Holdover Mode, the stored value in

memory from between 30 ms and 60 ms is used to set the output

frequency of the device.

The frequency accuracy in Holdover Mode is ±0.025 ppm, which

corresponds to the worst case of 18 frame (125 µs per frame) slips in 24

hours. This meets AT&T TR62411 requirement of ±0.37 ppm (255

frame slips per 24 hours).

The HOLDOVER pin will be set to logic high whenever the

IDT82V3001A goes into Holdover Mode.

11

11 Page | ||

| Páginas | Total 27 Páginas | |

| PDF Descargar | [ Datasheet IDT82V3001A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT82V3001A | WAN PLL WITH SINGLE REFERENCE INPUT | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |