|

|

PDF ICS83054I-01 Data sheet ( Hoja de datos )

| Número de pieza | ICS83054I-01 | |

| Descripción | SINGLE-ENDED MULTIPLEXER | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS83054I-01 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

PRELIMINARY

ICS83054I-01

4-BIT, 2:1,

SINGLE-ENDED MULTIPLEXER

GENERAL DESCRIPTION

The ICS83054I-01 is a 4-bit, 2:1, Single-ended Mul-

ICS tiplexer and a member of the HiPerClockS™fam-

HiPerClockS™ ily of High Performance Clock Solutions from ICS.

The ICS83054I-01 has two selectable single-ended

clock inputs and four single-ended clock outputs.

The output has a VDDO pin which may be set at 3.3V, 2.5V, or

1.8V, making the device ideal for use in voltage translation ap-

plications. An output enable pin places the output in

www.DataSheeat4Uh.igcohmimpedance state which may be useful for testing or

debug. Possible applications include systems with up to four

transceivers which need to be independently set for different

rates. For example, a board may have four transceivers, each

of which need to be independently configured for 1 Gigabit

Ethernet or 1 Gigabit Fibre Channel rates. Another possible

application may require the ports to be independently set for

FEC (Forward Error Correction) or non-FEC rates. The device

operates up to 250MHz and is packaged in a 16 TSSOP.

FEATURES

• 4-bit, 2:1 single-ended multiplexer

•

Nominal

output

impedance:

15Ω

(V

DDO

=3

.3V)

• Maximum output frequency: 250MHz

• Propagation delay: 2.5ns (typical)

• Input skew: 45ps (typical)

• Part-to-part skew: TBD

• Additive phase jitter, RMS (12KHz - 20MHz):

0.07ps (typical)

• Operating supply modes:

VDD/VDDO

3.3V/3.3V

3.3V/2.5V

3.3V/1.8V

2.5V/2.5V

2.5V/1.8V

• -40°C to 85°C ambient operating temperature

BLOCK DIAGRAM

SEL0 Pulldown

CLK0

CLK1

Pulldown

Pulldown

0

1

SEL3 Pulldown

OE Pullup

0

1

PIN ASSIGNMENT

SEL3 1 16 SEL0

Q3 2 15 Q0

VDDO 3

1 4 VDDO

GND 4 13 GND

Q0 Q2 5 12 Q1

SEL2 6 11 SEL1

CLK1 7 10 CLK0

VDD 8

9 OE

ICS83054I-01

16-Lead TSSOP

Q3 4.4mm x 3.0mm x 0.92mm package body

G Package

Top View

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on initial

product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

83054AGI-01

www.icst.com/products/hiperclocks.html

REV. A NOVEMBER 24, 2004

1

1 page

Integrated

Circuit

Systems, Inc.

PRELIMINARY

ICS83054I-01

4-BIT, 2:1,

SINGLE-ENDED MULTIPLEXER

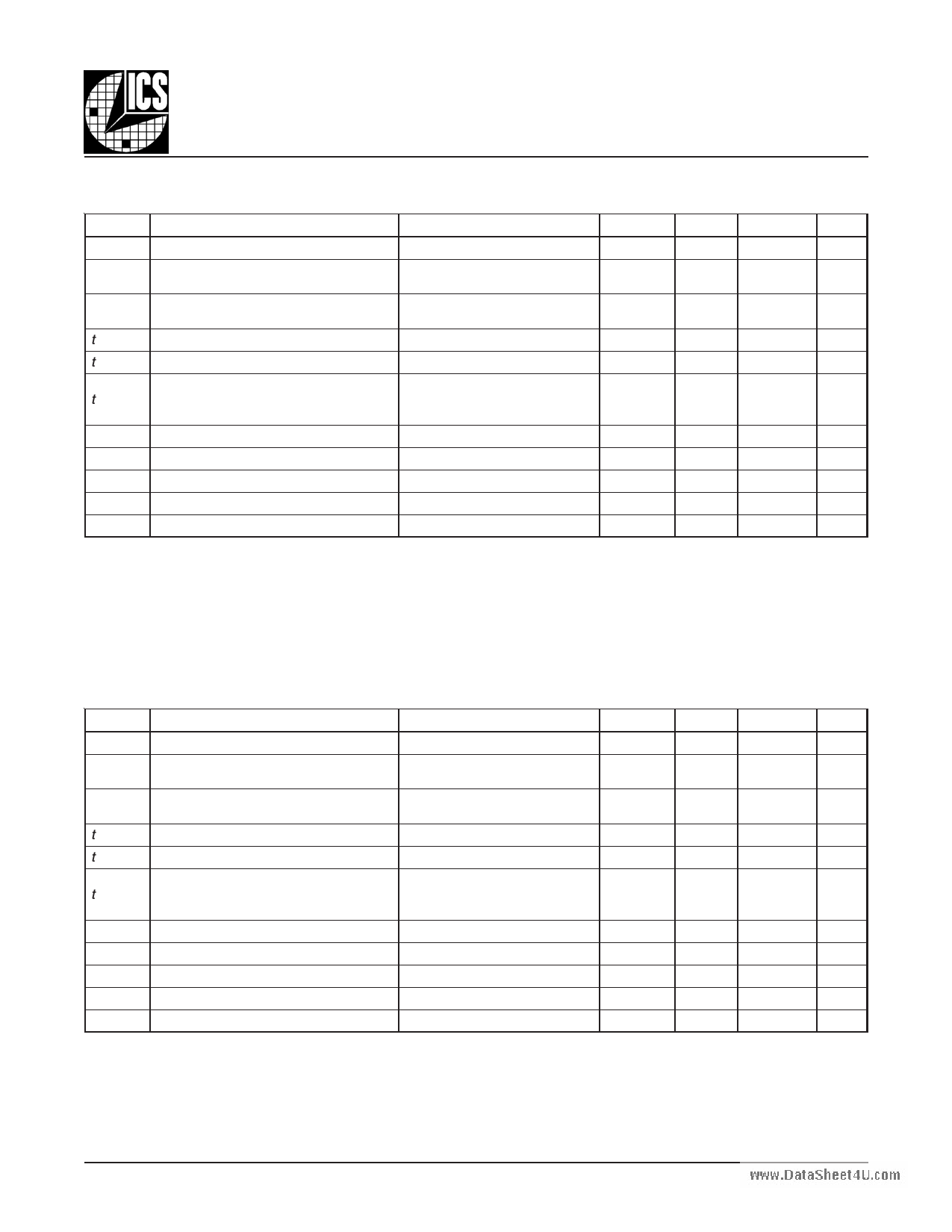

TABLE 5B. AC CHARACTERISTICS, VDD = 3.3V ± 5%, VDDO = 2.5V ± 5%, TA = -40°C TO 85°C

Symbol Parameter

Test Conditions

Minimum Typical Maximum

fMAX

tpLH

tpHL

tsk(i)

www.DataSheet4tsUk.(cpopm)

Output Frequency

Propagation Delay, Low to High;

NOTE 1

Propagation Delay, High to Low;

NOTE 1

Input Skew; NOTE 5

Part-to-Part Skew; NOTE 2, 5

2.7

2.7

38

TBD

250

Buffer Additive Phase Jitter, RMS;

tjit refer to Additive Phase Jitter section,

NOTE 4

Integration Range:

12KHz - 20MHz

0.04

tR / tF

odc

Output Rise/Fall Time

Output Duty Cycle

20% to 80%

550

50

tEN Output Enable Time; NOTE 3

tDIS Output Disable Time; NOTE 3

MUXISOL MUX Isolation

@100MHz

45

NOTE 1A: Measured from VDD/2 of the input to VDDO/2 of the output.

NOTE 2: Defined as skew between outputs on different devices operating a the same supply voltages and

with equal load conditions. Using the same type of input on each device, the output is measured at VDDO/2.

NOTE 3: These parameters are guaranteed by characterization. Not tested in production.

NOTE 4: Driving only one input clock.

NOTE 5: This parameter is defined in accordance with JEDEC Standard 65.

5

5

Units

MHz

ns

ns

ps

ps

ps

ps

%

ns

ns

dB

TABLE

5C.

AC

CHARACTERISTICS,

V

DD

=

3.3V

±

5%,

V

DDO

=

1.8V

±

0.2V,

TA

=

-40°C

TO

85°C

Symbol Parameter

Test Conditions

Minimum Typical Maximum Units

fMAX

tpLH

tpHL

tsk(i)

Output Frequency

Propagation Delay, Low to High;

NOTE 1

Propagation Delay, High to Low;

NOTE 1

Input Skew; NOTE 5

250 MHz

3 ns

3 ns

38 ps

tsk(pp)

tjit

t /t

RF

odc

Part-to-Part Skew; NOTE 2, 5

Buffer Additive Phase Jitter, RMS;

refer to Additive Phase Jitter section,

NOTE 4

Output Rise/Fall Time

Output Duty Cycle

Integration Range:

12KHz - 20MHz

20% to 80%

TBD

0.05

595

50

ps

ps

ps

%

tEN Output Enable Time; NOTE 3

tDIS Output Disable Time; NOTE 3

MUXISOL MUX Isolation

@100MHz

45

NOTE 1A: Measured from VDD/2 of the input to VDDO/2 of the output.

NOTE 2: Defined as skew between outputs on different devices operating a the same supply voltages and

with equal load conditions. Using the same type of input on each device, the output is measured at VDDO/2.

NOTE 3: These parameters are guaranteed by characterization. Not tested in production.

NOTE 4: Driving only one input clock.

NOTE 5: This parameter is defined in accordance with JEDEC Standard 65.

5

5

ns

ns

dB

83054AGI-01

www.icst.com/products/hiperclocks.html

5

REV. A NOVEMBER 24, 2004

5 Page

Integrated

Circuit

Systems, Inc.

PRELIMINARY

ICS83054I-01

4-BIT, 2:1,

SINGLE-ENDED MULTIPLEXER

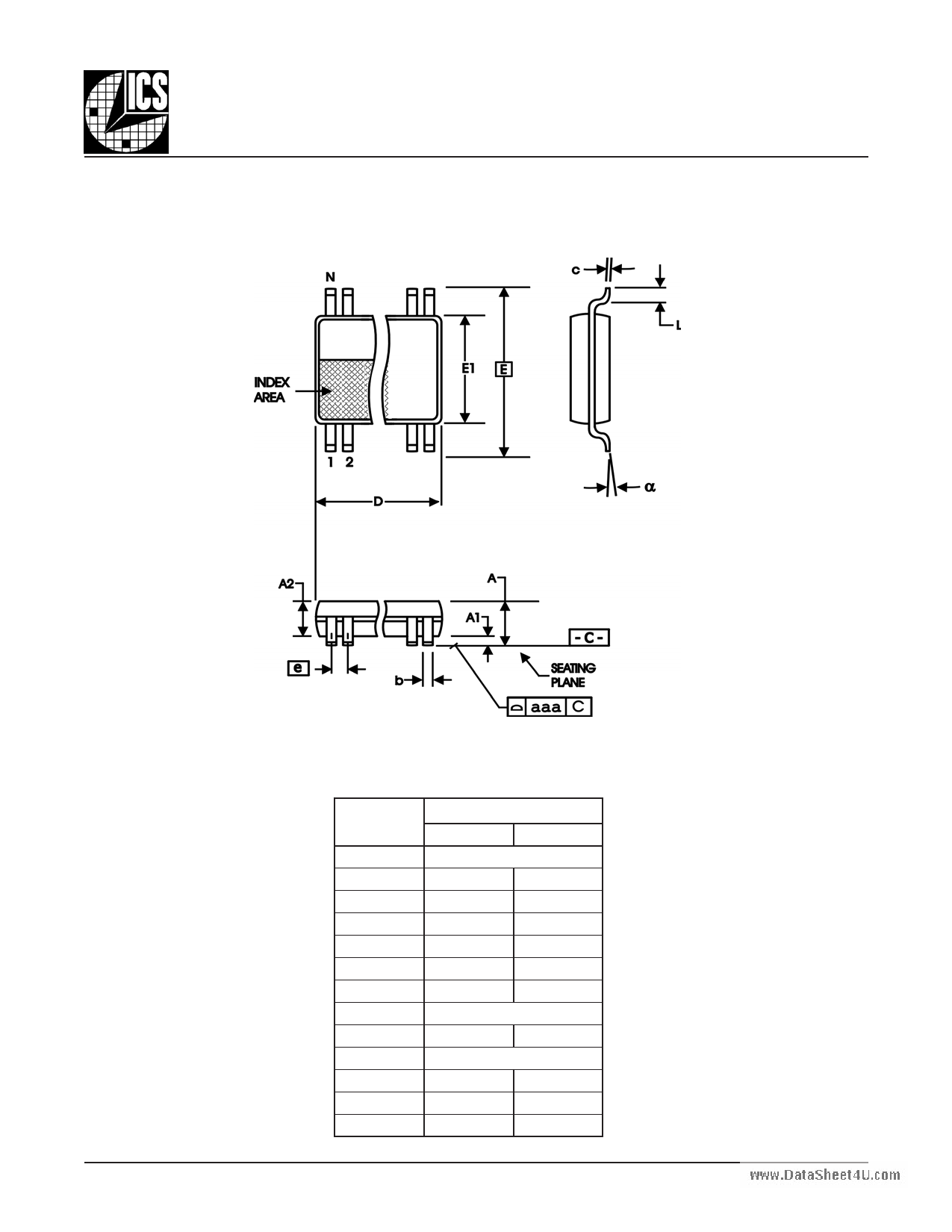

PACKAGE OUTLINE - G SUFFIX FOR 16 LEAD TSSOP

www.DataSheet4U.com

83054AGI-01

TABLE 6. PACKAGE DIMENSIONS

SYMBOL

Millimeters

Minimum

Maximum

N 16

A -- 1.20

A1 0.05 0.15

A2 0.80 1.05

b 0.19 0.30

c 0.09 0.20

D 4.90 5.10

E 6.40 BASIC

E1 4.30 4.50

e 0.65 BASIC

L 0.45 0.75

α 0° 8°

aaa -- 0.10

Reference Document: JEDEC Publication 95, MO-153

www.icst.com/products/hiperclocks.html

11

REV. A NOVEMBER 24, 2004

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet ICS83054I-01.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS83054I-01 | SINGLE-ENDED MULTIPLEXER | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |