|

|

PDF LH543611 Data sheet ( Hoja de datos )

| Número de pieza | LH543611 | |

| Descripción | 512 x 36 x 2 / 1024 x 36 x 2 Synchronous Bidirectional FIFO | |

| Fabricantes | Sharp Electrionic Components | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LH543611 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

LH543611/21

FEATURES

• Pin-Compatible and Functionally

Upwards-Compatible with Sharp LH5420 and

LH543601, but Deeper

• Expanded Control Register that is Fully

Readable as well as Writeable

• Fast Cycle Times: 18/20/25/30/35 ns

• Improved Input Setup and Flag Out Timing

• Two 512 × 36-bit FIFO Buffers (LH543611) or

Two 1024 × 36-bit FIFO Buffers (LH543621)

• Full 36-bit Word Width

• Selectable 36/18/9-bit Word Width on Port B;

Selection May be Changed Without Resetting

the BiFIFO

• Programmable Byte-Order Reversal –

‘Big-Endian ↔ Little-Endian Conversion’

• Independently-Synchronized (‘Fully-Asynchronous’)

Operation of Port A and Port B

• ‘Synchronous’ Enable-Plus-Clock Control at

Both Ports

• R/W, Enable, Request, and Address Control Inputs

are Sampled on the Rising Clock Edge

• Synchronous Request/Acknowledge ‘Handshake’

Capability; Use is Optional

• Device Comes Up Into a Known Default State at

Reset; Programming is Allowed, but is not Required

• Asynchronous Output Enables

• Five Status Flags per Port: Full, Almost-Full,

Half-Full, Almost-Empty, and Empty

• All Flags are Independently Programmable for

Either Synchronous or Asynchronous Operation

• Almost-Full Flag and Almost-Empty Flag Have

Programmable Offsets

• Mailbox Registers with Synchronized Flags

• Data-Bypass Function

• Data-Retransmit Function

• Automatic Byte Parity Checking with

Programmable Parity Flag Latch

• Programmable Byte Parity Generation

• Programmable Byte, Half-Word, or Full-Word

Oriented Parity Operations

• 8 mA-IOL High-Drive Three-State Outputs with

Built-In Series Resistor

• TTL/CMOS-Compatible I/O

• Space-Saving PQFP and TQFP Packages

BOLD = Additions over the 5420/3601 feature set

512 × 36 × 2 / 1024 × 36 × 2

Synchronous Bidirectional FIFO

FUNCTIONAL DESCRIPTION

The LH543611 and LH543621 contain two FIFO buff-

ers, FIFO #1 and FIFO #2. These operate in parallel, but

in opposite directions, for bidirectional data buffering.

FIFO #1 and FIFO #2 each are organized as 512 or 1024

by 36 bits. The LH543611 and LH543621 are ideal either

for wide unidirectional applications or for bidirectional

data applications; component count and board area are

reduced.

The LH543611 and LH543621 have two 36-bit ports,

Port A and Port B. Each port has its own port-synchro-

nous clock, but the two ports may operate asynchro-

nously relative to each other. Data flow is initiated at a port

by the rising edge of the appropriate clock; it is gated by

the corresponding edge-sampled enable, request, and

read/write control signals. At the maximum operating

frequency, the clock duty cycle may vary from 40% to

60%. At lower frequencies, the clock waveform may be

quite asymmetric, as long as the minimum pulse-width

conditions for clock-HIGH and clock-LOW remain satis-

fied; the LH543611 and LH543621 are fully-static parts.

Conceptually, the port clocks CKA and CKB are free-

running, periodic ‘clock’ waveforms, used to control other

signals which are edge-sensitive. However, there actually

is not any absolute requirement that these ‘clock’ wave-

forms must be periodic. An ‘asynchronous’ mode of op-

eration is possible, in one or both directions,

independently, if the appropriate enable and request in-

puts are continuously asserted, and enough aperiodic

‘clock’ pulses of suitable duration are generated by exter-

nal logic to cause all necessary actions to occur.

A synchronous request/acknowledge handshake

facility is provided at each port for FIFO data access. This

request/ acknowledge handshake resolves FIFO full and

empty boundary conditions, when the two ports are op-

erated asynchronously relative to each other.

FIFO status flags monitor the extent to which each

FIFO buffer has been filled. Full, Almost-Full, Half-Full,

Almost-Empty, and Empty flags are included for each

FIFO. Each of these flags may be independently pro-

grammed for either synchronous or asynchronous opera-

tion. Also, the Almost-Full and Almost-Empty flags are

programmable over the entire FIFO depth, but are auto-

matically initialized to eight locations from the respective

FIFO boundaries at reset. Adata block of 512 (LH543611)

or 1024 (LH543621) or fewer words may be retransmitted

any desired number of times.

1

1 page

512 x 36 x 2/1024 x 36 x 2 BiFIFOs

LH543611/21

PIN LIST

SIGNAL

NAME

A0A

A1A

A2A

OEA

FF1

AF1

HF1

PFA

D17A

D16A

D15A

D14A

D13A

D12A

D11A

D10A

D9A

D8A

D7A

D6A

D5A

D4A

D3A

D2A

D1A

D0A

RS

RT1

D0B

D1B

D2B

D3B

D4B

D5B

D6B

D7B

D8B

D9B

D10B

D11B

D12B

D13B

D14B

D15B

D16B

D17B

MBF1

AE1

PQFP

PIN NO.

1

2

3

4

6

7

8

9

10

11

12

14

15

16

17

19

20

21

23

24

25

27

28

29

31

32

33

34

35

36

37

39

40

41

43

44

45

47

48

49

51

52

53

54

56

57

58

59

TQFP

PIN NO.

126

125

124

123

121

120

119

118

117

116

115

113

112

111

110

106

105

104

102

101

100

98

97

96

94

93

92

91

89

88

87

85

84

83

81

80

79

77

76

75

71

70

69

68

66

65

64

63

SIGNAL

NAME

EF1

ACKB

REQB

ENB

R/WB

CKB

A0B

WS0

WS1

OEB

FF2

AF2

HF2

PFB

D18B

D19B

D20B

D21B

D22B

D23B

D24B

D25B

D26B

D27B

D28B

D29B

D30B

D31B

D32B

D33B

D34B

D35B

RT2

D35A

D34A

D33A

D32A

D31A

D30A

D29A

D28A

D27A

D26A

D25A

D24A

D23A

D22A

D21A

PQFP

PIN NO.

60

61

63

64

65

66

67

68

69

70

72

73

74

75

76

77

78

80

81

82

83

85

86

87

89

90

91

93

94

95

97

98

100

101

102

103

105

106

107

109

110

111

113

114

115

117

118

119

TQFP

PIN NO.

62

61

59

58

57

56

55

53

52

51

49

48

47

46

45

44

43

41

40

39

38

34

33

32

30

29

28

26

25

24

22

21

18

17

16

15

13

12

11

9

8

7

5

4

3

143

142

141

SIGNAL

NAME

D20A

D19A

D18A

MBF2

AE2

EF2

ACKA

REQA

ENA

R/WA

CKA

VCC

VSSO

VSSO

VCCO

VCCO

VSSO

VCCO

VSSO

VSSO

VSSO

VCCO

VSSO

VCCO

VCCO

VSSO

VSSO

VSS

VSS

VCC

VSSO

VSSO

VCCO

VCCO

VSSO

VCCO

VSSO

VSS

VSSO

VSSO

VCCO

VSSO

VCCO

VCCO

VSSO

VSSO

VSS

VSS

PQFP

PIN122 NO.

120

122

123

124

125

126

127

129

130

131

132

5

13

18

22

26

30

38

42

46

50

55

62

71

79

84

88

92

96

99

104

108

112

116

121

128

TQFP

PIN NO.

140

138

137

136

135

134

133

131

130

129

128

122

114

109

108

107

103

99

95

90

86

82

78

74

73

72

67

60

54

50

42

37

36

35

31

27

23

20

19

14

10

6

2

1

144

139

132

127

NOTE:

PINS

VCC

VCCO

COMMENTS

Supply internal logic. Connected to each other.

Supply output drivers only. Connected to each

other.

PINS

VSS

VSSO

COMMENTS

Supply internal logic. Connected to each other.

Supply output drivers only. Connected to each

other.

5

5 Page

512 x 36 x 2/1024 x 36 x 2 BiFIFOs

LH543611/21

OPERATIONAL DESCRIPTION

Reset

The device is reset whenever the asynchronous Reset

(RS) input is taken LOW, and at least one rising edge and

one falling edge of both CKA and CKB occur while RS is

LOW. A reset operation is required after power-up, before

the first write operation may occur. The LH543611/21 is

fully ready for operation after being reset. No device

programming is required if the default states described

below are acceptable.

A reset operation initializes the read-address and

write-address pointers for FIFO #1 and FIFO #2 to those

FIFO’s first physical memory locations. If the respective

outputs are enabled, the initial contents of these first

locations appear at the outputs. FIFO and mailbox status

flags are updated to indicate an empty condition. In

addition, the programmable-status-flag offset values are

initialized to eight. Thus, the AE1/AE2 flags get asserted

within eight locations of an empty condition, and the

AF1/AF2 flags likewise get asserted within eight locations

of a full condition, for FIFO #1/FIFO #2 respectively.

Bypass Operation

During reset (whenever RS is LOW) the device acts

as a registered transceiver, bypassing the internal FIFO

memories. Port A acts as the master port. A write or read

operation on Port A during reset transfers data directly to

or from Port B. Port B is considered to be the slave, and

cannot perform write or read operations independently on

its own during reset.

The direction of the bypass data transmission is deter-

mined by the R/WA control input, which does not get

overridden by the RS input. Here, a ‘write’ operation

means passing data from Port A to Port B, and a ‘read’

operation means passing data from Port B to Port A.

The bypass capability may be used to pass initializa-

tion or configuration data directly between a master proc-

essor and a peripheral device during reset.

Address Modes

Address pins select the device resource to be

accessed by each port. Port A has three resource-regis-

ter-select inputs, A0A,A1A, and A2A, which select between

FIFO access, mailbox-register access, control-register

access, and programmable flag-offset-value-register ac-

cess. Port B has a single address input, A0B, to select

between FIFO access or mailbox-register access.

The status of the resource-register-select inputs is

sampled at the rising edge of an enabled clock (CKA or

CKB). Resource-register select-input address definitions

are summarized in Table 1.

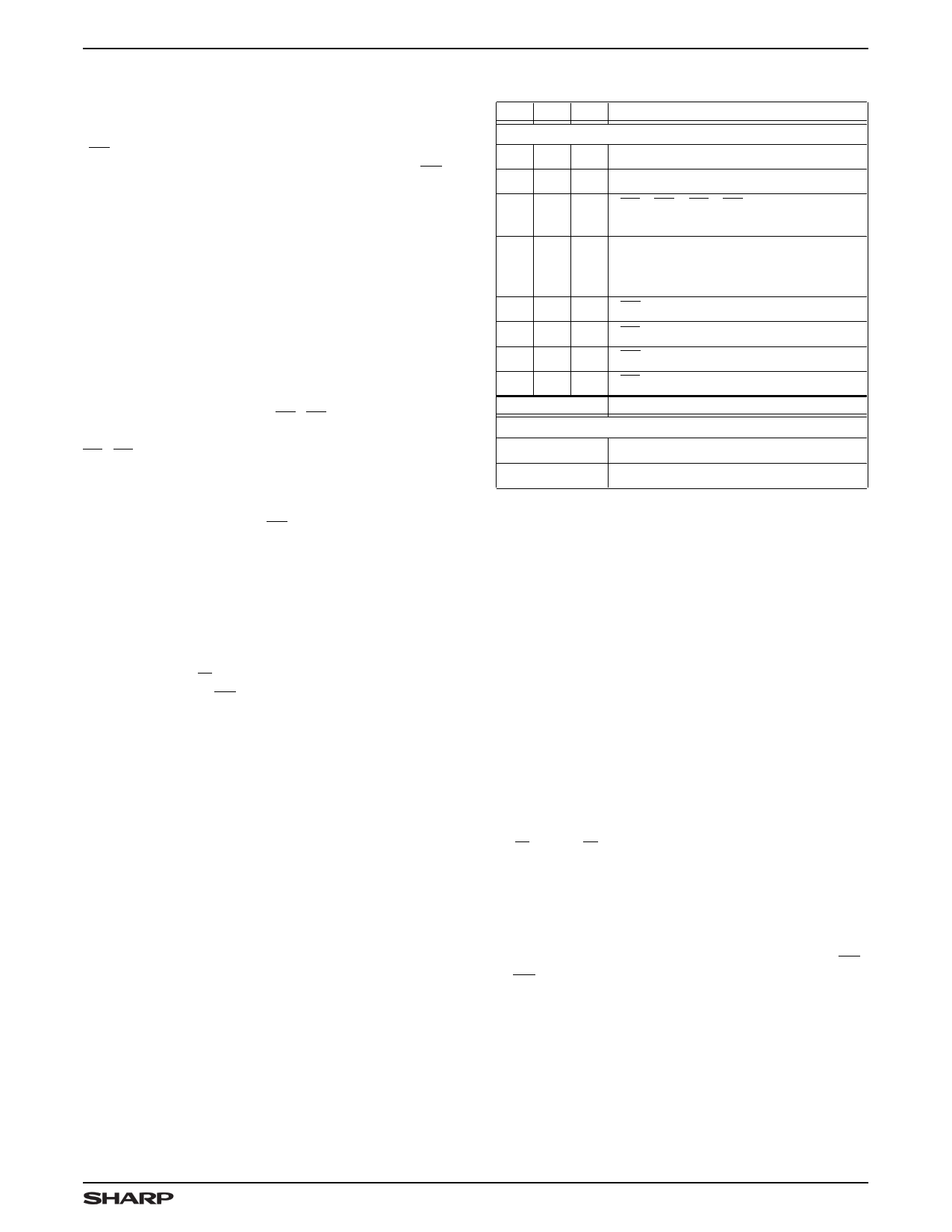

Table 1. Resource-Register Addresses

A2A A1A A0A

HHH

HHL

HLH

HLL

LHH

LHL

LLH

LLL

A0B

H

L

RESOURCE

PORT A

FIFO

Mailbox

AF2, AE2, AF1, AE1 Flag Offsets

Register (36-Bit Mode)

Control Register Flag-

Synchronization and Parity

Operating Mode

AE1 Flag Offset Register

AF1 Flag Offset Register

AE2 Flag Offset Register

AF2 Flag Offset Register

RESOURCE

PORT B

FIFO

Mailbox

Control Register

The eighteen Control-Register bits govern the syn-

chronization mode of the fullness-status flags at each

port, the choice of odd or even parity at both ports, the

enabling of parity generation for data flow at each port,

the optional latching behavior of the parity-error flags at

each port, and the selection of a full-word or half-word or

single-byte field for parity checking. A reset operation

initializes the LH543611/21 Control Register for

LH5420/LH543601-compatible operation, but it may be

reprogrammed at will at any time during LH543611/21

operation.

FIFO Write

Port A writes to FIFO #1, and Port B writes to FIFO #2.

A write operation is initiated on the rising edge of a clock

(CKA or CKB) whenever: the appropriate enable (ENA or

ENB) is held HIGH; the appropriate request (REQA or

REQB) is held HIGH; the appropriate Read/Write control

(R/WA or R/WB) is held LOW; the FIFO address is

selected for the address inputs (A2A – A0A or A0B); and

the prescribed setup times and hold times are observed

for all of these signals. Setup times and hold times must

also be observed on the data-bus pins (D0A – D35A or

D0B – D35B).

Normally, the appropriate Output Enable signal (OEA

or OEB) is HIGH, to disable the outputs at that port, so

that the data word present on the bus from external

sources gets stored. However, a ‘loopback’ mode of

operation also is possible, in which the data word supplied

by the outputs of one internal FIFO is ‘turned around’ at

the port and read back into the other FIFO. In this mode,

the outputs at the port are not disabled. To remain within

specification for all timing parameters, the Clock Cycle

Frequency must be reduced slightly below the value

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet LH543611.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LH543611 | 512 x 36 x 2 / 1024 x 36 x 2 Synchronous Bidirectional FIFO | Sharp Electrionic Components |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |