|

|

PDF KM68FV1000 Data sheet ( Hoja de datos )

| Número de pieza | KM68FV1000 | |

| Descripción | CMOS SRAM | |

| Fabricantes | Samsung Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de KM68FV1000 (archivo pdf) en la parte inferior de esta página. Total 11 Páginas | ||

|

No Preview Available !

KM68FV1000, KM68FS1000, KM68FR1000 Family

CMOS SRAM

Document Title

128K x8 bit Super Low Power and Low Voltage Full CMOS Static RAM

Revision History

Revision No. History

0.0 Initial draft

0.1

www.DataSheet4U.com

Revise

- Erase 100ns from KM68FS1000 Family

- Add 150ns for KM68FS1000 Family

- Add 32-sTSOP1 new package

- Add high power version

ISB1=5.0µA(Max)

- Change VDR(Min) 1.0 to 1.5V

1.0 Finalize

- Concept change high power version to low low power version

ISB1=5.0µA(Max)

- Change super low power version with special handling

ISB1=1.0µA(Max)

- Icc & Icc1(Read) decrease 10 to 5mA

2.0 Revise

- Change datasheet format

- Remove reverse type package from product

- Remove reserved speed bin(100ns)

3.0 Revise

- Add CSP type packaged product.

- Improved ICC2

Draft Date

March 15, 1996

July 7, 1996

Remark

Advance

Preliminary

December 1, 1996 Final

February 26, 1998 Final

July 29, 1998

Final

The attached datasheets are provided by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserves the right to change the specifications and

products. SAMSUNG Electronics will answer to your questions about device. If you have any questions, please contact the SAMSUNG branch offices.

1 Revision 3.0

July 1998

1 page

KM68FV1000, KM68FS1000, KM68FR1000 Family

CMOS SRAM

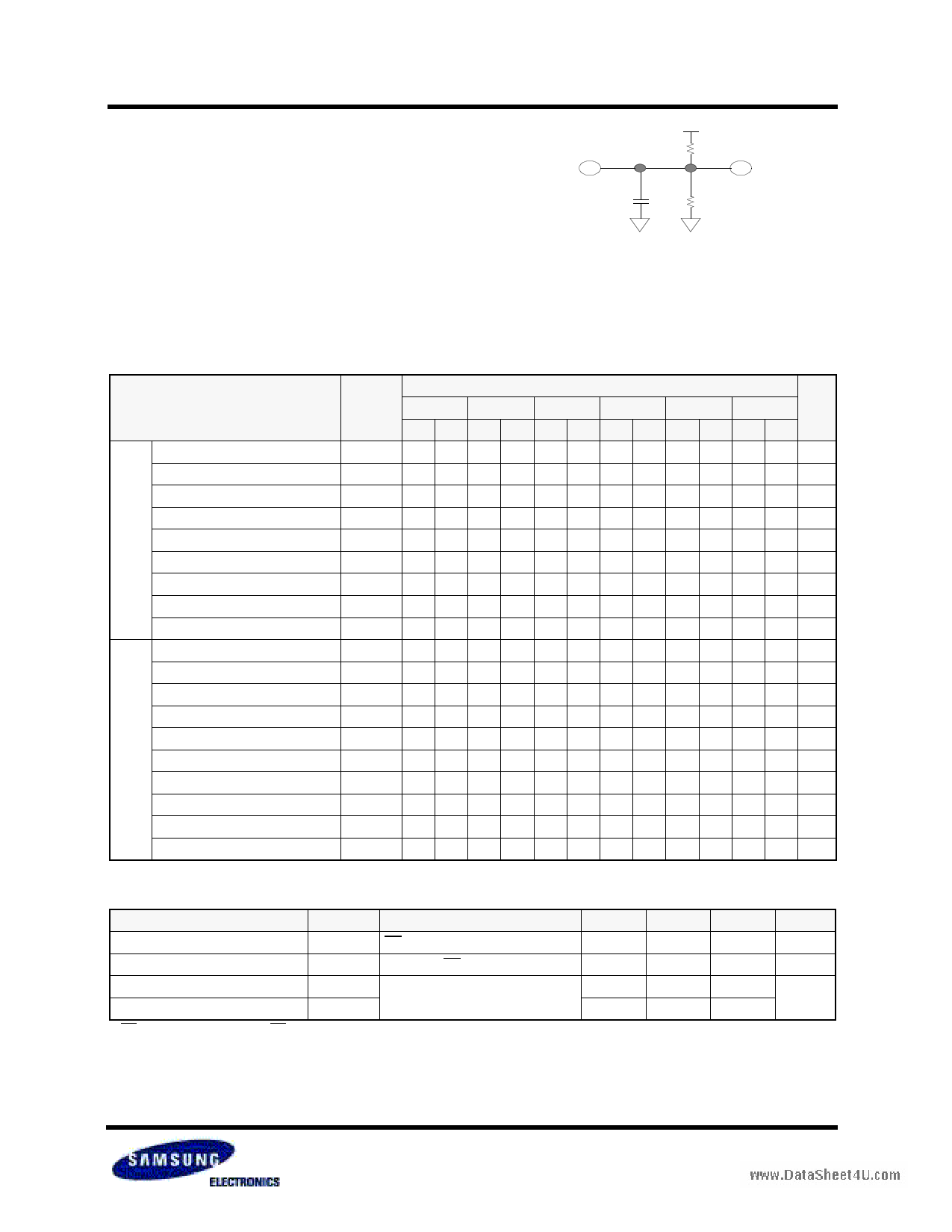

AC OPERATING CONDITIONS

TEST CONDITIONS (Test Load and Test Input/Output Reference)

Input pulse level : 0.4 to 2.2V for Vcc=3.3V, 3.0V, 2.5V

0.4 to 1.8V for Vcc=2.0V

Input rising and falling time : 5ns

Input and output reference voltage : 1.5V for Vcc=3.3V, 3.0V

1.1V for Vcc=2.5V

0.9V for Vcc=2.0V

Output load (See right) :CL=100pF+1TTL

CL=30pF+1TTL

VTM3)

R12)

CL1)

R22)

1. Including scope and jig capacitance

2. R1=3070Ω, R2=3150Ω

3. VTM =2.8V for VCC=3.0/3.3V

2.3V for VCC=2.5V

1.8V for VCC=2.0V

AC CHARACTERISTICS(Commercial product :TA=0 to 70°C, Industrial product : TA=-40 to 85°C

KM68FV1000 Family : Vcc=3.0~3.6V, KM68FS1000 Family : Vcc=2.3~3.3V,

www.DataSheet4U.com

KM68FR1000 Family : Vcc=1.8~2.7V)

Speed Bins

Parameter List

Symbol 70ns

85ns

100ns 120ns 150ns 300ns Units

Min Max Min Max Min Max Min Max Min Max Min Max

Read cycle time

tRC 70 - 85 - 100 - 120 - 150 - 300 - ns

Address access time

tAA - 70 - 85 - 100 - 120 - 150 - 300 ns

Chip select to output

tCO1, tCO2 - 70 - 85 - 100 - 120 - 150 - 300 ns

Output enable to valid output

Read Chip select to low-Z output

tOE - 35 - 45 - 50 - 60 - 75 - 150 ns

tLZ1, tLZ2 10 - 10 - 10 - 10 - 20 - 50 - ns

Output enable to low-Z output

tOLZ 5 - 5 - 5 - 5 - 10 - 30 - ns

Chip disable to high-Z output

tHZ1, tHZ2 0 25 0 25 0 30 0 35 0 40 0 60 ns

Output disable to high-Z output

tOHZ 0 25 0 25 0 30 0 35 0 40 0 60 ns

Output hold from address change tOH 10 - 15 - 15 - 15 - 15 - 30 - ns

Write cycle time

tWC 70 - 85 - 100 - 120 - 150 - 300 - ns

Chip select to end of write

tCW 65 - 70 - 80 - 100 - 120 - 300 - ns

Address set-up time

tAS 0 - 0 - 0 - 0 - 0 - 0 - ns

Address valid to end of write

tAW 65 - 70 - 80 - 100 - 120 - 300 - ns

Write pulse width

Write

Write recovery time

tWP 55 - 60 - 70 - 80 - 100 - 200 - ns

tWR 0 - 0 - 0 - 0 - 0 - 0 - ns

Write to output high-Z

tWHZ

0 25 0 25 0 30 0 35 0 40 0 60 ns

Data to write time overlap

tDW 30 - 35 - 40 - 50 - 60 - 120 - ns

Data hold from write time

tDH 0 - 0 - 0 - 0 - 0 - 0 - ns

End write to output low-Z

tOW 5 - 5 - 5 - 5 - 5 - 20 - ns

DATA RETENTION CHARACTERISTICS

Item

Symbol

Test Condition

Vcc for data retention

VDR CS1≥Vcc-0.2V1)

Data retention current

Data retention set-up time

Recovery time

IDR

tSDR

tRDR

Vcc=3.0V, CS1≥Vcc-0.2V1)

See data retention waveform

1. CS1≥Vcc-0.2V, CS2≥Vcc-0.2V(CS1 controlled) or CS2≤0.2V(CS2 controlled)

2. Super low power product = 1µA with special handling.

Min Typ Max Unit

1.5 - 3.6 V

-

-

5.02)

µA

0-

tRC -

-

ns

-

5 Revision 3.0

July 1998

5 Page

KM68FV1000, KM68FS1000, KM68FR1000 Family

CMOS SRAM

PACKAGE DIMENSIONS

32 PIN THIN SMALL OUTLINE PACKAGE TYPE I (0820F)

Top View

Units: millimeter(inch)

Bottom View

Ball #A1

B

www.DataSheet4U.com

Ball #A1

B

654321

A

B

C

D

E

F

G

H

B1

B/2 SRAM Die

Elastomer

Side View

D

Detail A

B/2

Detail A

A

Y

C

Min Typ Max

A - 0.75 -

B 5.90 6.00 6.10

B1 - 3.75 -

C 7.90 8.00 8.10

C1 - 5.25 -

D 0.30 0.35 0.40

E - 0.80 0.81

E1 - 0.55 -

E2 - 0.25 -

Y-

- 0.08

Elastomer

Die

0.3/Typ.

Notes.

1. Bump counts : 48(8row x 6column)

2. Bump pitch : (x,y)=(0.75 x 0.75)(typ.)

3. All tolerence are +/-0.050 unless

otherwise specified.

4. Typ : Typical

5. Y is coplanarity: 0.08(Max)

11 Revision 3.0

July 1998

11 Page | ||

| Páginas | Total 11 Páginas | |

| PDF Descargar | [ Datasheet KM68FV1000.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KM68FV1000 | CMOS SRAM | Samsung Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |