|

|

PDF LH5164AVH Data sheet ( Hoja de datos )

| Número de pieza | LH5164AVH | |

| Descripción | CMOS 64K (8K x 8) Static RAM | |

| Fabricantes | Sharp Electrionic Components | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LH5164AVH (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

LH5164AVH

CMOS 64K (8K × 8) Static RAM

FEATURES

• 8,192 × 8 bit organization

• Access time: 200 ns (MAX.)

• Supply current (MAX.):

Operating: 90 mW

29 mW (tRC, tWC = 1 µs)

Standby: 3.6 µW (MAX.) @ 70°C

10.8 µW (MAX.) @ 85°C

Data retention:

0.6 µW (VCC = 3 V, tA = 25°C)

• Low voltage operation: 3.3 V ±0.3 V

• Fully-static operation

• TTL compatible I/O

• Three-state outputs

• Packages:

28-pin, 450-mil SOP

28-pin, 8 × 13 mm2 TSOP (Type I)

DESCRIPTION

The LH5164AVH is a static RAM organized as

8,192 × 8 bits. It is fabricated using silicon-gate CMOS

process technology.

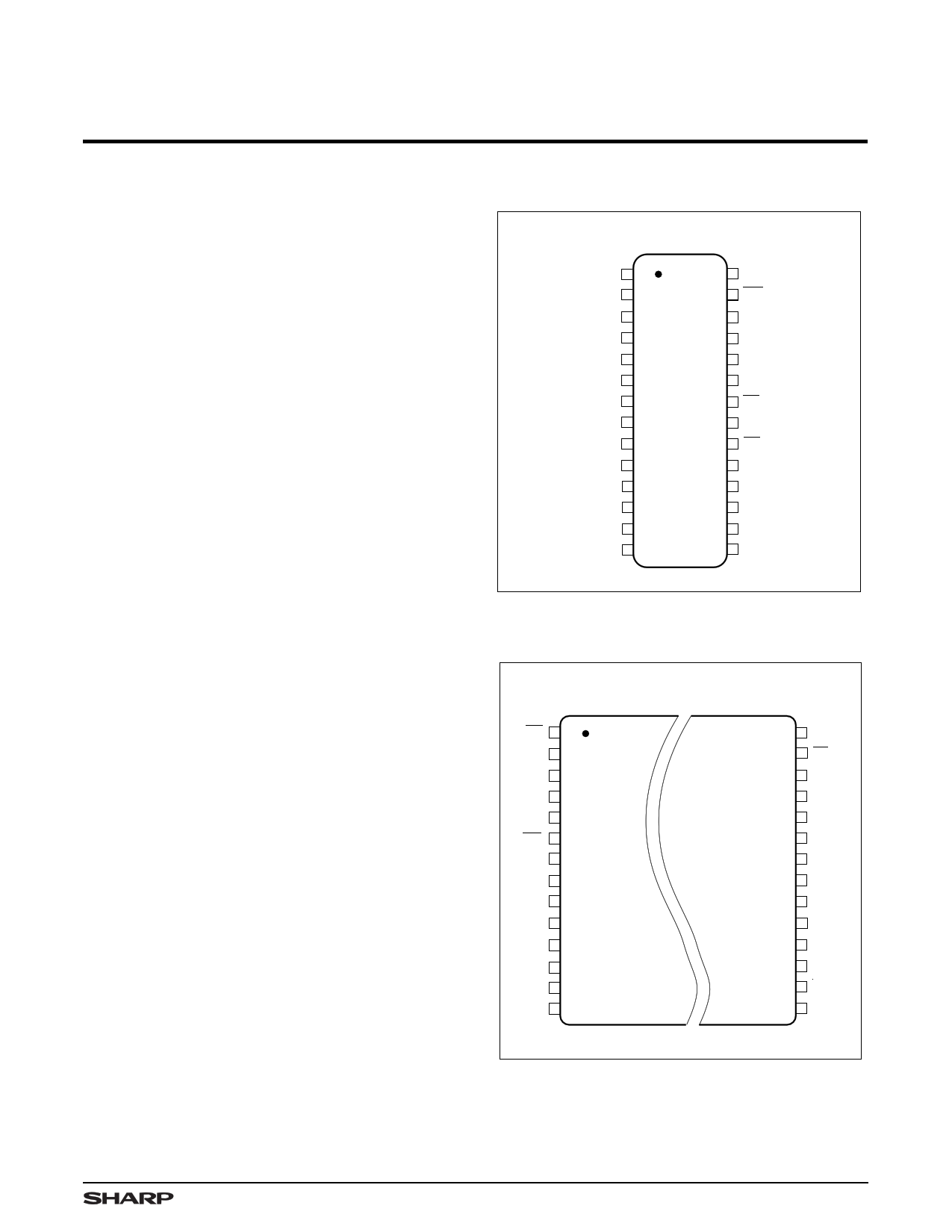

PIN CONNECTIONS

28-PIN SOP

TOP VIEW

NC

A12

A7

A6

A5

A4

A3

A2

A1

A0

I/O1

I/O2

I/O3

GND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 VCC

27 WE

26 CE2

25 A8

24 A9

23 A11

22 OE

21 A10

20 CE1

19 I/O8

18 I/O7

17 I/O6

16 I/O5

15 I/O4

5164AVH-1

Figure 1. Pin Connections for SOP Package

28-PIN TSOP (Type I)

TOP VIEW

OE

A11

A9

A8

CE2

WE

VCC

NC

A12

A7

A6

A5

A4

A3

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 A10

27 CE1

26 I/O8

25 I/O7

24 I/O6

23 I/O5

22 I/O4

21 GND

20 I/O3

19 I/O2

18 I/O1

17 A0

16 A1

15 A2

5164AVH-2

Figure 2. Pin Connections for TSOP Package

1

1 page

CMOS 64K (8K × 8) Static RAM

LH5164AVH

DATA RETENTION CHARACTERISTICS (TA = –40°C to +85°C)

PARAMETER

SYMBOL

CONDITIONS

MIN.

Data retention supply voltage

Data retention supply current

VCCDR

ICCDR

CE2 ≤ 0.2 V or

CE1 ≥ VCCDR – 0.2 V

VCCDR = 3 V,

CE2 ≤ 0.2 V or

CE1 ≥ VCCDR – 0.2 V

TA =

25°C

TA =

70°C

2.0

Chip disable to data retention

tCDR

Recovery time

tR

NOTES:

1. CE2 should be ≥ VCCDR – 0.2 V or ≤ 0.2 V.

2. tRC = Read cycle time.

0

tRC

MAX.

0.2

0.6

1.5

UNIT

V

µA

µA

µA

ns

ns

NOTE

1

1

2

CE1 CONTROL (NOTE)

VCC

3.0 V

CE1

VCC - 0.5 V

VCCDR

0V

CE2 CONTROL

VCC

CE2

3.0 V

tCDR

tCDR

DATA RETENTION MODE

tR

CE1 ≥ VCCDR - 0.2 V

DATA RETENTION MODE

tR

VCCDR

0.2 V

0V

CE2 ≤ 0.2 V

NOTE: To control the data retention mode at CE1, fix the input level of CE2 between

VCCDR to VCCDR - 0.2 V or 0 V and 0.2 V during the data retention mode.

Figure 4. Data Retention Characteristics

5164AVH-7

5

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet LH5164AVH.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LH5164AV | CMOS 64K (8K x 8) Static RAM | Sharp Electrionic Components |

| LH5164AVH | CMOS 64K (8K x 8) Static RAM | Sharp Electrionic Components |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |