|

|

PDF S29NS-P Data sheet ( Hoja de datos )

| Número de pieza | S29NS-P | |

| Descripción | MirrorBit Flash Family | |

| Fabricantes | SPANSION | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de S29NS-P (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

S29NS-P MirrorBitTM Flash Family

www.DataSheetS4U2.c9omNS512P S29NS256P S29NS128P

512/256/128 Mb (32/16/8 M x 16 bit), 1.8 V Burst Simultaneous

Read/Write, Multiplexed MirrorBit Flash Memory

Data Sheet (Advance Information)

S29NS-P MirrorBitTM Flash Family Cover Sheet

Notice to Readers: This document states the current technical specifications regarding the Spansion

product(s) described herein. Each product described herein may be designated as Advance Information,

Preliminary, or Full Production. See Notice On Data Sheet Designations for definitions.

Publication Number S29NS-P_00

Revision A Amendment 1

Issue Date February 20, 2007

1 page

Data Sheet (Advance Information)

Figures

www.DataSheet4U.com

Figure 3.1 Simultaneous Operation Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 4.1 64-Ball Very Thin Fine-Pitch Ball Grid Array, S29NS512P Top View, Balls Facing Down . . 10

Figure 4.2 44-Ball Very Thin Fine-Pitch Ball Grid Array, S29NS256P Top View, Balls Facing Down . . 11

Figure 4.3 44-Ball Very Thin Fine-Pitch Ball Grid Array, S29NS128P Top View, Balls Facing Down . . 11

Figure 4.4 VDD064—64-Ball Very Thin Fine-Pitch Ball Grid Array, S29NS512P. . . . . . . . . . . . . . . . . . 12

Figure 4.5 VDE044—44-Ball Very Thin Fine-Pitch Ball Grid Array, S29NS128/256P . . . . . . . . . . . . . . 13

Figure 6.1 Synchronous Read Flow Chart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 6.2 Single Word Program. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 6.3 Write Buffer Programming Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 6.4 Sector Erase Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 6.5 Write Operation Status Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 7.1 Advanced Sector Protection/Unprotection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 7.2 PPB Program/Erase Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 7.3 Lock Register Program Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 10.1 Maximum Negative Overshoot Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 10.2 Maximum Positive Overshoot Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Figure 10.3 Test Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 10.4 Input Waveforms and Measurement Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 10.5 VCC Power-Up Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 10.6 CLK Characterization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 10.7 8-Word Linear Synchronous Single Data Rate Burst with Wrap Around . . . . . . . . . . . . . . . . 68

Figure 10.8 8-Word Linear Single Data Read Synchronous Burst without Wrap Around . . . . . . . . . . . . . 69

Figure 10.9 Asynchronous Mode Read with Latched Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 10.10 Asynchronous Mode Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Figure 10.11 Reset Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 10.12 Asynchronous Program Operation Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 10.13 Chip/Sector Erase Command Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 10.14 Accelerated Unlock Bypass Programming Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 10.15 Data# Polling Timings (During Embedded Algorithm) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 10.16 Toggle Bit Timings (During Embedded Algorithm). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Figure 10.17 Synchronous Data Polling Timings/Toggle Bit Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 10.18 DQ2 vs. DQ6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 10.19 Latency with Boundary Crossing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Figure 10.20 Wait State Configuration Register Setup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 10.21 Back-to-Back Read/Write Cycle Timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

February 20, 2007 S29NS-P_00_A1

S29NS-P MirrorBitTM Flash Family

5

5 Page

Data Sheet (Advance Information)

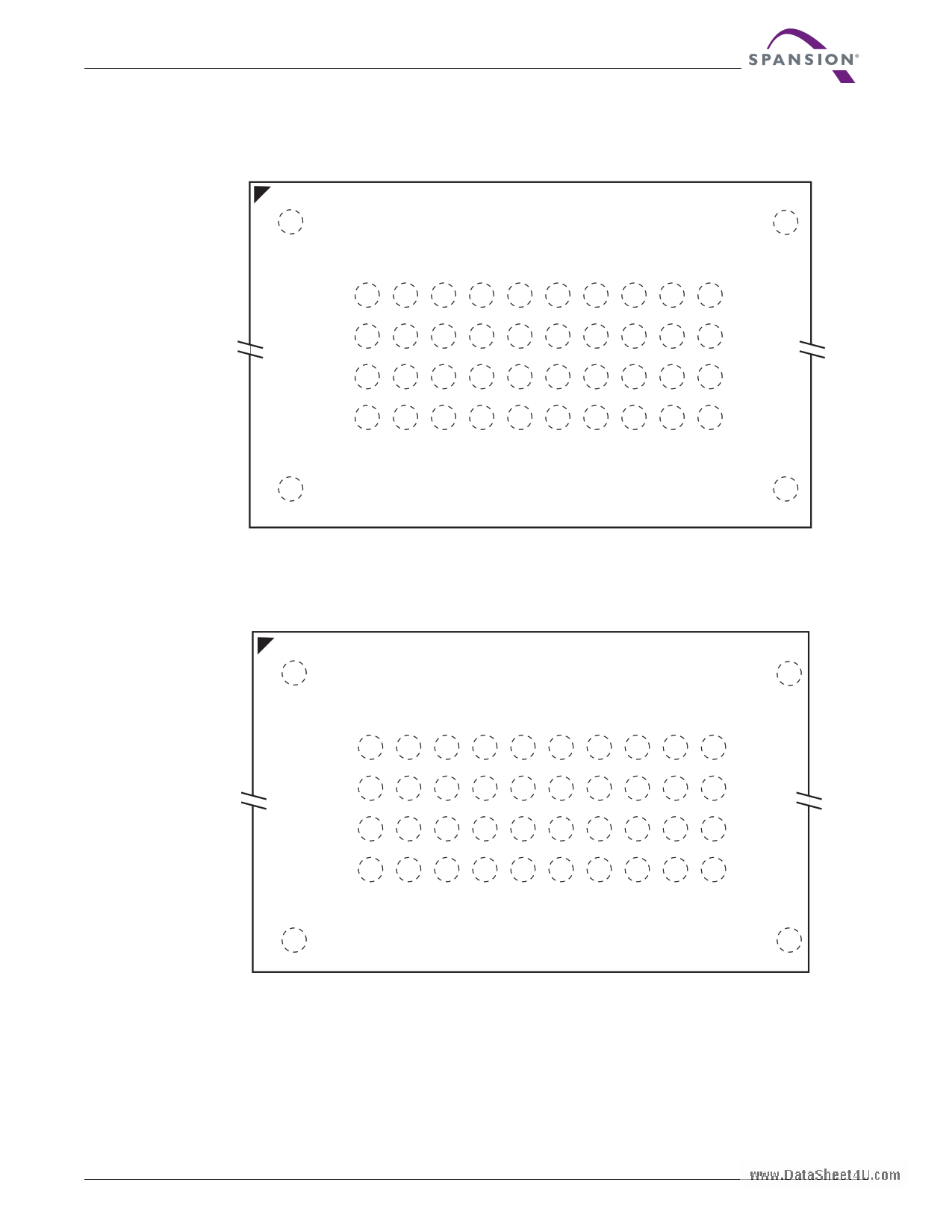

44-Ball Very Thin Fine-Pitch Ball Grid Array, S29NS256P

Figure 4.2 44-Ball Very Thin Fine-Pitch Ball Grid Array, S29NS256P Top View, Balls Facing Down

www.DataSheet4U.com

NC

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10

RDY A21 VSS CLK VCC WE# VPP A19 A17 A22

B1 B2 B3 B4 B5 B6 B7 B8 B9 B10

VCCQ

A16

A20 AVD# A23 RESET# WP#

A18

CE#

VSSQ

C1 C2 C3 C4 C5 C6 C7 C8 C9 C10

VSS A/DQ7 A/DQ6 A/DQ13 A/DQ12 A/DQ3 A/DQ2 A/DQ9 A/DQ8 OE#

D1 D2 D3 D4 D5 D6 D7 D8 D9 D10

A/DQ15 A/DQ14 VSSQ A/DQ5 A/DQ4 A/DQ11 A/DQ10 VCCQ A/DQ1 A/DQ0

NC

NC NC

44-Ball Very Thin Fine-Pitch Ball Grid Array, S29NS128P

Figure 4.3 44-Ball Very Thin Fine-Pitch Ball Grid Array, S29NS128P Top View, Balls Facing Down

NC

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10

RDY A21 VSS CLK VCC WE# VPP A19 A17 A22

B1 B2 B3 B4 B5 B6 B7 B8 B9 B10

VCCQ

A16

A20 AVD# NC RESET# WP#

A18

CE#

VSSQ

C1 C2 C3 C4 C5 C6 C7 C8 C9 C10

VSS A/DQ7 A/DQ6 A/DQ13 A/DQ12 A/DQ3 A/DQ2 A/DQ9 A/DQ8 OE#

D1 D2 D3 D4 D5 D6 D7 D8 D9 D10

A/DQ15 A/DQ14 VSSQ A/DQ5 A/DQ4 A/DQ11 A/DQ10 VCCQ A/DQ1 A/DQ0

NC

NC NC

February 20, 2007 S29NS-P_00_A1

S29NS-P MirrorBitTM Flash Family

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S29NS-P.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S29NS-J | Burst Mode Flash Memories | SPANSION |

| S29NS-N | Burst Mode Flash Memory | SPANSION |

| S29NS-P | MirrorBit Flash Family | SPANSION |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |